設計IP需要考慮如下因素:

1)基于 IBTA 1.5 協議規范,支持 RoCE v2 標準協議傳輸,同時支持 ARP協議和 ICMP 協議。

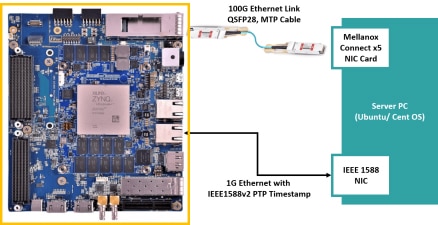

2)基于 Xilinx CMAC 集成塊進行開發并獨立設計 UDP/IP 協議棧。一方面,CMAC 集成塊具有多種版本,并且適用平臺多,因此本數據傳輸系統能夠部署在支持 CMAC 集成塊的 FPGA 開發板上。另一方面,獨立設計 UDP/IP 協議棧能夠讓本設計具有更高的數據傳輸性能并進一步降低資源占用。

3)采用純邏輯電路開發。設計基于純邏輯電路,可以脫離 MCU 控制獨立運行,兼容 SoC 環境與純邏輯環境。

4)使用標準 AXI 總線接口,設計使用標準化的 AXI4 及 AXI-Stream 總線接口進行數據傳輸,同時使用標準化的 AXI-Lite 總線接口提供系統控制功能,在保證傳輸性能的同時,使得本設計更容易集成到應用、生產環境中。

5)多隊列并行管理及控制。支持系統運行過程中進行創建隊列、刪除隊列、隊列更改等操作。

6)DMA 傳輸。通過配置 DMA 寄存器實現直接的數據傳輸請求,同時使用突發傳輸來提高數據傳輸性能。

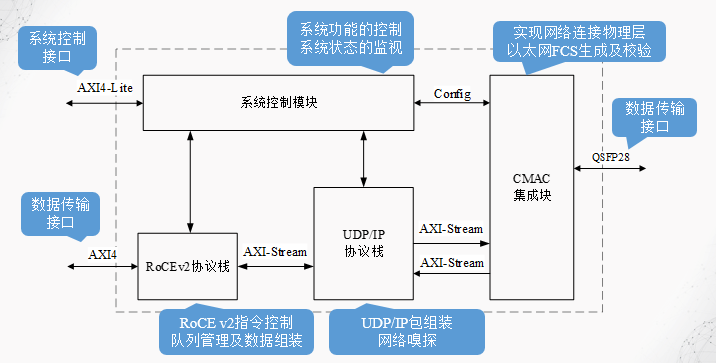

IP框架

這里重點討論PC與FPGA之間采用RDMA RoCE v2 高速數據傳輸,FPGA與FPGA后面介紹。該IP系統的整體架構如圖 1 所示。它通過 QSFP28 接口連接上位機進行數據傳輸;通過AXI-Lite 接口進行系統控制;AXI4 接口進行數據傳輸。在系統內部,根據功能劃分為系統控制模塊、融合以太網協議棧、以太網協議棧和 CMAC 集成塊。以下為各功能模塊的定義。

圖1 RDMA over RoCE V2 IP框圖

該IP控制模塊是實現系統功能控制的核心模塊。RoCE v2 高速數據傳輸系統內部集成了多種功能,包括 RDMA 建鏈、RDMA 隊列管理、DMA 傳輸和系統監控等。

這些功能均由系統控制模塊進行管理。為了對這些功能進行高效的管理,系統控制模塊設計了對應的功能控制單元及相應的寄存器,并將這些寄存器抽象為 AXI-Lite 從機端接口,使得本數據傳輸系統可以簡易地集成進用戶環境。同時通過 AXI-Lite 接口,用戶可以高效的與本數據傳輸系統進行交互,實現對系統功能的控制,而不必了解本IP的底層工作邏輯。

融合以太網協議棧是實現 RoCE v2 命令提交和完成機制的核心模塊,完成網絡層級中網絡層及應用層功能。該模塊負責將來自系統控制模塊的功能請求轉換為RoCE v2 指令,如建鏈、斷鏈、數據傳輸,并執行指令提交及完成機制。此外,該模塊還實現了 RDMA 隊列管理功能,包括隊列存儲、隊列創建及刪除、隊列仲裁等功能。同時,本模塊也負責控制 DMA 數據讀寫,將數據讀寫請求轉換為 AXI4 總線事務,通過 AXI4 總線接口讀寫數據,并負責 RoCE v2 網絡包的封裝、解析、不變循環冗余校驗(ICRC)生成等功能。

以太網協議棧模塊負責解析及組裝網絡包,完成網絡層級中傳輸層、網絡層及網絡接口層功能。首先,該模塊接收來自融合以太網協議棧的網絡包,并為其逐層添加UDP、IP 及 ETH 頭部,使其成為完整的網絡包后發送至 CMAC 集成塊。其次,該模塊解析來自遠程主機的 ARP 或 ICMP 網絡包,用以實現網絡嗅探功能。最后,該模塊負責接收 CMAC 集成塊傳輸過來的網絡包,并對其進行解包和解析,而后根據包的功能分發到相應模塊或子模塊。最后,該模塊還實現了網絡擁塞處理及流量控制機

制,如 ECN 協議或 PFC 協議。

B站已給出相關性能的視頻,如想進一步了解,請搜索B站用戶:專注與守望

鏈接:https://space.bilibili.com/585132944/dynamic?spm_id_from=333.1365.list.card_title.click

審核編輯 黃宇

-

FPGA

+關注

關注

1645文章

22050瀏覽量

618693 -

RDMA

+關注

關注

0文章

85瀏覽量

9299

發布評論請先 登錄

RDMA over RoCE V2設計2:ip 整體框架設計考慮

RDMA over RoCE V2設計1:為什么要設計它?

RDMA over RoCE V2設計1:通用,穩定及高性能!

RDMA簡介7之可靠傳輸

RDMA簡介6之RoCEV2連接管理

RDMA簡介5之RoCE V2隊列分析

RDMA簡介4之ROcE V2初析

RDMA簡介3之四種子協議對比

RDMA簡介2之A技術優勢分析

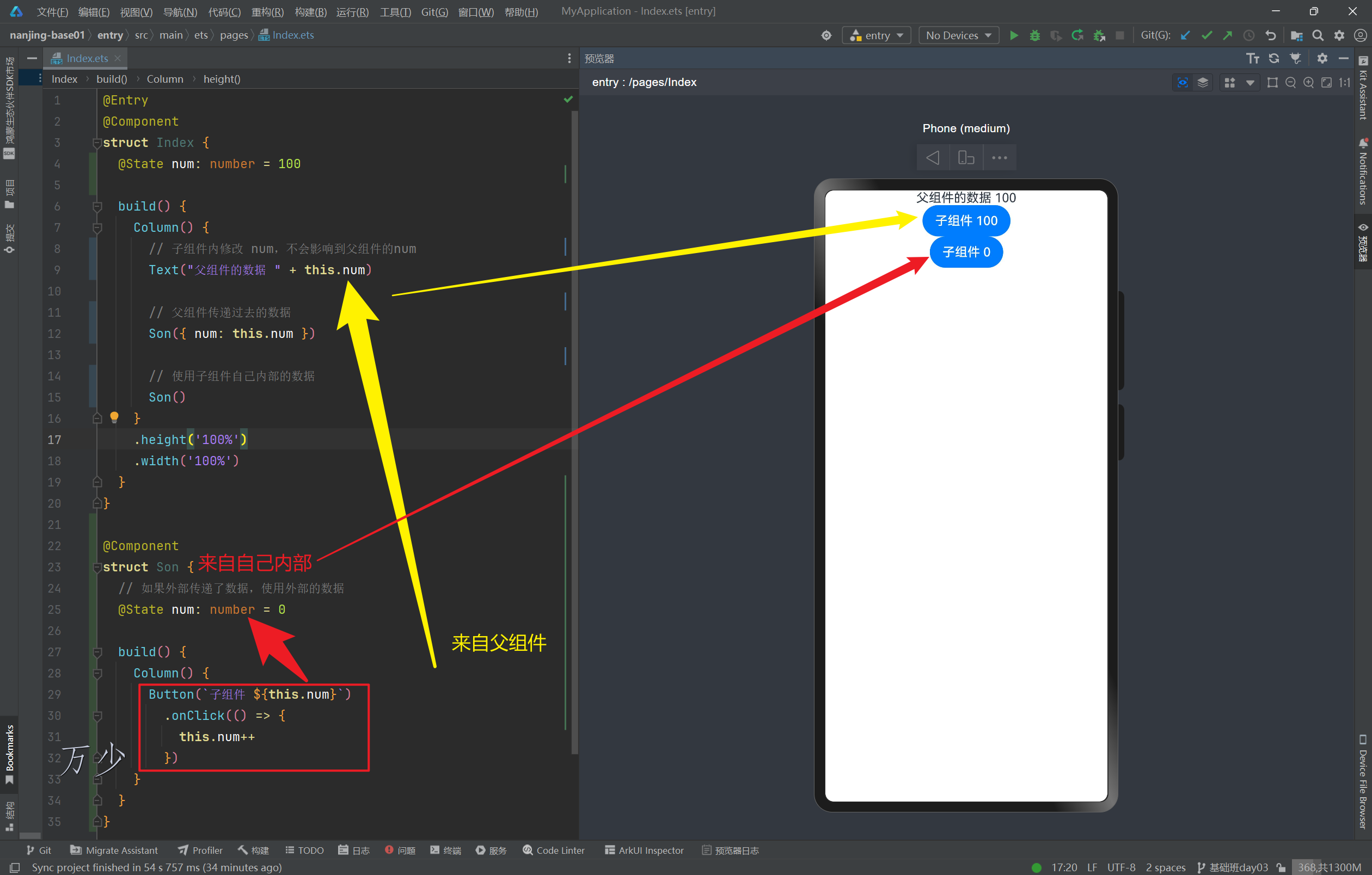

HarmonyOS Next V2 @Local 和@Param

HarmonyOS Next V2 @Monitor 和@Computed

加速網絡性能:融合以太網 RDMA (RoCE) 的影響

RoCE與IB對比分析(一):協議棧層級篇

RDMA over RoCE V2設計2:ip 整體設計考慮

RDMA over RoCE V2設計2:ip 整體設計考慮

評論