超大規(guī)模集成電路(Very Large Scale Integration Circuit,VLSI)是一種將大量晶體管組合到單一芯片的集成電路,其集成度大于大規(guī)模集成電路。集成的晶體管數(shù)在不同的標(biāo)準(zhǔn)中有所不同。從1970年代開始,隨著復(fù)雜的半導(dǎo)體以及通信技術(shù)的發(fā)展,集成電路的研究、發(fā)展也逐步展開。計(jì)算機(jī)里的控制核心微處理器就是超大規(guī)模集成電路的最典型實(shí)例,超大規(guī)模集成電路設(shè)計(jì)(VLSI design),尤其是數(shù)字集成電路,通常采用電子設(shè)計(jì)自動(dòng)化的方式進(jìn)行,已經(jīng)成為計(jì)算機(jī)工程的重要分支之一。

超大規(guī)模集成電路(Very Large Scale Integrated circuits:VLSI)

在一塊芯片上集成的元件數(shù)超過10萬個(gè),或門電路數(shù)超過萬門的集成電路,稱為超大規(guī)模集成電路。超大規(guī)模集成電路是20世紀(jì)70年代后期研制成功的,主要用于制造存儲(chǔ)器和微處理機(jī)。64k位隨機(jī)存取存儲(chǔ)器是第一代超大規(guī)模集成電路,大約包含15萬個(gè)元件,線寬為3微米。

超大規(guī)模集成電路的集成度已達(dá)到600萬個(gè)晶體管,線寬達(dá)到0.3微米。用超大規(guī)模集成電路制造的電子設(shè)備,體積小、重量輕、功耗低、可靠性高。利用超大規(guī)模集成電路技術(shù)可以將一個(gè)電子分系統(tǒng)乃至整個(gè)電子系統(tǒng)“集成”在一塊芯片上,完成信息采集、處理、存儲(chǔ)等多種功能。例如,可以將整個(gè)386微處理機(jī)電路集成在一塊芯片上,集成度達(dá)250萬個(gè)晶體管。超大規(guī)模集成電路研制成功,是微電子技術(shù)的一次飛躍,大大推動(dòng)了電子技術(shù)的進(jìn)步,從而帶動(dòng)了軍事技術(shù)和民用技術(shù)的發(fā)展。超大規(guī)模集成電路已成為衡量一個(gè)國家科學(xué)技術(shù)和工業(yè)發(fā)展水平的重要標(biāo)志,也是世界主要工業(yè)國家,特別是美國和日本競爭最激烈的一個(gè)領(lǐng)域。

發(fā)展現(xiàn)狀

數(shù)十億級別的晶體管處理器已經(jīng)得到商用。隨著半導(dǎo)體制造工藝從32納米水平躍升到下一步22納米,這種集成電路會(huì)更加普遍,盡管會(huì)遇到諸如工藝角偏差之類的挑戰(zhàn)。值得注意的例子是英偉達(dá)的GeForce 700系列的首款顯示核心,代號‘GK110’的圖形處理器,采用了全部71億個(gè)晶體管來處理數(shù)字邏輯。而Itanium的大多數(shù)晶體管是用來構(gòu)成其3千兩百萬字節(jié)的三級緩存。Intel Core i7處理器的芯片集成度達(dá)到了14億個(gè)晶體管。所采用的設(shè)計(jì)與早期不同的是它廣泛應(yīng)用電子設(shè)計(jì)自動(dòng)化工具,設(shè)計(jì)人員可以把大部分精力放在電路邏輯功能的硬件描述語言表達(dá)形式,而功能驗(yàn)證、邏輯仿真、邏輯綜合、布局、布線、版圖等可以由計(jì)算機(jī)輔助完成。

不足

由于技術(shù)規(guī)模不斷擴(kuò)大,微處理器的復(fù)雜程度也不斷提高,微處理器的設(shè)計(jì)者已經(jīng)遇到了若干挑戰(zhàn)。

功耗、散熱:隨著元件集成規(guī)模的提升,單位體積產(chǎn)生的熱功率也逐漸變大,然而器件散熱面積不變,造成單位面積的熱耗散達(dá)不到要求。同時(shí),單個(gè)晶體管微弱亞閾值電流造成的靜態(tài)功耗由于晶體管數(shù)量的大幅增加而變得日益顯著。人們提出了一些低功耗設(shè)計(jì)技術(shù),例如動(dòng)態(tài)電壓/頻率調(diào)節(jié)(dynamic voltage and frequency scaling (DVFS)),來降低耗散總功率。

工藝偏差:由于光刻技術(shù)受限于光學(xué)規(guī)律,更高精確度的摻雜以及刻蝕會(huì)變得更加困難,造成誤差的可能性會(huì)變大。設(shè)計(jì)者必須在芯片制造前進(jìn)行技術(shù)仿真。

更嚴(yán)格的設(shè)計(jì)規(guī)律:由于光刻和刻蝕工藝的問題,集成電路布局的設(shè)計(jì)規(guī)則必須更加嚴(yán)格。在設(shè)計(jì)布局時(shí),設(shè)計(jì)者必須時(shí)刻考慮這些規(guī)則。定制設(shè)計(jì)的總開銷已經(jīng)達(dá)到了一個(gè)臨界點(diǎn),許多設(shè)計(jì)機(jī)構(gòu)都傾向于始于電子設(shè)計(jì)自動(dòng)化來實(shí)現(xiàn)自動(dòng)設(shè)計(jì)。

設(shè)計(jì)收斂:由于數(shù)字電子應(yīng)用的時(shí)鐘頻率趨于上升,設(shè)計(jì)者發(fā)現(xiàn)要在整個(gè)芯片上保持低時(shí)鐘偏移更加困難。這引發(fā)了對于多核心、多處理器架構(gòu)的興趣(參見阿姆達(dá)爾定律)。

成本:隨著晶粒尺寸的縮小,晶圓尺寸變大,單位晶圓面積上的晶粒數(shù)增加,這樣制造工藝所用到的光掩模的復(fù)雜程度就急劇上升。現(xiàn)代高精度的光掩模技術(shù)十分昂貴。

-

芯片

+關(guān)注

關(guān)注

459文章

51927瀏覽量

433655 -

集成電路

+關(guān)注

關(guān)注

5415文章

11865瀏覽量

366265 -

晶體管

+關(guān)注

關(guān)注

77文章

9909瀏覽量

140187

原文標(biāo)題:超大規(guī)模集成電路

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

電子管與晶體管在結(jié)構(gòu)和應(yīng)用上的區(qū)別

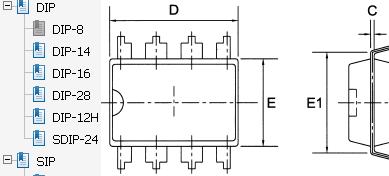

一文解讀集成電路的組成及封裝形式

關(guān)于ULN2003達(dá)林頓晶體管集成電路的知識(shí)匯總

什么是晶體管 晶體管的分類及主要參數(shù)

鰭式場效晶體管集成電路設(shè)計(jì)與測試

一種將大量晶體管組合到單一芯片的集成電路

一種將大量晶體管組合到單一芯片的集成電路

評論