聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1646文章

22054瀏覽量

618791 -

Altera

+關(guān)注

關(guān)注

37文章

805瀏覽量

156087 -

數(shù)碼管

+關(guān)注

關(guān)注

32文章

1889瀏覽量

92653 -

DIY

+關(guān)注

關(guān)注

176文章

894瀏覽量

353389

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

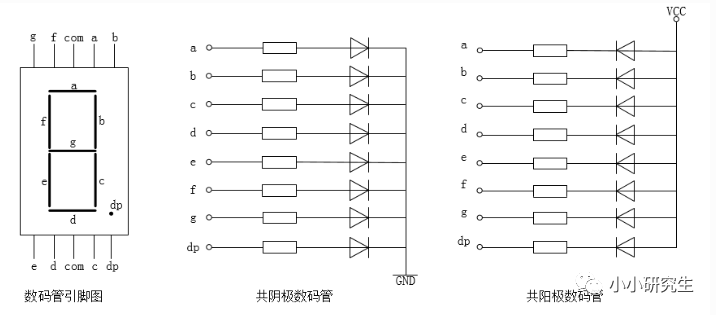

什么是數(shù)碼管靜態(tài)顯示

注意:本實(shí)驗(yàn)采用清翔電子51單片機(jī)開發(fā)板(同樣的51單片機(jī)開發(fā)板,不同型號(hào),內(nèi)部設(shè)計(jì)會(huì)有一定差異,程序不一定適用)1、數(shù)碼管知識(shí)a圖為一個(gè)數(shù)碼管

發(fā)表于 07-06 07:28

由FPGA DIY開發(fā)板控制實(shí)現(xiàn)數(shù)碼管靜態(tài)顯示1-F

使用靜態(tài)掃描方式,數(shù)碼管循環(huán)顯示1-F。8個(gè)數(shù)字顯示相同內(nèi)容。

利用FPGA DIY開發(fā)板實(shí)現(xiàn)撥碼開關(guān)控制靜態(tài)數(shù)碼管顯示

FPGA diy作業(yè)實(shí)現(xiàn)撥碼開關(guān)控制顯示數(shù)碼管0到8的靜態(tài)

采用FPGA DIY開發(fā)板實(shí)現(xiàn)數(shù)碼管動(dòng)態(tài)顯示60計(jì)數(shù)

asean的 FPGA DIY 數(shù)碼管動(dòng)態(tài)顯示60計(jì)數(shù)視頻

利用FPGA DIY開發(fā)板控制數(shù)碼管實(shí)現(xiàn)0至9循環(huán)顯示

asean的 FPGA DIY 數(shù)碼管實(shí)現(xiàn)0至9循環(huán)顯示視頻

采用FPGA DIY開發(fā)板實(shí)現(xiàn)8個(gè)數(shù)碼管的滾動(dòng)顯示

實(shí)現(xiàn)8個(gè)數(shù)碼管的滾動(dòng)顯示,即第1個(gè)顯示1,時(shí)間1s,然后關(guān)閉;接著然后第2

采用FPGA DIY 開發(fā)板實(shí)現(xiàn)數(shù)碼管靜態(tài)顯示

8個(gè)數(shù)碼管靜態(tài)顯示數(shù)字,并從0計(jì)數(shù)到f

通過(guò)FPGA DIY開發(fā)板實(shí)現(xiàn)數(shù)碼管動(dòng)態(tài)顯示

8個(gè)數(shù)碼管動(dòng)態(tài)顯示數(shù)字,數(shù)碼管依次顯示數(shù)字0~7

FPGA入門系列實(shí)驗(yàn)教程之實(shí)現(xiàn)數(shù)碼管靜態(tài)顯示的詳細(xì)資料說(shuō)明

實(shí)現(xiàn)開發(fā)板上的數(shù)碼管靜態(tài)循環(huán)顯示 0~F。通過(guò)這個(gè)實(shí)驗(yàn),掌握采用 VerilogHDL 語(yǔ)言編

發(fā)表于 06-12 15:59

?19次下載

采用FPGA DIY開發(fā)板實(shí)現(xiàn)8個(gè)靜態(tài)的數(shù)碼管顯示

采用FPGA DIY開發(fā)板實(shí)現(xiàn)8個(gè)靜態(tài)的數(shù)碼管顯示

評(píng)論