我知道,我對與電子有關的所有事情都很著迷,但不論從哪個角度看,今天的現場可編程門陣列(FPGA),都顯得“鶴立雞群”,真是非常棒的器件。如果在這個智能時代,在這個領域,想擁有一技之長的你還沒有關注FPGA,那么世界將拋棄你,時代將拋棄你。

前面的文章我們介紹了關于FFT的硬件實現。關于FFT的逆運算IFFT,其實就是將實現FFT的過程反過來執行就可以了。

在實現過程中要注意很多問題。

同 FFT一樣,效率問題。以2048點為例,根據理論值計算,計算一次2048點的IFFT的時間應為130us。在采用流水線的方式下,實部計算和虛部計算均采用兩塊RAM實現流水線。

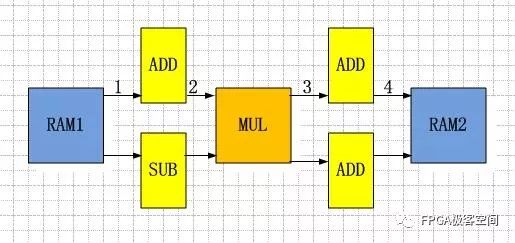

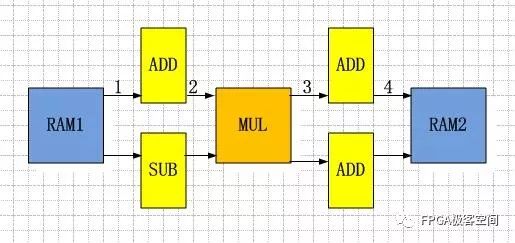

結構如上圖。在這種方式下,FPGA的片上RAM會消耗很多。

為了節省RAM,可以采用一塊RAM的流水線方式。在實現過程中要注意對RAM操作的reading-during-write,之前的文章介紹過了。這種方式速度會降低一半。

最節省的方式是使用控制器方式,但速度更低。這里不再介紹。

上圖所示的IFFT流程,存在大量的組合邏輯,時序遠遠不夠,所以應當在組合邏輯中加入寄存器提高速度。但是,寄存器流水線的級數又影響到了讀寫兩塊RAM的切換,從而影響計算效率,所以這里值得商榷。

由于設計中RAM輸出端沒有使用REG,所以1處應該加入REG,提高速度,否則1處會出現時序違規,1處的組合邏輯延遲很大。

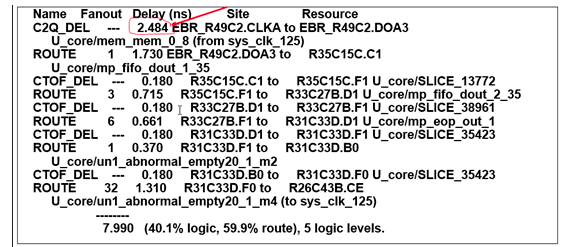

2處和3處也是值得深入考慮的地方,加法器的輸出到乘法器的輸入,以及乘法器的輸出再到加法器的輸入,均是大量的組合邏輯,設計中一定要注意,不能僅僅完成功能仿真就可以了,一定要在綜合工具下綜合一下,看看時序是否滿足。實踐中,這兩處均加入REG。

4處是否再加REG需要看綜合后的結果。根據實際分析,4處加REG會降低計算效率,讀RAM和寫RAM來不及切換,這是根據自己的設計得出的結果。

由于FFT計算過程用到乘法器,所以在IFFT中需要用到除法器。如何減少除法器使用的資源或者將除法器更改為其他邏輯實現,需要深入探討。

-

FPGA

+關注

關注

1646文章

22054瀏覽量

618801 -

RAM

+關注

關注

8文章

1392瀏覽量

117594 -

FFT

+關注

關注

15文章

445瀏覽量

61054

原文標題:關于硬件實現FFT逆運算

文章出處:【微信號:ALIFPGA,微信公眾號:FPGA極客空間】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

基于FPGA的超高速FFT硬件實現

基于FPGA的FFT算法硬件實現

Quartus中FFT模塊中文說明

關于調用IP核實現FFT

FFT至簡設計法實現法_FFT算法_蝶形運算_fpga

FFT 算法的一種 FPGA 實現

如何在FPGA上實現硬件上的FFT算法

怎么使用cordic旋轉方法在??VHDL中實現FFT?

基于FPGA的超高速FFT硬件實現

FPGA內嵌的塊RAM在FFT算法中的應用

WIMAX系統中可配置FFT_IFFT的實現

基于FPGA-IPCore的FFT仿真與硬件實現

采用IEEE745格式的浮點+ROM RAM的方式成功實現FFT的設計

關于FFT硬件實現,設計中RAM輸出端為何沒有使用REG

關于FFT硬件實現,設計中RAM輸出端為何沒有使用REG

評論