基于 0.18μm 1P3M 45V BCD 工藝設(shè)計(jì)實(shí)現(xiàn)了一款用于電表系統(tǒng)的異步 BUCK DC-DC 芯片。介紹了電表應(yīng)用系統(tǒng)中 BUCK DC-DC 的應(yīng)用環(huán)境,設(shè)計(jì)了 CCM 電流模式 PWM 調(diào)制方式的控制環(huán)路結(jié)構(gòu),對(duì) DC-DC 系統(tǒng)參數(shù)的折中進(jìn)行了分析,并用 Matlab 工具建模進(jìn)行驗(yàn)證。設(shè)計(jì)了 ESD 保護(hù)方案,給出了封裝方案。經(jīng)流片驗(yàn)證,測(cè)試結(jié)果顯示,芯片的功能和性能指標(biāo)達(dá)到設(shè)計(jì)要求。

1 引言

智能電表系統(tǒng)由計(jì)量、MCU、顯示與驅(qū)動(dòng)、存儲(chǔ)、通信(含模塊)、電源管理等部分組成,需要考慮整個(gè)系統(tǒng)每個(gè)芯片的電源解決方案。

PLC 載波模塊單獨(dú)一路電源供電,工作電壓 3.3 V / 5 V/12 V,通信時(shí)功耗<1.5 W(折合:VDD=5 V,IDD<300 mA)。國(guó)家電網(wǎng)公司企業(yè)標(biāo)準(zhǔn) Q/GDW355-2012[1]對(duì)通信模塊的供電電源的要求進(jìn)行了明確的規(guī)定:通信模塊模擬電源,由電能表提供,電壓范圍:+12 V±1 V(負(fù)載電流 0~125 mA)。通信模塊電源故障或短路時(shí)不應(yīng)影響電能表的基本功能(電表應(yīng)采取保護(hù)措施)。VCC 電源帶載(單相表125 mA,三相表 450 mA)情況下,VCC 電源的工頻紋波 Vp-p 應(yīng)小于 1‰。

本文的 BUCK DC-DC 芯片是針對(duì)電表應(yīng)用市場(chǎng)需求進(jìn)行特別優(yōu)化指標(biāo)的 45 V 600 mA BUCK DC-DC 轉(zhuǎn)換器 IC。該電路具有寬輸入電壓范圍(4.5 V~45 V),高效率,低輸出紋波(小于千分之一)、低溫度系數(shù)(全溫度范圍變化小于千分之五),最大典型輸出電流為 600 mA。

該電路采用電流模反饋環(huán)路架構(gòu),能夠提供快速的環(huán)路響應(yīng)。該電路采用 1.6 MHz 固定頻率的 PWM 調(diào)制方式。它能夠支持極小體積的外部元器件,包括輸入輸出陶瓷電容和電感等元件。芯片 SOT23-6 封裝。

目前,本 BUCK DC-DC 在電表系統(tǒng)中,搭配變壓器線圈,從交流電源中取電,處于一次降壓 DC-DC 穩(wěn)壓器的位置,對(duì)輸入電壓的范圍要求較寬,對(duì)生產(chǎn)工藝要求也較高。本 DC-DC 的負(fù)載主要是 PLC 載波模塊等,具有非常大的應(yīng)用市場(chǎng)。

本 BUCK DC-DC 芯片基于 0.18 μm 1P3M 45V BCD 工藝技術(shù)設(shè)計(jì)實(shí)現(xiàn),其技術(shù)水平達(dá)到并超過國(guó)內(nèi)外同類產(chǎn)品。高壓 DC-DC 技術(shù)的應(yīng)用非常廣泛,主要都是針對(duì)汽車、工控、電力儀表等中高端市場(chǎng)。本電路設(shè)計(jì)主要針對(duì)國(guó)內(nèi)及部分海外的電表市場(chǎng)。

2 系統(tǒng)應(yīng)用環(huán)境

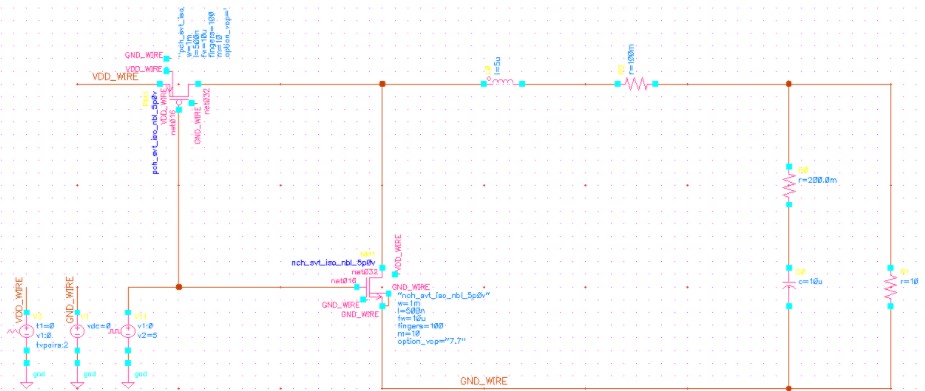

如圖 1 所示為輸出電壓 12 V 時(shí)的系統(tǒng)應(yīng)用圖,其前級(jí)為從交流電網(wǎng)取電的變壓器輸出,后級(jí)為 PLC 載波模塊。需要外置的續(xù)流二極管(異步整流),電感取值可以根據(jù)系統(tǒng)設(shè)計(jì)方案在 2.2 μH~ 47 μH 之間取值。33 pF 的反饋電容決定了一個(gè)零點(diǎn)的位置,可以根據(jù)系統(tǒng)環(huán)路穩(wěn)定性的需要進(jìn)行選擇。輸入和輸出節(jié)點(diǎn)分別加穩(wěn)壓濾波電容,從而獲得較好的輸入輸出紋波特性。

3 內(nèi)部系統(tǒng)設(shè)計(jì)

如圖 2 為本 BUCK DC-DC 芯片的系統(tǒng)設(shè)計(jì)框圖。本芯片適應(yīng)寬輸入電源范圍,4.5 V 到 45 V,內(nèi)置上開關(guān)管(NMOS),采用異步整流,用外置的肖特基二極管進(jìn)行續(xù)流,寬電感范圍(2.2 μH ~ 47 μH)。

內(nèi)置補(bǔ)償電路,內(nèi)置軟啟動(dòng)電路。內(nèi)置電流峰值檢測(cè)電路、短路保護(hù)短路、過溫保護(hù)電路。固定工作頻率 PWM 調(diào)制方式、電流模。

基于自舉方案的同步降壓型電源變換器的系統(tǒng)結(jié)構(gòu),采用共源級(jí)結(jié)構(gòu)實(shí)現(xiàn)強(qiáng)驅(qū)動(dòng)能力為 VBST 供電,避免了直接與模擬電源(VDD)比較,從而減小了自舉電路在頻繁開關(guān)過程中對(duì)于模擬電源的干擾。能夠支持大占空比、大負(fù)載電流的應(yīng)用。

采用一種巧妙地實(shí)現(xiàn)對(duì)功率開關(guān)電流的檢測(cè)電路結(jié)構(gòu)設(shè)計(jì),使得最終得到的輸出電流采樣檢測(cè)增益僅僅與 MOS 管的尺寸之比和兩個(gè)電阻串的比值有關(guān),消除了工藝、溫度、電源電壓的影響,在不受 PVT 變化影響的精準(zhǔn)的輸出電流采樣檢測(cè)。即使工藝波動(dòng)很大,溫度波動(dòng)很大,也能精確檢測(cè)電流。斜坡補(bǔ)償電流的實(shí)現(xiàn)方式,將對(duì)功率開關(guān)電流的采樣電流和斜坡補(bǔ)償電流累加轉(zhuǎn)換為電壓值后反饋到 PWM 電壓比較器,從而完成電源變換器的電流反饋環(huán)路。在此結(jié)構(gòu)的基礎(chǔ)上,很精簡(jiǎn)地實(shí)現(xiàn)了電流峰值檢測(cè)的實(shí)現(xiàn)電路。

設(shè)計(jì)了一種電流環(huán)路上 PWM 波形產(chǎn)生電路,能夠在大占空比工作時(shí)優(yōu)化輸出紋波。輸出紋波幅度能夠?qū)崿F(xiàn)輸出電壓的千分之一以內(nèi)。

4 DC-DC 系統(tǒng)指標(biāo)的平衡

本芯片的設(shè)計(jì)難點(diǎn)之一即為 DC-DC 系統(tǒng)指標(biāo)的平衡,特別是 Vin/Vo/L/Co/Io 等外圍條件大范圍變化時(shí),如何平衡系統(tǒng)指標(biāo)。

在 PWM 調(diào) 制方式的反饋環(huán)路當(dāng)中無論采用電流模式還是電壓模式都需要一個(gè)斜坡補(bǔ)償電壓。當(dāng)輸出出現(xiàn)微小波動(dòng)的時(shí)候輸出的占空比能否自動(dòng)回到理想的值。如果不加入斜坡補(bǔ)償?shù)脑挘诶碚撜伎毡却笥?0.5 時(shí),輸出電流有一個(gè)微小的擾動(dòng)的話,電流模式下輸出電流會(huì)趨于發(fā)散震蕩。

假設(shè) ml 和 m2 分別是輸出電流的上升和下降的速率,在加入了補(bǔ)償斜坡之后假如斜坡補(bǔ)償?shù)男甭蕿?-ma。可以證明斜坡補(bǔ)償?shù)男甭市枰獫M足 ma > 0.5×m2 = 0.5×Vo/L,系統(tǒng)才能穩(wěn)定[2]。為了得到足夠的斜坡補(bǔ)償斜率值,必須根據(jù)電感電流下降的斜率設(shè)定補(bǔ)償?shù)碾娏鳌栴}是其中輸出電流下降的斜率m2和輸出電壓是成正比的。因此斜坡電流最好能夠和輸出電壓成正比。如果斜坡補(bǔ)償?shù)碾娏鞴潭ǎ捅仨毟鶕?jù)輸出最大電壓來確定補(bǔ)償電流(因?yàn)檩敵鲭妷鹤畲髸r(shí),m2 最大,m1 最小)。一般來說取值在 ma = 0.7×m2 附近。但是過補(bǔ)償也有風(fēng)險(xiǎn),降低系統(tǒng)動(dòng)態(tài)性能、降低最大峰值電流能力(從而限制最終的輸出驅(qū)動(dòng)能力)。

系統(tǒng)工作于 CCM 狀態(tài)時(shí),要滿足穩(wěn)定性要求的最小補(bǔ)償斜率。若取 ma = 0.5×m2 = 0.5×Vo/L,

若取 ma = n×m2 = n×Vo/L 時(shí),

則等效到 EAOUT 處的電流峰值 Ipeak 的最大值為

討論(1)n > 0.5 時(shí),Ipeak_max 隨 Vin 升高減小。在正常電流輸出情況下,Io < 600 mA,Ipeak_max 變化規(guī)律就是 EAOUT 的變化規(guī)律。

(2)n < 0.5 時(shí),Ipeak_max 隨 Vin 升高而升高,一般不會(huì)把系統(tǒng)設(shè)置到這個(gè)范圍,一方面可能不穩(wěn)定,另一方面不利于效率優(yōu)化。

假設(shè)應(yīng)用需求將輸出電流典型值取 0~660 mA,即要求系統(tǒng)工作于大占空比時(shí)(補(bǔ)償量最大)仍然可以輸出 660 mA 電流。

基于以上 Ipeak_max 公式進(jìn)行討論,分析 Iomax = 660 mA、fsw = 1.6 MHz(Ts = 0.625 μs)、Vo = 12 V 補(bǔ)償斜率為 0.7×Vo/L(即 n = 0.7)時(shí)的最大值 Ipeak_max 隨電感的變化范圍。如圖 3 所示為用 Matlab 算出的結(jié)果,其中變量只有 Vo、Vin、L。

從結(jié)果來看,Vin 的變化對(duì) Ipeak_max 的影響很小。Vo 和 L 的影響要明顯的多。這個(gè) Ipeak_max 是對(duì)EA 輸出電壓范圍所對(duì)應(yīng)的電流范圍的限定,也就是要求 EA 輸出電壓范圍所對(duì)應(yīng)的電流范圍要大于所有情況的范圍。從 Matlab 計(jì)算結(jié)果來看,如果全部包含要大于 5 A,這是不可能的。所以 EA 輸出范圍只能盡可能大,但是也不能兼顧所有的應(yīng)用情況。在 L 很小、占空比很大或者兩者兼有時(shí)不能滿足要求。

舉例,如果設(shè)置 Gcs=1 A/V,EAOUTmax = 3.1 V,EAOUT 能夠支持的 Ipeak_max = EAOUTmax×Gcs = 3.1 A。如果設(shè)置 Gcs = 0.66 A/V,EAOUTmax = 3.1 V,EAOUT 能夠支持的 Ipeak_max = EAOUTmax×Gcs = 2.046 A。所以提高 Gcs 或者提高 EAOUT 的上限,都可以提高 EAOUT 支持的Ipeak_max。

以 Ipeak_max = EAOUTmax×Gcs =3.1 A 為基礎(chǔ),當(dāng) Vo= 12 V,fsw = 1 MHz,Iomax = 660 mA 時(shí),根據(jù) Vin 的取值,得到最小可用電感值 L 如表 1 Vin 決定的最小 L,圖 4 Power MOS SIZE 和驅(qū)動(dòng)電路的最優(yōu)解。

另外,也可以用 Matlab 對(duì)功率損耗建模,以得出 Power MOS SIZE 和驅(qū)動(dòng)電路的最優(yōu)解[3]。上升沿設(shè)置為 25 ns,下降沿設(shè)置為 6 ns,利用 Matlab 模型對(duì) Power MOS SIZE 掃描,得到結(jié)果如下所示。fsw = 1.6 MHZ,L= 47μH,優(yōu)先考慮 Vin =14 V,Vo = 12 V,Io = 120 mA 的應(yīng)用情況,在 Ron = 0.413 Ω時(shí),是最優(yōu)解。

5 ESD 方案設(shè)計(jì)實(shí)現(xiàn)

本 BUCK DC-DC 電路的引腳的工作范圍比較復(fù)雜,Vin = EN =(-0.3 V~ 45 V),F(xiàn)B =(-0.3 V~ 6 V),LX =(-0.3 V ~ Vin +0.3 V),BST-GND = LX + 6 V,BST-LX =(-0.3 V ~ 6 V),典型應(yīng)用中要求通過 HBM 2 kV ESD 測(cè)試。所采用的 ESD 實(shí)現(xiàn)方案如圖 5 所示。

由于本芯片為電源設(shè)計(jì)方案,PIN 腳之間對(duì)電源的方案復(fù)雜,我們選擇采用共地通路的方法,即所有的 ESD 通路均通過公共地環(huán)形成通路。高壓腳到 GND 之間采用 SCR IP 以節(jié)省面積,低壓腳到 GND 之間采用 GGN MOS 結(jié)構(gòu)實(shí)現(xiàn),BST 到 LX 之間采用了帶 NBL 和深阱隔離的低壓 GGN MOS 結(jié)構(gòu)實(shí)現(xiàn),在輸入端口加入了二級(jí)保護(hù)結(jié)構(gòu)。

5 驗(yàn)證

所有的電路仿真測(cè)試均基于 0.18μm 1P3M 45 V BCD 工藝。電源電壓 Vin 拉偏范圍 4.5 V~45 V,溫度拉偏范圍 -40 ℃ ~ 85 ℃。采用 Cadence 的SPECTRE 對(duì)電路進(jìn)行模塊和全芯片的仿真驗(yàn)證。本 BUCK DC-DC 的量產(chǎn)芯片 DECAP 后看到的管芯和封裝如圖 6 所示,采用 SOT23-6 封裝。

經(jīng)流片驗(yàn)證,芯片的功能和性能指標(biāo)符合定義要求,其中空載待機(jī)靜態(tài)電流僅約 600 μA。輸入 16 V,輸出 12 V,L = 47μH,負(fù)載電流 300 mA 時(shí),效率高至 95.6%。

不同負(fù)載電流和輸入電壓對(duì)效率的影響結(jié)果如圖 7 所示。不同負(fù)載電流對(duì)輸出電壓的影響如圖 8 所示。不同輸入電壓對(duì)輸出電壓的影響如圖 9 所示。如圖 10 所示為輸出紋波測(cè)試結(jié)果(Vin = 18±1 V,220 V 變壓器供電,Vo = 12 V,Io = 120 mA,輸出電容 10μF + 0.1μF+ 470μF,電感 47 μH 輸入電容 2200 μF,示波器帶寬 20 MHz)。在 -40℃~85℃全溫度范圍內(nèi),輸出電壓的變化能夠控制在輸出電壓的千分之五。能夠?qū)崿F(xiàn)很小的輸入輸出壓差,在 Vout = 12 V、負(fù)載電流 600 mA 滿載測(cè)試時(shí),最小壓差可以低至 0.72 V。在上海宜碩按照標(biāo)準(zhǔn) MIL-STD-883H Method 3015.8 測(cè)試,通過 2 kV HBM ESD 測(cè)試。目前產(chǎn)品在市場(chǎng)銷售。

4 結(jié)語(yǔ)

本文基于 0.18μm 1P3M 45 V BCD 工藝設(shè)計(jì)實(shí)現(xiàn)了一款異步 BUCK DC-DC 芯片。介紹了電表應(yīng)用系統(tǒng)中 BUCK DC-DC 的應(yīng)用環(huán)境,設(shè)計(jì)了 CCM 的電流模 PWM 調(diào)制方式的控制環(huán)路結(jié)構(gòu),對(duì) DC-DC 系統(tǒng)參數(shù)的折中進(jìn)行了分析,并用 Matlab工具建模進(jìn)行驗(yàn)證。設(shè)計(jì)了 ESD 保護(hù)方案,給出了封裝方案。經(jīng)流片驗(yàn)證,測(cè)試結(jié)果顯示,芯片的功能和性能指標(biāo)達(dá)到設(shè)計(jì)要求。

-

芯片

+關(guān)注

關(guān)注

456文章

51273瀏覽量

427761 -

智能電表

+關(guān)注

關(guān)注

25文章

941瀏覽量

109392

原文標(biāo)題:用于電表系統(tǒng)的 45 V 600 mA BUCK DC-DC 芯片設(shè)計(jì)

文章出處:【微信號(hào):appic-cn,微信公眾號(hào):集成電路應(yīng)用雜志】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

DC-DC 和LDO 簡(jiǎn)單介紹

#硬聲創(chuàng)作季 DC-DC電路之buck電路

能否介紹幾種Buck架構(gòu)DC-DC轉(zhuǎn)換器?

DC-DC BUCK電源芯片的基本工作原理

DC-DC開關(guān)穩(wěn)壓芯片(LM2596)講解

DC-DC與電感的相關(guān)資料分享

Buck型DC-DC的相關(guān)資料分享

LDO和DC-DC有什么不同?

常用DC-DC buck原理圖電路圖分享

DC-DC芯片資料分享

智能電表專用DC-DC芯片

介紹電表應(yīng)用系統(tǒng)中 BUCK DC-DC 的設(shè)計(jì)與應(yīng)用

介紹電表應(yīng)用系統(tǒng)中 BUCK DC-DC 的設(shè)計(jì)與應(yīng)用

評(píng)論