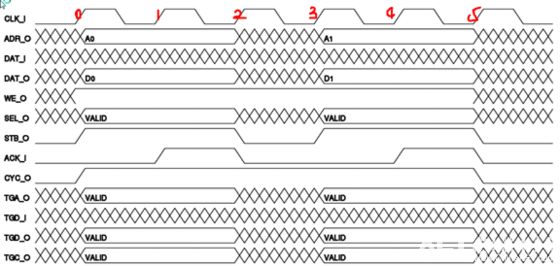

圖17顯示的是一個標準的塊寫周期時序圖。塊寫周期可以在每一個時鐘周期完成一次數據傳輸。但是,本例中顯示了主機和從機插入等待狀態以控制數據傳輸速率的情況。圖中一共顯示了5個傳輸。第二次傳輸后,主機插入了一個等待狀態。第四次傳輸后,從機插入了一個等待狀態。整個周期在第五次傳輸之后結束。

圖17 標準塊寫周期

總線協議的執行流程如下:

時鐘上升沿0:

·主機將有效地址置于ADR_O()和TGA_O();

·主機將WE_O置位,以表明進入寫周期;

·主機輸出SEL_O()(bank select)表明其操作的數據地址;

·主機將CYC_O和TGC_O()置位,以表明周期的開始;

·主機將STB_O置位,以表明第一個段(phase)的開始;

注意:主機可以在時鐘上升沿1之前的任意時間,將CYC_O和TGC_O()置位。

時鐘上升沿1:

·從機解碼輸入,并作出從機響應(ACK_I)。

時鐘上升沿2:

·主機將監控ACK_I信號;

·主機將STB_O復位,以插入一個等待狀態(-WSW-)。

時鐘上升沿3:

·主機將有效地址置于ADR_O()和TGA_O();

·主機將WE_O置位,以表明進入寫周期;

·主機輸出SEL_O()(bank select)表明其操作的數據地址;

·主機將CYC_O和TGC_O()置位,以表明周期的開始;

·主機將STB_O置位,以表明第二個段(phase)的開始。

時鐘上升沿4:

·主機將有效地址置于ADR_O()和TGA_O()

·主機將WE_O復位,以表明進入讀周期;

·主機輸出SEL_O()(bank select)表明其操作的數據地址;

·主機將STB_O置位。

·從機解碼輸入,并對ACK_I做出相應。

時鐘上升沿5:

·主機監控ACK_I信號;

·主機將STB_O和CYC_O復位,以結束本次塊讀周期。

流水線塊寫操作

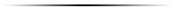

流水線塊寫模式的時序圖如圖18所示。

圖18 流水線塊寫周期

總線協議的執行流程如下:

時鐘上升沿0:

·主機將有效地址置于ADR_O()和TGA_O();

·主機將WE_O置位,以表明進入寫周期;

·主機輸出SEL_O()(bank select)表明其操作的數據地址;

·主機將CYC_O和TGC_O()置位,以表明周期的開始;

·主機將STB_O置位,以表明第一個段(phase)的開始;

·主機監控ACK_I信號,并準備鎖存DAT_I()和TGD_I()信號。

時鐘上升沿1:

·從機解碼輸入,并作出從機響應(ACK_I);

·主機將有效地址置于ADR_O()和TGA_O();

·主機將WE_O置位,以表明進入寫周期;

·主機輸出SEL_O()(bank select)表明其操作的數據地址;

·主機將STB_O置位,以表明第二個段(phase)的開始。

時鐘上升沿2:

時鐘上升沿3:

·從機解碼輸入,并作出從機響應(ACK_I);

·當STALL_I為低電平時(inactive),主機將STB_O信號復位。

時鐘上升沿4:

·主機將CYC_O信號復位,當接受到第二個ACK_O信號時。

-

數據傳輸

+關注

關注

9文章

2020瀏覽量

66109 -

主機

+關注

關注

0文章

1038瀏覽量

36002

原文標題:【博文連載】Wishbone總線周期之塊寫操作

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

怎么由芯片的時序圖寫它的程序?

請問如何用proteus仿真出8086的總線周期時序圖?

求助:有哪位大神用過AD977,怎么用Verilog寫它的時序圖

關于單片機時序圖分析

【轉帖】教你看懂時序圖

教程 | SDRAM讀寫時序介紹(配時序圖)

怎么由芯片的時序圖寫程序?_單片機對1602液晶時序圖編程設計

關于塊寫周期時序圖的應用

關于塊寫周期時序圖的應用

評論