我知道,我對(duì)與電子有關(guān)的所有事情都很著迷,但不論從哪個(gè)角度看,今天的現(xiàn)場(chǎng)可編程門陣列(FPGA),都顯得“鶴立雞群”,真是非常棒的器件。如果在這個(gè)智能時(shí)代,在這個(gè)領(lǐng)域,想擁有一技之長(zhǎng)的你還沒有關(guān)注FPGA,那么世界將拋棄你,時(shí)代將拋棄你。

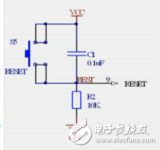

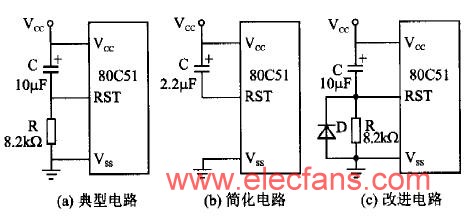

在實(shí)際設(shè)計(jì)中,由于外部阻容復(fù)位時(shí)間短,可能無法使FPGA內(nèi)部復(fù)位到理想的狀態(tài),所以今天介紹一下網(wǎng)上流行的復(fù)位邏輯。

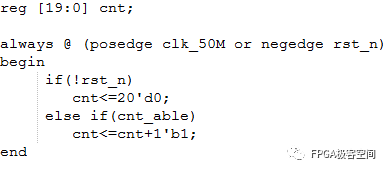

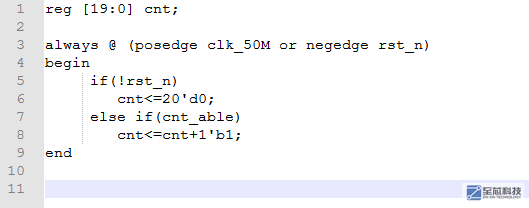

在基于verilog的FPGA設(shè)計(jì)中,我們常常可以看到以下形式的進(jìn)程:

信號(hào)rst_n用來對(duì)進(jìn)程中所用變量的初始化,這個(gè)復(fù)位信號(hào)是十分重要的,如果沒有復(fù)位,會(huì)導(dǎo)致一些寄存器的初始值變得未知,如果此時(shí)FPGA就開始工作的話,極易導(dǎo)致錯(cuò)誤。

那么,這個(gè)復(fù)位信號(hào)來自何處?難道我們做好的系統(tǒng),每次上電后都要手動(dòng)按一下reset按鈕么?

答案是否定的!這個(gè)復(fù)位信號(hào)其實(shí)是由特定的程序來產(chǎn)生的,系統(tǒng)每次上電,都會(huì)由該程序產(chǎn)生一個(gè)復(fù)位信號(hào),從而避免了手動(dòng)復(fù)位。

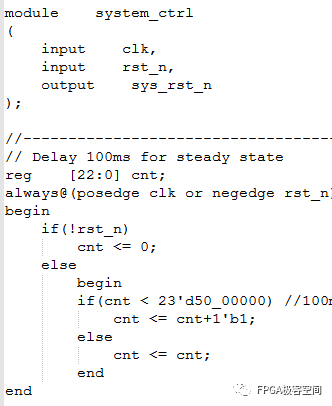

復(fù)位的方案很多,下面介紹一個(gè)簡(jiǎn)單方案。

clk:50M時(shí)鐘輸入

rst_n:異步復(fù)位輸入

sys_rst_n:系統(tǒng)全局同步復(fù)位信號(hào)

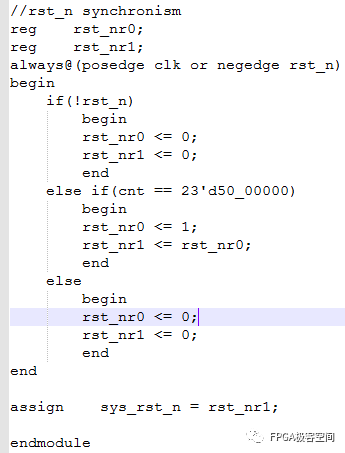

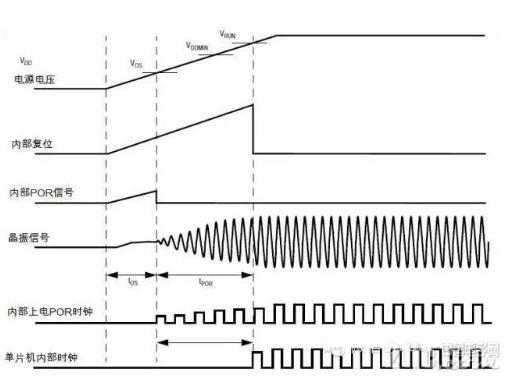

第一個(gè)進(jìn)程用來延時(shí),當(dāng)上電后,延時(shí)100ms,以保證FPGA內(nèi)部達(dá)到穩(wěn)定狀態(tài);此時(shí)sys_rst_n始終為0,也就是系統(tǒng)時(shí)鐘處于復(fù)位狀態(tài)中;2.當(dāng)100ms延時(shí)結(jié)束后,sys_rst_n與系統(tǒng)時(shí)鐘同步釋放,即sys_rst_n拉高,復(fù)位結(jié)束,系統(tǒng)開始正常工作。

-

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615359 -

Verilog

+關(guān)注

關(guān)注

29文章

1366瀏覽量

111990

原文標(biāo)題:流行的FPGA的上電復(fù)位

文章出處:【微信號(hào):ALIFPGA,微信公眾號(hào):FPGA極客空間】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

簡(jiǎn)談FPGA的上電復(fù)位

AVR單片機(jī)的復(fù)位:看門狗復(fù)位、上電復(fù)位、掉電復(fù)位

Spartan-6 FPGA是否需要設(shè)計(jì)中的上電復(fù)位電路

BSC上下電復(fù)位對(duì)語音的影響分析

單片機(jī)上電復(fù)位和復(fù)位延時(shí)的時(shí)序分析

上電復(fù)位和按鍵復(fù)位區(qū)別

單片機(jī)上電復(fù)位與欠壓復(fù)位的過程解析

(70)Verilog HDL測(cè)試激勵(lì):復(fù)位激勵(lì)2

(77)Verilog HDL測(cè)試激勵(lì):復(fù)位激勵(lì)3

FPGA復(fù)位電路的實(shí)現(xiàn)——以cycloneIII系列芯片為例

FPGA復(fù)位電路的實(shí)現(xiàn)方式

單片機(jī)上位復(fù)位電路與按鍵與上電復(fù)位的區(qū)別

IC上電復(fù)位和關(guān)斷功能建議

基于verilog的FPGA中上電復(fù)位設(shè)計(jì)

基于verilog的FPGA中上電復(fù)位設(shè)計(jì)

評(píng)論