一.常用電路的EMC設計

A.電源電路

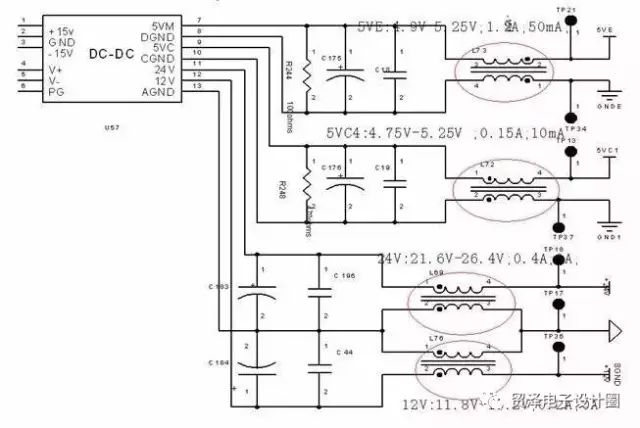

電源電路設計中,功能性設計主要考慮溫升和紋波大小。溫升大小由結構散熱和效率決定;輸出紋波除了采用輸出濾波外,輸出濾波電容的選取也很關鍵:大電容一般采用低ESR電容,小電容采用0.1UF和1000pF共用。電源電路設計中,電磁兼容設計是關鍵設計。主要涉及的電磁兼容設計有:傳導發射和浪涌。

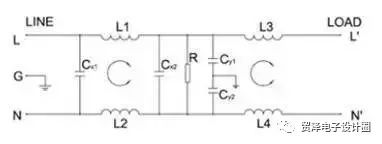

傳導發射設計一般采用輸入濾波器方式。外部采購的濾波器內部電路一般采用下列電路:

Cx1和Cx2為X電容,防止差模干擾。差模干擾大時,可增加其值進行抑制;Cy1和Cy2為Y電容,防止共模干擾。共模干擾大時,可增加其值進行抑制。需要注意的是,如自行設計濾波電路,Y電容不可設計在輸入端,也不可雙端都加Y電容。

浪涌設計一般采用壓敏電阻。差模可根據電源輸入耐壓選取;共模需要電源輸入耐壓和產品耐壓測試綜合考慮。

當浪涌能量大時,也可考慮壓敏電阻(或TVS)與放電管組合設計。

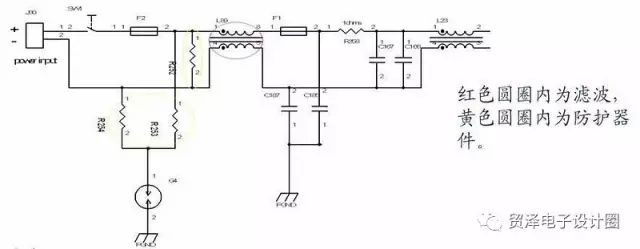

1 電源輸入部分的EMC設計

應遵循①先防護后濾波;②CLASS B規格要求的電源輸入端推薦兩級濾波電路,且盡量靠近輸入端;③在電源輸入端濾波電路前和濾波電路中無采樣電路和其它分叉電路;如果一定有采樣電路,采樣電路應額外增加了足夠的濾波電路。

原因說明:

①先防護后濾波:

第一級防護器件應在濾波器件之前,防止濾波器件在浪涌、防雷測試中損壞,或導致濾波參數偏離,第二級保護器件可以放在濾波器件的后面;選擇防護器件時,還應考慮個頭不要太大,防止濾波器件在PCB布局時距離接口太遠,起不到濾波效果。

②CLASS B規格要求的電源輸入端推薦兩級濾波電路,且盡量靠近輸入端:

CLASSB要求比CLASS A要求小10dB,即小3倍,所以應有兩級濾波電路;

CLASSA規格要求至少一級濾波電路;所謂一級濾波電路指包含一級共模電感的濾波電路。

③在電源輸入端濾波電路前和濾波電路中無采樣電路和其它分叉電路;如果一定有采樣電路,采樣電路應額外增加了足夠的濾波電路:

電源采樣電路應從濾波電路后取;

如果采用電路精度很高,必須從電源輸入口進行采樣時,必須增加額外濾波電路。

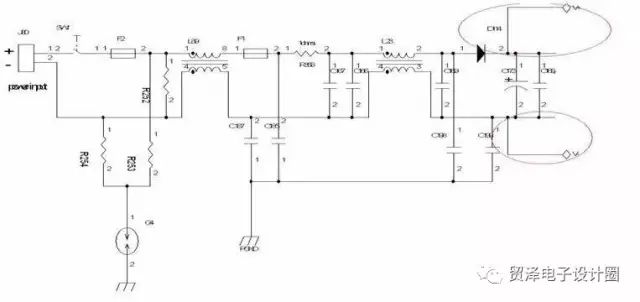

2 電源輸出部分的EMC設計

應遵循①電源模塊輸出一定要求有濾波措施,推薦使用共模電感或差模電感;②長距離電源走線是否預留足夠電容組10uF/0.1uF或1uF/0.01uF,應考慮PCB板每間隔187.5px放置一對。

原因說明:

①電源模塊輸出一定要求有濾波措施,推薦使用共模電感或差模電感:

用共模電感進行濾波,防止開關電源的噪聲串到整個單板的電源、地上;

用磁珠進行濾波,防止開關電源的噪聲串到整個單板的電源、地上;

在電源輸出端設計Y電容時,需斟酌,如有螺釘可使Y電容就近接地時,可考慮增加,否則不用。

②長距離電源走線是否預留足夠電容組10uF/0.1uF或1uF/0.01uF,應考慮PCB板每間隔187.5px放置一對:

當電源模塊有多路電源輸出時,比如提供給通訊接口的通訊電源、地,提供給傳感器供電的12V、24V電源、地,提供給繼電器驅動用的12V電源、地,均會存在長距離走線問題,為了使電源、地之間的阻抗最小,且回路最小,應每隔187.5px增加一對電容。

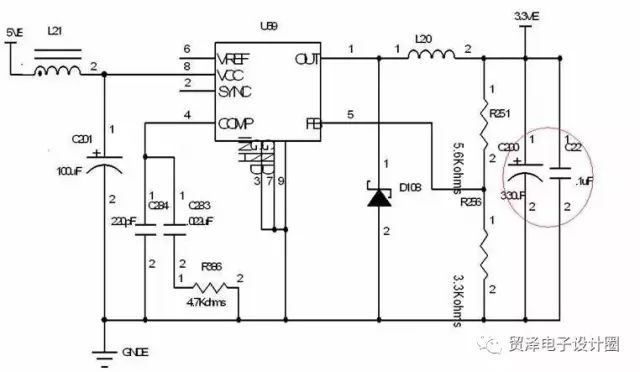

3 電源轉換芯片的EMC設計

應遵循電源轉換芯片輸入輸出端應并聯BULK電容和去耦電容;電容容值應依據芯片手冊推薦,或者依據驅動能力來估算;開關轉換芯片輸出應考慮磁珠進行濾波。

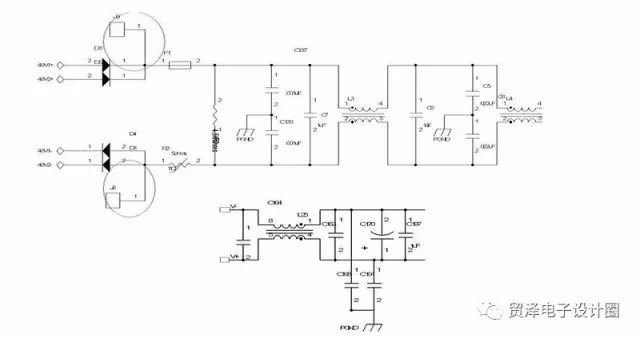

B.接口電路

接口電路多種多樣,一般需電纜引出的接口電路需要較完備的電磁兼容設計,如CAN總線、RS485總線;其他的接口電路如RS232、USB等一般采用磁珠加TVS管設計。

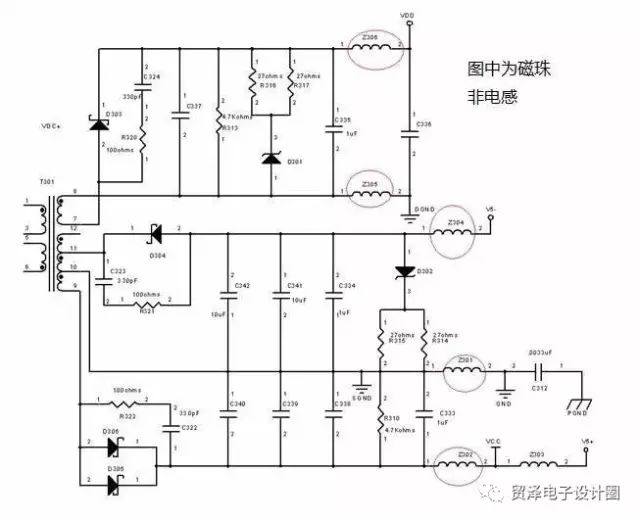

1 RS485/CAN接口設計

RS485接口標準電路如下:

在具體設計中,R1/R2用自恢復保險絲,保護效果更好。一般不使用放電管;TVS管可作為預留設計(取決于驅動芯片內部是否包含TVS管)。

需要注意的是,共模電容需設計在接口端,這樣做的原因是抑制外部的傳導干擾和快速脈沖群干擾,以免其對RS485數據通信產生擾亂。

CAN接口保護時,TVS和電容參數略有不同。

RS-485總線共模電壓范圍為-7~+12V;

CAN總線的共模電壓為-2~+7 V。

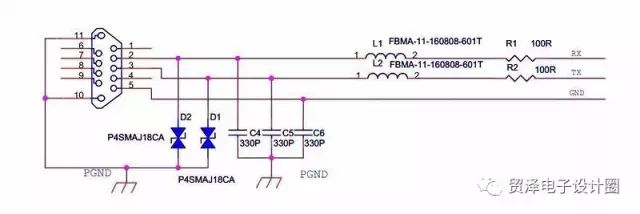

2 RS232接口設計

RS232接口標準電路如下:

485/CAN差分接口優先選用共模電感或者磁珠進行濾波,232接口用磁珠進行濾波;濾波電路盡量靠近端口,磁珠或共模電感到端子間PCB走線長度小于62.5px;如防護器件過多,磁珠到端子間PCB走線長度距離大于62.5px,則應在最靠近接口處增加Y電容或高壓電容進行濾波,Y電容要滿足耐壓要求;如果采用屏蔽電纜,屏蔽層要接PGND;需要接出到端子的通訊地需要經過濾波。

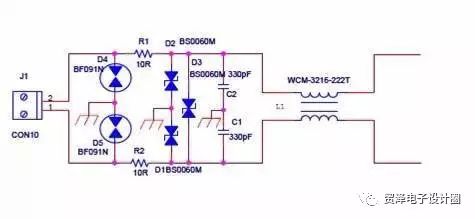

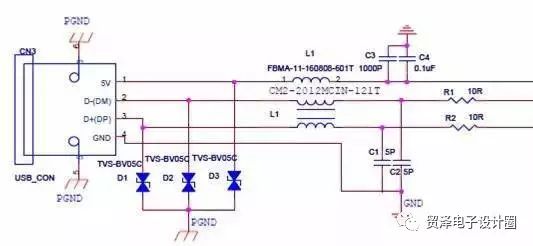

3 USB接口設計

USB接口標準電路如下:

具體設計中,共模電感一般用磁珠代替;C1、C2共模電容為預留設計,當USB口有輻射輸出干擾時,C1、C2可對其進行抑制。

需要注意的是,因USB數據速率高,選用TVS時必須采用低電容的TVS管,TVS管最少能承受8KV以上的接觸靜電放電。

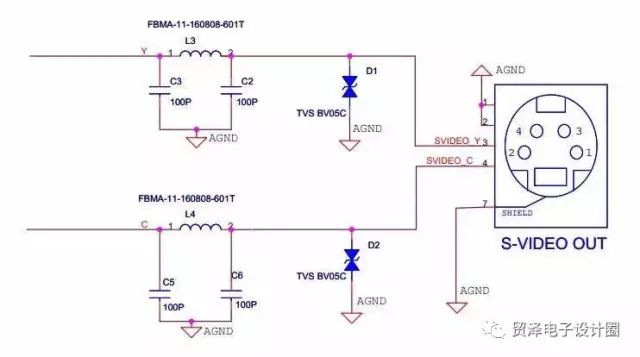

4 S_VIDEO接口設計

S_VIDEO接口標準電路如下:

磁珠電容可根據實際情況進行參數調整。

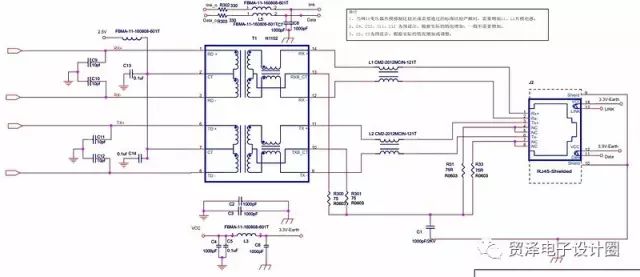

5 以太網接口設計

以太網接口標準電路如下:

當網口變壓器共模抑制比較差或需要通過的標準比較嚴酷時,需要增加L1、L2共模電感;C9、C10、C11、C12為預設計,根據實際的情況增加,一般不需要增加;C2、C3為與設計,根據是實際的情況增加或調整。

C.時鐘晶體電路

時鐘晶體電路一般有兩種:無源晶體電路和有源震蕩器電路。時鐘晶體電路一般是輻射發射的干擾源。

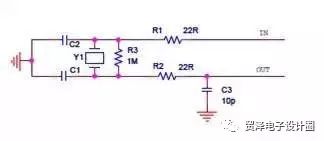

1 無源晶體

無源晶體標準電路如下:

在實際設計時,R3電阻和C3電容為預留設計。R3電阻可幫助啟震;C3電容可改善震蕩信號質量。

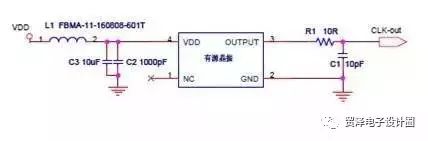

2 有源震蕩器

標準電路如下:

實際設計時,C1是預留設計。C1電容可改善震蕩器輸出信號質量。

供電磁珠一般不可缺省,其作用時防止震蕩器的高頻信號通過電源污染外部電路。

時鐘芯片電源管腳采用LC濾波電路或者PI濾波電路;晶體外殼要做接地設計;時鐘信號分叉時在分叉后每路都設置匹配電阻,匹配電阻靠近時鐘芯片;T型網絡,或采用末端匹配。

二.常用電路PCB設計的EMC考慮

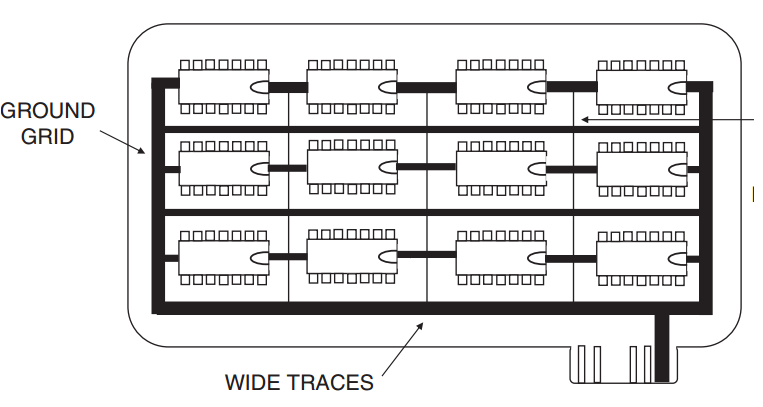

A.器件的布局

在PCB設計的過程中,從EMC角度,首先要考慮三個主要因素:輸入/輸出引腳的個數,器件密度和功耗。一個實用的規則是片狀元件所占面積為基片的20%,每平方英寸耗散功率不大于2W。

在器件布置方面,原則上應將相互有關的器件盡量靠近,將數字電路、模擬電路及電源電路分別放置,將高頻電路與低頻電路分開。易產生噪聲的器件、小電流電路、大電流電路等應盡量遠離邏輯電路。對時鐘電路和高頻電路等主要干擾和輻射源應單獨安排,遠離敏感電路。輸入輸出芯片要位于接近混合電路封裝的I/O出口處。

高頻元器件盡可能縮短連線,以減少分布參數和相互間的電磁干擾,易受干擾元器件不能相互離得太近,輸入輸出盡量遠離。震蕩器盡可能靠近使用時鐘芯片的位置,并遠離信號接口和低電平信號芯片。元器件要與基片的一邊平行或垂直,盡可能使元器件平行排列,這樣不僅會減小元器件之間的分布參數,也符合混合電路的制造工藝,易于生產。

在混合電路基片上電源和接地的引出焊盤應對稱布置,最好均勻地分布許多電源和接地的I/O連接。裸芯片的貼裝區連接到最負的電位平面。

在選用多層混合電路時,電路板的層間安排隨著具體電路改變,但一般具有以下特征。

(1)電源和地層分配在內層,可視為屏蔽層,可以很好地抑制電路板上固有的共模RF干擾,減小高頻電源的分布阻抗。

(2)板內電源平面和地平面盡量相互鄰近,一般地平面在電源平面之上,這樣可以利用層間電容作為電源的平滑電容,同時接地平面對電源平面分布的輻射電流起到屏蔽作用。

(3)布線層應盡量安排與電源或地平面相鄰以產生通量對消作用。

B.PCB走線

在電路設計中,往往只注重提高布線密度,或追求布局均勻,忽視了線路布局對預防干擾的影響,使大量的信號輻射到空間形成干擾,可能會導致更多的電磁兼容問題。因此,良好的布線是決定設計成功的關鍵。

1 地線的布局

地線不僅是電路工作的電位參考點,還可以作為信號的低阻抗回路。地線上較常見的干擾就是地環路電流導致的地環路干擾。解決好這一類干擾問題,就等于解決了大部分的電磁兼容問題。地線上的噪音主要對數字電路的地電平造成影響,而數字電路輸出低電平時,對地線的噪聲更為敏感。地線上的干擾不僅可能引起電路的誤動作,還會造成傳導和輻射發射。因此,減小這些干擾的重點就在于盡可能地減小地線的阻抗(對于數字電路,減小地線電感尤為重要)。

地線的布局要注意以下幾點:

(1)根據不同的電源電壓,數字電路和模擬電路分別設置地線。

(2)公共地線盡可能加粗。在采用多層厚膜工藝時,可專門設置地線面,這樣有助于減小環路面積,同時也降低了接受天線的效率。并且可作為信號線的屏蔽體。

(3)應避免梳狀地線,這種結構使信號回流環路很大,會增加輻射和敏感度,并且芯片之間的公共阻抗也可能造成電路的誤操作。

(4)板上裝有多個芯片時,地線上會出現較大的電位差,應把地線設計成封閉環路,提高電路的噪聲容限。

(5)同時具有模擬和數字功能的電路板,模擬地和數字地通常是分離的,只在電源處連接。

2 電源線的布局

一般而言,除直接由電磁輻射引起的干擾外,經由電源線引起的電磁干擾最為常見。因此電源線的布局也很重要,通常應遵守以下規則。

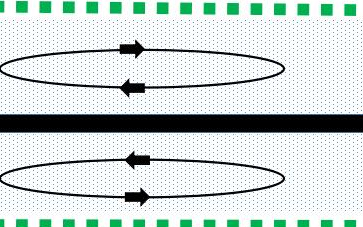

(1)電源線盡可能靠近地線以減小供電環路面積,差模輻射小,有助于減小電路交擾。不同電源的供電環路不要相互重疊。

(2)采用多層工藝時,模擬電源和數字電源分開,避免相互干擾。不要把數字電源與模擬電源重疊放置,否則就會產生耦合電容,破壞分離度。

(3)電源平面與地平面可采用完全介質隔離,頻率和速度很高時,應選用低介電常數的介質漿料。電源平面應靠近接地平面,并安排在接地平面之下,對電源平面分布的輻射電流起到屏蔽作用。

(4)芯片的電源引腳和地線引腳之間應進行去耦。去耦電容采用0.01uF的片式電容,應貼近芯片安裝,使去耦電容的回路面積盡可能減小。

(5)選用貼片式芯片時,盡量選用電源引腳與地引腳靠得較近的芯片,可以進一步減小去耦電容的供電回路面積,有利于實現電磁兼容。

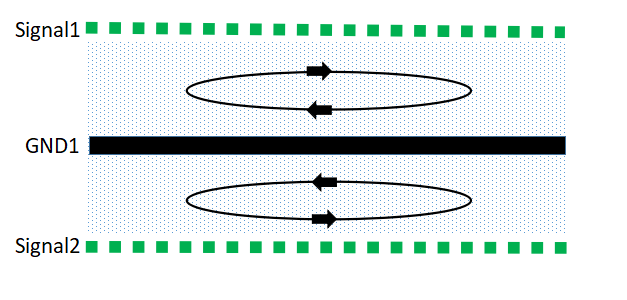

3 信號線的布局

在使用單層薄膜工藝時,一個簡便適用的方法是先布好地線,然后將關鍵信號,如高速時鐘信號或敏感電路靠近它們的地回路布置,最后對其它電路布線。信號線的布置最好根據信號的流向順序安排,使電路板上的信號走向流暢。

如果要把EMI減到最小,就讓信號線盡量靠近與它構成的回流信號線,使回路面積盡可能小,以免發生輻射干擾。低電平信號通道不能靠近高電平信號通道和無濾波的電源線,對噪聲敏感的布線不要與大電流、高速開關線平行。如果可能,把所有關鍵走線都布置成帶狀線。不相容的信號線(數字與模擬、高速與低速、大電流與小電流、高電壓與低電壓等)應相互遠離,不要平行走線。信號間的串擾對相鄰平行走線的長度和走線間距極其敏感,所以盡量使高速信號線與其它平行信號線間距拉大且平行長度縮小。

導帶的電感與其長度和長度的對數成正比,與其寬度的對數成反比。因此,導帶要盡可能短,同一元件的各條地址線或數據線盡可能保持長度一致,作為電路輸入輸出的導線盡量避免相鄰平行,最好在之間加接地線,可有效抑制串擾。低速信號的布線密度可以相對大些,高速信號的布線密度應盡量小。

在多層厚膜工藝中,除了遵守單層布線的規則外還應注意:

盡量設計單獨的地線面,信號層安排與地層相鄰。不能使用時,必須在高頻或敏感電路的鄰近設置一根地線。分布在不同層上的信號線走向應相互垂直,這樣可以減少線間的電場和磁場耦合干擾;同一層上的信號線保持一定間距,最好用相應地線回路隔離,減少線間信號串擾。每一條高速信號線要限制在同一層上。信號線不要離基片邊緣太近,否則會引起特征阻抗變化,而且容易產生邊緣場,增加向外的輻射。

4 時鐘線路的布局

時鐘電路在數字電路中占有重要地位,同時又是產生電磁輻射的主要來源。一個具有2ns上升沿的時鐘信號輻射能量的頻譜可達160MHz。因此設計好時鐘電路是保證達到整個電路電磁兼容的關鍵。關于時鐘電路的布局,有以下注意事項:

(1)不要采用菊花鏈結構傳送時鐘信號,而應采用星型結構,即所有的時鐘負載直接與時鐘功率驅動器相互連接。

(2)所有連接晶振輸入/輸出端的導帶盡量短,以減少噪聲干擾及分布電容對晶振的影響。

(3)晶振電容地線應使用盡量寬而短的導帶連接至器件上;離晶振最近的數字地引腳,應盡量減少過孔。

-

電路

+關注

關注

173文章

6024瀏覽量

174784 -

PCB設計

+關注

關注

396文章

4793瀏覽量

89838 -

emc

+關注

關注

172文章

4148瀏覽量

186475

原文標題:20180813---常用電路EMC設計攻略

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PCB疊層EMC規劃與設計思路

PCB設計中EMC/EMI的仿真

在PCB的EMC設計時,你真的考慮周全了嗎?(附六層板設計案例)

PCB設計考慮EMC的接地技巧

PCB如何設計EMC效果才會最優?

PCB如何設計才能發揮EMC最優效果?

從EMC角度考慮常用電路設計及PCB設計

從EMC角度考慮常用電路設計及PCB設計

評論