基于砷化鎵集成無源器件(Integrated Passive Device,IPD)工藝,研制出了一款性能優良的K波段發夾型帶通濾波器芯片,測試結果表明:在19.5~21.3 GHz頻帶內,該芯片濾波器的插入損耗<2.6 dB,最小插入損耗為20 GHz處2.2 dB, 帶內輸入輸出回波損耗<-25 dB,群時延波動<50 ps, 測試結果與仿真設計十分吻合。該濾波器尺寸僅為2.96 mm×1.8 mm×0.1 mm,相比傳統工藝的微波濾波器,體積大大縮小,符合當前通信、雷達等微波系統中器件小型化的發展趨勢,具有廣闊的應用前景。

0 引言

隨著當代半導體工藝與器件的日趨改善與進步,得益于系統級封裝(System In Package,SIP)的集成架構與設計思路,當代雷達、通信、電子戰等微波系統朝著小型化、高密度集成、高可靠性、低成本等方向發展,因此對微波系統中器件與模塊提出了更高的要求。

微波濾波器作為微波系統中重要的無源器件,在射頻前端應用廣泛,其各項指標很大程度地影響著微波系統的整體指標。在(亞)毫米波頻帶的實際工程應用中,PCB、LTCC、腔體等傳統工藝制造的濾波器[1-3]由于其相對尺寸過大、加工精度、量產一致性及難以與系統集成等問題已無法滿足當代微波系統小型化與高性能的要求,而當前采用體聲波和聲表面波技術的MEMS濾波器[4-5]雖然擁有較小的尺寸和不錯的量產能力,但是由于材料與工藝的限制,其實際應用的頻段目前主要在C波段以下,無法滿足更高頻率的微波系統的需求。

GaAs作為第二代半導體材料,采用GaAs襯底的高電子遷移率晶體管(High Electron Mobility Transistor,HEMT)等有源工藝制造的如功放、移相器等有源芯片早已大量應用在各軍用及民用微波系統中。在無源器件的實現上,得益于GaAs襯底極低的介質損耗(為萬分之一量級)和微電子工藝制程,采用GaAs襯底IPD工藝制造的如濾波器、功分器、耦合器等器件具有較高的性能與加工精度、較小的體積、優秀的量產一致性,因此十分適合于微波毫米波系統中的大規模應用。

本文則是基于國內某GaAs IPD工藝線,研制出了一款K波段帶通芯片濾波器,體積僅為2.96 mm×1.8 mm×0.1 mm,比原有采用傳統工藝制造的器件,體積縮小了約80%,實現了無源器件的小型化,其相應的性能指標完全滿足系統需求。

1 工藝簡介

為了使微波無源器件在GaAs襯底上集成,本項目的IPD工藝使用先進和高成品率的微電子制造過程,其工藝典型的無源器件的襯底模型示意圖如圖1所示。

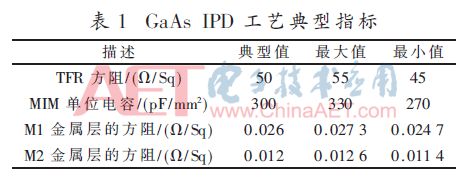

圖1中底部的100 μm的GaAs為整個集成無源器件的襯底介質,再通過若干如光刻、顯影、濺射、剝離、金屬蒸鍍、刻蝕等微電子工藝即可在襯底上面形成一系列的金屬、電介質、過孔等多層結構,可形成不同的基本無源元件如MIM(Metal-Instric-Metal)電容、螺旋電感、TFR(Thin Firm Resistor)電阻等,該IPD工藝的典型參數指標如表1所示。

2 帶通濾波器設計

2.1 耦合矩陣綜合

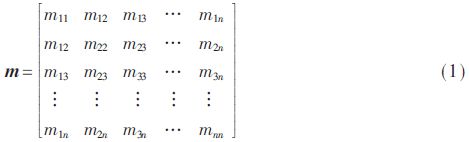

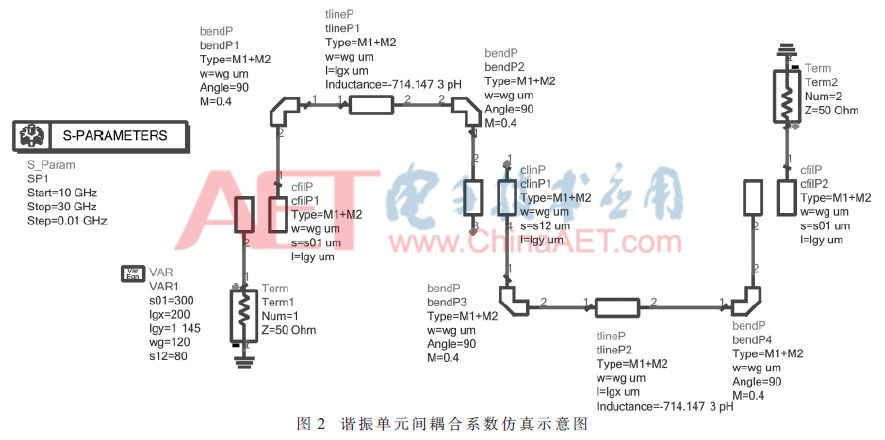

根據濾波器耦合矩陣的理論[6],無論何種結構的微波濾波器,其電特性參數由其耦合系數矩陣m和外部品質因素QE所決定,n階濾波器的典型廣義耦合矩陣如式(1)所示:

因為濾波器為互易無源器件,所以式(1)的濾波器廣義耦合矩陣是對稱的,其中mii為各個諧振器頻率的相對偏移,對于同步調諧的濾波器來說,mii=0;mij為諧振器間的互耦合系數,其與耦合強度成正相關關系,決定了濾波器的相對帶寬大小。實際應用中,需要將廣義耦合矩陣通過式(2)轉換成狹義耦合矩陣:

式中,f0為濾波器的中心頻率,BW為濾波器的帶寬。結合實際項目中對濾波器的指標要求:中心頻率為20.4 GHz、帶寬大于1.8 GHz,并需要較高的帶外抑制,擬采用5階契比雪夫響應的形式來實現,結合CoupleFil濾波器矩陣綜合軟件和式(2)可以確定該濾波器的狹義耦合矩陣如式(3)所示。

2.2 電路原理圖設計

2.2.1 諧振單元的確定

在確定了濾波器的狹義耦合矩陣和外部品質因素后,需進行具體的電路設計。根據微波濾波器基本理論知識[6],可采用1/2介質波長的開路微帶線作為基本諧振單元,為了減小濾波器的插入損耗即需要提高單個諧振器的Q值,微帶線損耗即影響諧振器Q值的主要因素為其導體損耗,導體基本的電阻計算公式為:

式中,ρ為導體的電阻率,L為導體長度,h和w分別為導體橫截面的厚度和寬度。可知在導體電阻率e和長度L確定的條件下,要想減小微帶線的導體損耗主要有兩種方法:第一種方法就是增加導體的厚度,結合本IPD的工藝特性,可選擇M1+M2兩層導體(其中M1層厚1 μm,M2層厚2 μm)同時走線方式,即將M1與M2層之間的SiN刻蝕后金屬化填充,使總導體厚度達到該工藝目前的3 μm的最大值;第二種方法則是增加導體的寬度,結合Txline軟件可計算出在頻率20.4 GHz處,100 μm厚的GaAs襯底上的特征阻抗為50 Ω,半波長的微帶線的寬度和長度分別約為70 μm和2 600 μm。因此在實際設計中考慮采用寬度更大即特抗阻抗更低的微帶諧振器作為諧振器單元,為了節約版圖面積即實現濾波器的小型化,將微帶開路諧振單元設計成U型的發夾結構。

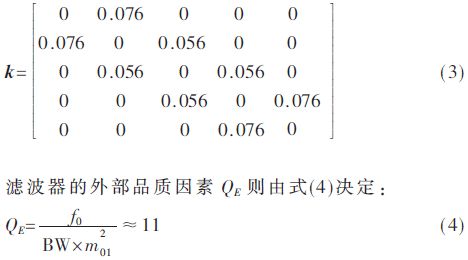

2.2.2 耦合系數的仿真

在確定了濾波器基本諧振單元的尺寸后,需要根據狹義耦合系數矩陣和外部品質因素來綜合出各個諧振器間的實際物理尺寸,發夾型微帶諧振器單元間主要通過縫隙耦合,以1和2諧振單元為例,諧振器間的耦合系數仿真示意圖如圖2所示。

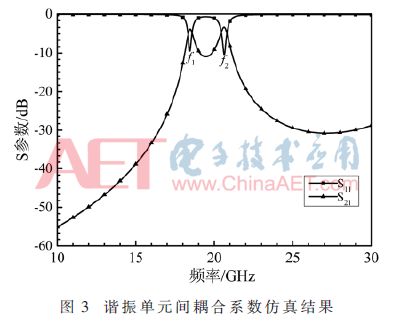

影響發夾諧振器間耦合系數的因素即為兩個發夾諧振單元的縫隙(即如圖3中的S21變量),仿真初值為80 μm,仿真結果如圖3所示。

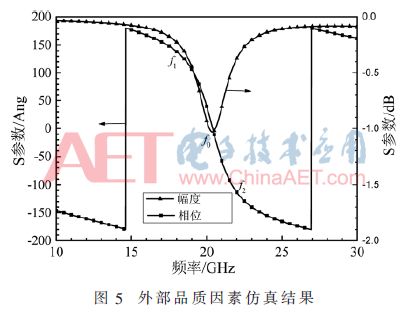

從圖3的S參數仿真結果可知,其仿真曲線有兩個諧振尖峰點f1和f2,分別為18.46 GHz和20.62 GHz。為了使源和負載耦合效應對諧振單元間耦合的影響最小化,仿真過程中盡可能加大圖中源端和負載端微帶與諧振單元間的縫隙(即圖3中的S11變量),使得兩個諧振尖峰頻率不隨S11變量的變化而變化為止。諧振器間耦合系數的綜合近似公式為:

根據圖3的仿真結果和式(6),對比式(3)的狹義耦合矩陣,可知其耦合系數比理想值偏大,耦合過強,因此要適當增加兩個諧振單元的縫隙以降低兩者的耦合強度。由于本濾波器采用輸入輸出完全對稱的結構,同理只需再對諧振器2和3之間進行仿真,調節兩者間的耦合系數,以滿足理論的耦合系數值,即可得到5個諧振單元間縫隙大小的初值。

2.2.3 外部品質因素的仿真

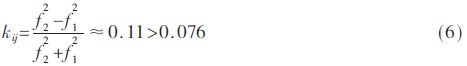

在確定完各諧振單元間的耦合縫隙大小即耦合系數后,需要通過改變濾波器輸入輸出饋電位置來調節其外部品質因素的大小,外部品質因素原理圖仿真示意圖如圖4所示。

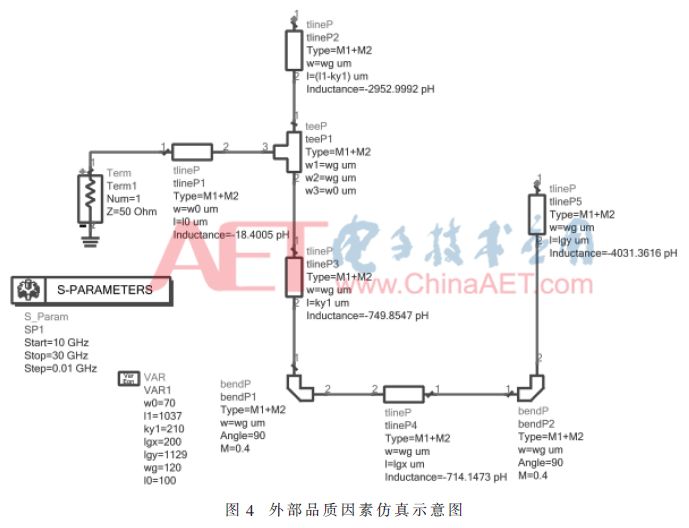

在諧振單元確定的情況下,采用特征阻抗50 Ω即寬度為70 μm的微帶線進行直接饋電,其外部品質因素由圖4中的ky1參量即饋電點距離發夾諧振器底部的距離來決定,圖4的仿真結果如圖5所示。

圖5中f0為單個發夾型諧振器的諧振頻率即20.38 GHz,f1和f2分別為S11相位與諧振頻率點處相差±90°的兩側頻點,分別約為19.31 GHz和21.45 GHz,頻域法的外部品質因素估算公式為:

即外部品質因素約等于諧振點處頻率f0除以兩側與f0相位各相差90°頻點的差值,圖5中ky1等于210 μm時,計算得出的Qe為9.5要小于理論值的11。因此需要進一步調節饋電點的位置,即ky1的值以滿足初步理論的指標要求,最終各參數的值見下文。

2.3 版圖的仿真與設計

由于上節基于原理圖和耦合矩陣理論提取的初步尺寸只是針對單個或兩個諧振器而言的,而忽略了其他諧振單元耦合效應的影響, 同時原理圖相對簡單的電路級仿真已無法準確地預測K波段下的電磁場結果,原理圖仿真的尺寸參數只能作為版圖設計的參考初值,與最終實際物理尺寸可能存在一定甚至是較大的偏差。因此鑒于GaAs IPD工藝具有精準的電磁(EM)仿真模型,在上節綜合出濾波器各單元結構的初步尺寸后,可直接根據該IPD的工藝設計規則和模型進行基于Momentum的芯片濾波器整體版圖仿真與設計。

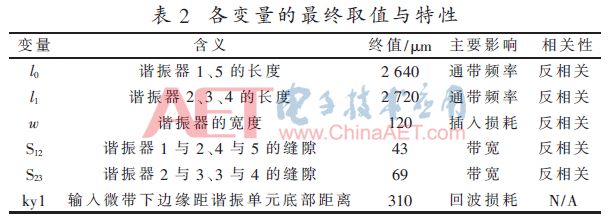

版圖設計時主要需參考整體原理圖的仿真結果和耦合矩陣理論,對影響濾波器性能的主要參數即各諧振器的長度(l)、寬度(w)、諧振單元間的耦合縫隙(S12和S23)、輸入輸出饋電點的位置(ky1)進行調節,進而找到上述變量對濾波器的插損、帶寬、通帶范圍等特性影響的變化趨勢,并且需在芯片尺寸與整體性能做出一定的折中,這是一個不斷迭代的過程,最終上述各參數調節后的取值及對濾波器特性主要影響關系見表2。

最終流片的版圖如圖6所示,芯片尺寸為2.96 mm×1.8 mm×0.1 mm。

3 實物與測試結果

其他微電子工藝如Si CMOS、GaAs HEMT等有源芯片的流片時間長達3~5個月,而基于GaAs IPD工藝的無源MMIC由于其日趨成熟穩定的工藝與純無源結構,具有較快的流片周期,典型的流片時間僅為20天,十分符合現代快速的科研生產需求。最終本文研制的小型化K波段帶通濾波器芯片實物如圖7所示。

濾波器芯片采用Keysight公司的N5247A矢網和Cascade公司的ACP系列的GSG-150探針進行測試,實測與仿真結果對比如圖8所示。

從圖8可知,該濾波器芯片實測與仿真結果吻合度很好,驗證了該工藝模型的準確性。圖8(a)的S參數測試結果表明,在通帶19.5-21.3 GHz內,其插入損耗最小值約2.2 dB,最大值2.6 dB,回波損耗小于-25 dB,匹配效果十分良好,其在帶外15.5 GHz與26.8 GHz處的帶外抑制已達到50 dB。圖8(b)群時延測試結果表明,該濾波器的帶內群時延約為360~405 ps,群時延波動小于50 ps,具有很好的相位響應。

為了驗證IPD工藝的穩定與一致性,隨機抽取本次流片的5塊芯片分別進行單獨測試,最終各芯片測試結果如圖9所示。

從圖9可知,隨機抽取的各濾波器芯片的測試結果十分吻合,難以辨別出測試結果的差異,進而證明了該工藝的成熟與穩定,十分符合對于一致性要求較高的批量化應用。

4 結論

本文設計并實現了一款基于GaAs IPD微電子工藝的發夾型K波段帶通濾波器芯片,該濾波器擁有優良的性能和一致性,且相比采用傳統LTCC、薄膜、PCB工藝研制的濾波器,體積大大減小,實現了器件的小型化,目前已代替傳統濾波器在某毫米波通信項目中直接應用,該GaAs IPD工藝也為今后微波毫米波系統中其他無源器件的小型化指明了一個新的方向。

-

濾波器

+關注

關注

161文章

7873瀏覽量

179057 -

GaAs

+關注

關注

2文章

510瀏覽量

23107 -

IPD

+關注

關注

4文章

83瀏覽量

26653

原文標題:【學術論文】基于GaAs IPD的K波段芯片濾波器

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

P波段腔體濾波器的小型化設計

濾波器設計資料集錦

X波段微帶帶通濾波器的設計介紹

L波段發夾型微帶濾波器的設計

詳解FIR濾波器和IIR濾波器的區別

基于橢圓函數的LC帶通濾波器設計與仿真

一種新型小型化K波段帶通濾波器的設計解析

高通正式推出了ultraSAW濾波器

正交鏡像濾波器的詳細資料介紹

如何實現一種UHF波段帶通濾波器的設計資料說明

基于GaAs IPD的K波段濾波器芯片的設計資料分析總結

基于GaAs IPD的K波段濾波器芯片的設計資料分析總結

評論