摘要:

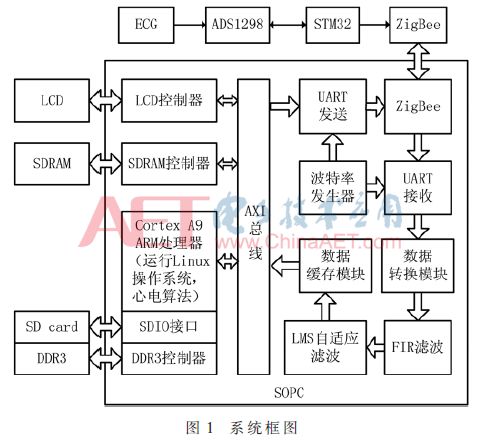

針對家用心電監護系統的需求,設計了一種基于SOPC的多導聯ECG實時監測系統。系統以ADS1298為心電信號采集前端,通過ZigBee將多個導聯的心電數據發送到后端處理。系統后端采用內嵌了ARM Cortex A9雙核處理器的FPGA,并在ARM上搭建了

Linux開發環境。在FPGA中通過并行處理、流水線設計和自定義IP核實現對心電數據的接收、格式轉換、FIR濾波、LMS自適應陷波和數據緩存;在ARM上實現了QRS檢測算法、心率變異性分析和心梗檢測算法,并通過SD卡和LCD屏實現心電數據的長時間存儲及心電波形與診斷結果的實時顯示。

目前,心血管疾病的發病率迅速上升,已經成為威脅人類身體健康的主要因素之一。常規的心電監護儀需要患者在有限時間內,到固定的醫療場所進行監護診斷,無法滿足患者長期實時監護的需求,因此家用心電監護儀在人們的生活中發揮著越來越重要的作用[1]。現今,絕大多數的家用心電監護儀或是通過采集電路,將心電數據經互聯網發送到醫院監護中心進行遠程監護[2-3],或是實現多體征參數的監護,計算心率,畫出波形等[4]。這些都沒有對復雜的心血管疾病進行實時分析診斷。因此本文提出了一種針對家用的、可對心血管疾病實時分析診斷的心電監測系統。

本文使用內嵌了ARM Cortex A9雙核處理器的FPGA,其運算處理能力強,可實時分析處理心電數據。通過軟硬件協同設計,在ARM上實現了難以硬件化的QRS檢測算法,心率變異性分析和基于卷積神經網絡的心梗檢測算法;在FPGA中實現FIR濾波器和LMS自適應陷波及數據緩存,減輕ARM處理負擔,提高數據處理效率。

基于SOPC的多導聯ECG監測系統框架如圖1所示,系統包括心電信號采集前端和心電數據處理后端兩部分,兩者之間通過ZigBee進行數據傳輸與控制。

2.1 心電信號采集前端

為了達到心電信號采集前端便攜化的目的,使用了TI公司推出的專門針對ECG信號采集的ADS1298芯片。ADS1298內部集成了8通道24位帶符號的模數轉換模塊,分別用來測量I、Ⅱ導聯及V1~V6的6個胸導聯信號[5]。根據這8個導聯的信號經過一定的運算處理可得到十二導聯心電信號[6]。其采樣頻率可在250 S/s~32 kS/s之間。

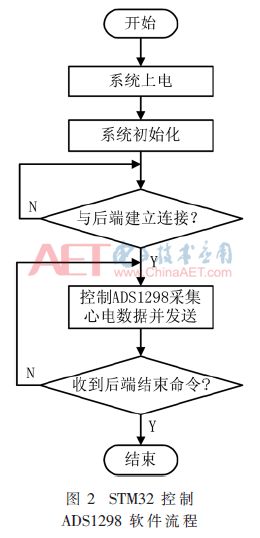

系統通過AgCl電極片拾取心電信號,ADS1298每完成一次采樣轉換,STM32控制ZigBee模塊將所用到的導聯的心電數據發送到心電數據處理后端。其軟件控制流程如圖2所示。

2.2 無線傳輸模塊

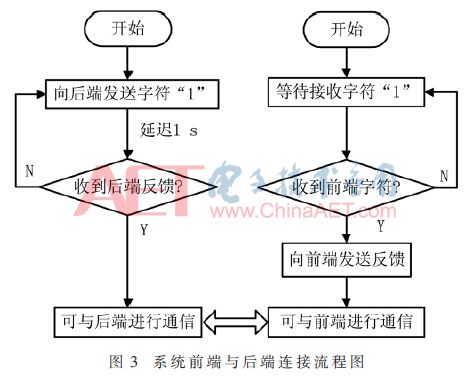

本系統使用UART接口的ZigBee模塊。雖然ZigBee傳輸距離較短,速率慢,但由于系統AD采樣速率較低,并且針對家用,傳輸距離限于幾十米范圍,再加上ZigBee功耗低,因此ZigBee滿足設計要求[7]。首先系統上電后要檢測前端與后端是否建立連接。圖3所示為判斷是否建立連接流程。

2.3 心電數據處理后端

心電數據處理后端的主要任務是通過FPGA與ARM完成對心電數據的預處理與算法處理。

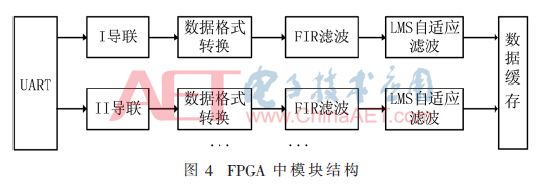

FPGA中設計結構如圖4所示。用多路并行處理的方式處理心電數據,且每一路的設計遵從流水線的設計思路,提高系統處理速度,實現實時處理。

2.3.1 UART模塊

為靈活接收ZigBee的數據并將數據傳送到后端處理,本系統在FPGA中用Verilog采用有限狀態機的方式實現了UART接口。

2.3.2 數據格式轉換模塊

由于FIR濾波與LMS自適應濾波均為浮點數運算,因此該模塊的主要功能是將心電采集前端發送的24位整型數據轉換成對應的32位浮點型數據。其結構如圖5所示。

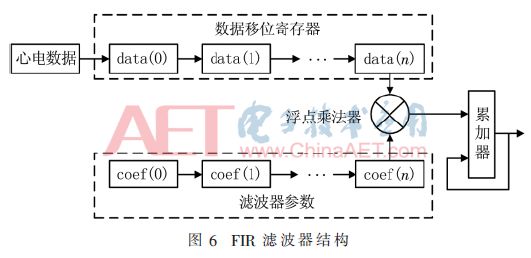

2.3.3 FIR濾波模塊

從心電采集前端發送的心電數據中有由呼吸引起的基線漂移,其頻率在0.5 Hz左右[8],因此設計了截止頻率為0.5 Hz的FIR高通濾波器。經測試,1 000階濾波器效果較好。

FIR濾波器本質上是卷積運算,僅涉及移位、相乘、累加運算。在MATLAB中設計得到的濾波器系數均為浮點數,因此采用Altera自帶的浮點乘法器與浮點加法器IP核。考慮到濾波器的階數為1 000階,因此采用串行結構且只用一個浮點乘法器與浮點加法器。經計算,完成移位、1 001次乘法、1 000次加法需占用9 000個時鐘周期左右。而系統時鐘為50 MHz,可得該模塊吞吐率可達160 kb/s。心電信號的采樣率為250 Hz,所以該FIR濾波器可實時處理心電數據。圖6所示為FIR濾波器的具體結構。該模塊對FPGA資源占用率為2%。

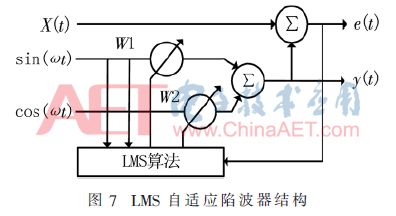

2.3.4 LMS自適應濾波器

前端心電采集系統發送的心電數據中有較嚴重的50 Hz工頻干擾,所以設計了基于LMS算法的自適應陷波器[9],抑制輸入信號中的工頻干擾。

基于LMS算法的自適應陷波器結構如圖7所示。其中X(t)是含有干擾信號的輸入信號,干擾信號頻率為ω,由于干擾信號的幅值與相位未知,因此提供兩個相互正交的單頻信號sin(ωt)與cos(ωt),通過調整權值來合成與干擾信號相同的信號,將輸入信號與合成的干擾信號作差就可得到有用信號。

LMS自適應陷波器所涉及的運算僅為乘法和加法,且都為浮點運算,為節省FPGA資源,使用一個浮點乘法器和加法器。經計算,按照此種方法,該模塊的吞吐率可達16 Mb/s,可實時處理心電數據。該模塊對所用FPGA資源占用率為2%。

2.3.5 基于自定義IP核的數據緩存模塊

為提高ARM的處理效率,以自定義IP核形式設計了數據緩存模塊將心電數據存儲到片外的SDRAM中,之后由ARM讀取SDRAM中的數據作算法處理。本系統ARM與FPGA之間通過AXI總線進行數據交換。

數據緩存模塊的實現是基于Altera的Qsys硬件平臺。在Qsys中添加SDRAM Controller,通過FPGA和ARM分別對SDRAM Controller的控制,來完成對片外SDRAM的讀寫。SDRAM Controller是基于Avalon總線實現的Avalon從端口。因此在FPGA中實現對SDRAM Controller的控制是通過遵循Avalon總線傳輸協議編寫一個Avalon主端口。然后將該Avalon主端口模塊例化為自定義IP核添加到Qsys中,便可實現在FPGA中對SDRAM Controller的控制。ARM則通過AXI總線完成控制。

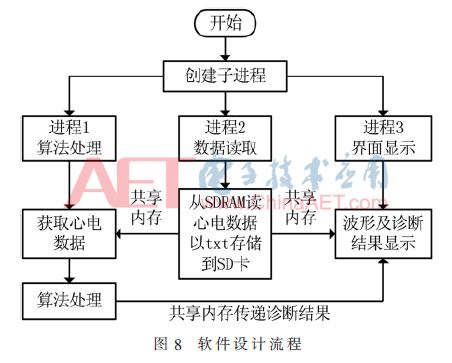

2.3.6 ARM處理平臺

嵌入式ARM硬核為雙核,且主頻可達925 MHz,運算能力強,可實時處理心電數據。在ARM上構建了Linux操作系統,編程方式采用多任務編程,通過創建多個進程分別完成心電數據的讀取,實現難以硬件化的心電檢測算法,控制各模塊之間協調工作,將心電數據以txt文件格式存儲到SD卡當中,以及在LCD屏上顯示心電波形和診斷結果。各進程之間通過共享內存的方式實現數據交互。圖8所示為軟件設計流程。

3.1 占用資源情況

系統總導聯數為5導聯,采樣率為250 Hz。在友晶DE1-SoC開發板上運行,FPGA總資源占用情況如表1所示,占用資源在系統限度內。

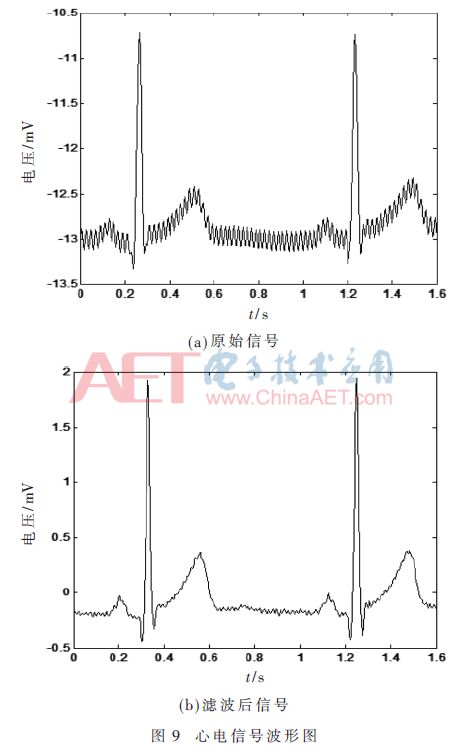

3.2 ECG信號提取測試

圖9(a)是心電前端采集系統采集的原始心電信號波形,有明顯的基線漂移和較大的工頻干擾。圖9(b)為從系統SD卡中得到的經過FPGA濾波處理的心電圖,可看到基線漂移被明顯濾除,且50 Hz工頻得到有效抑制。

3.3 系統測試

被測者身心狀況良好。圖10為液晶屏的顯示,可實時顯示心電波形及診斷結果。圖中下方左邊Heart Rate顯示心率為69,正常;下方中間status顯示正常心電信號(Norm)或是有心肌梗死前兆,圖中顯示的為Norm即正常心電信號;SDNN和NN50顯示心率變異性結果,其中SDNN為0.133在正常范圍(0.141±0.039 s)內,NN50顯示30 s內相鄰心跳間期的差值超過50 ms的心跳個數,為11個。

3.4 心電算法的實現

本系統實現了課題組前期QRS檢測算法[10],通過計算RR間期,可計算心率值。在此基礎上本文進行了額外的心率變異性分析,從而輔助心血管疾病的預防。包含兩個方面:(1)SDNN:全部心跳間期的的標準差,正常情況下該值一般在0.141±0.039 s的范圍內[11]。(2)NN50:心電信號中所有每對相鄰心跳間期的差值超過50 ms的心跳個數,數值越大表明心率變異性也越大[12]。

本系統也實現了課題組前期的基于V2、V3、V5、aVL導聯和卷積神經網絡的心梗檢測算法[13],該算法可達到總體96%的準確率。通過將在PC上離線訓練好的卷積神經網絡移植到SOPC平臺,實現對心梗疾病的診斷。

本文提出了一種基于SOPC的多導聯ECG實時監測系統,可以實現對心電信號的采集和無線傳輸,并在SOPC平臺上進行實時數字濾波、算法分析診斷以及診斷結果和心電波形的顯示。實驗表明,本系統可以很好地采集人體心電信號,經處理后可得到良好的心電波形,并借助ARM處理器對心電數據實時算法分析,實現心電疾病的診斷。

-

sopc

+關注

關注

2文章

248瀏覽量

63432 -

神經網絡

+關注

關注

42文章

4814瀏覽量

103616 -

監測系統

+關注

關注

8文章

2884瀏覽量

82521

原文標題:【學術論文】基于SOPC的多導聯ECG實時監測系統

文章出處:【微信號:ChinaAET,微信公眾號:電子技術應用ChinaAET】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

DSP的EASI十二導聯多功能Holter系統

基于ADAS1000系列的12導聯ECG測量系統

心電圖(ECG)設計如何防止ECG子系統受到各種外部和環境輻射影響

基于SOPC的紅外實時成像系統的研制

一種基于SOPC的多導聯ECG實時監測系統

一種基于SOPC的多導聯ECG實時監測系統

評論