一、引言

隨著半導體技術的飛速發展,具有圖像功能的嵌入式應用愈來愈多。從數碼相機、可視電話、多功能移動電話等消費產品到門禁、數字視頻監視等工業控制及安防產品,圖像采集和處理已成為重要的組成部分之一。圖像采集需要進行同步信號的處理,比通常的A/D數據采集過程復雜,電路的設計也較為困難。傳統PC上的圖像采集卡都是在Philips、Brooktree等半導體公司提供的接口芯片基礎上,由專業公司開發生產。在嵌入式系統中不同的處理器和圖像傳感器的信號定義及接口方式不同,沒有通用的接口芯片。另外,利用系統中的現有資源設計圖像采集電路,可以減少器件數量、縮小產品體積和降低系統成本。所以,通常嵌入式系統中要求自行設計圖像采集接口電路。本文針對不同采集速度的要求,提出了兩種圖像采集接口電路的設計方法。

目前市場上主流的圖像傳感器有CCD、CMOS兩種器件,其中CMOS器件上世紀90年代產生,近年來得到了迅速發展。傳感器的輸出有模擬和數字兩種。由于CMOS器件功耗小、使用方便,具有直接數字圖像輸出功能,作者在設計時選用了CMOS數字輸出圖像傳感器件。其他方式器件的接口設計與此類似,將在討論中說明。

本文內容做如下安排:第二部分簡述圖像信號的特點;第三、四部分分別介紹I/O和內存直接寫入兩種接口設計方法;最后部分是討論。

二、圖像信號介紹

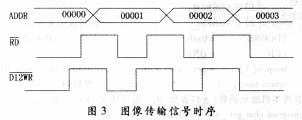

圖1給出了采樣時鐘(PCLK)和輸出數據(D)之間的時序關系。在讀取圖像數據時用PCLK鎖存輸出數據。除采樣時鐘(PCLK)和數據輸出(D)外,還有水平方向的行同步信號(HSYNC))和垂直方向的場同步信號(VSYNC)。對于隔行掃描器件,還有幀同步信號(FRAME)。如圖2,一幀包括兩場。圖2中窄的矩形條是同步脈沖,同步脈沖期間數據端口輸出的數據無效。

PLCK存在時,圖像數據端口連續不斷地輸出數據。由于行之間以及場之間輸出數據無效,在采集圖像數據必須考慮同步信號,讀取有效數據才能保證圖像的完整性。

三、I/O接口設計

對于MCU、DSP處理器,I/O是最方便的訪問方式之一。以I/O方式讀取圖像數據不僅可以簡化電路設計,而且程序也很簡單。但由于讀取每一個像素都要檢測狀態,在處理器速度低的情況下,讀取圖像慢。在處理器速度快或圖像采集速度要求不高的應用中,I/O接口方式是一個較好的選擇。

1、電路原理和結構

在圖像傳感器和處理器之間,利用兩個鎖存器分別鎖存狀態和圖像數據,處理器通過兩個I/O端口分別讀取。圖3中,在采樣時鐘的上升沿數據鎖存器保存傳感器輸出的圖像數據,當處理器通過I/O口讀取圖像時,數據鎖存器輸出數據。其它情況下,鎖存器輸出處于高阻狀態。處理器通過狀態鎖存器讀取同步信號和圖像就緒(Ready)指示信號。在數據鎖存器保存圖像數據的同時,狀態鎖存器產生Ready信號(從‘0’到‘1’)。處理器讀取圖像數據時,Ready信號自動清除(從‘1’到‘0’)。處理器讀取狀態時鎖存器驅動總線,其他情況下輸出處于高阻狀態。

2、圖像讀取流程

要保證圖像的完整性就必須從一場圖像的第一行開始讀取,對于隔行掃描輸出的圖像則必須從一幀的第一行開始讀取。讀取每行圖像數據時,則從該行的第一個像素開始。因此,在讀取圖像數據前應先判斷場和行的起始位置。圖4是通過I/O接口方式讀取圖像數據的流程。讀取每個像素數據前先查詢數據狀態,如果數據已準備好則讀取數據。

3、同步信號檢測

為了簡化電路設計,用處理器直接讀取同步信號,然后找出場和行的起始位置。

從圖2可以看出,處理器讀取同步信號時,信號可能處在同步脈沖狀態(‘1’)或正常狀態(‘0‘)。對于那些同步信號反向的器件,則分別為‘0’和‘1’。如果信號處于同步脈沖狀態,第一次檢測到的正常狀態就起始位置。如果信號處于正常狀態,則首先檢測到脈沖狀態,然后用同樣的方法確定起始位置。

通過上述方法可以檢測出場的起始位置和行起始位置。

4、用VHDL設計鎖存器

在應用中,以上兩個鎖存器的功能和其他邏輯集中在一起,用可編程邏輯器件實現。下面分別為它們的VHDL表示。

設DO(0-7)是鎖存器輸出端,DI(0-7)是鎖存器輸入端,DM(0-7)是中間狀態,Data_R是數據讀信號(低電平時有效),則數據鎖存器的VHDL描述為:

Process (reset, PCLK) -- 鎖存圖像數據

Begin

If reset=‘0’ then

DM《=“00000000”; -- 清除數據

Else if PCLK‘event and PCLK=’1‘ then

DM《=DI; -- 鎖存數據

End if;

End process;

Process (DM, Data_R) -- 讀取圖像數據

Begin

If Data_R=’0‘ then

DO《=DM; -- 輸出圖像數據

Else

DO《=“ZZZZZZZZ” -- 輸出高阻

End if;

End process;

進一步設數據有效狀態為Dstatus, 狀態讀寫信號為Status_R (低點平時有效),則狀態鎖存器的VHDL描述為:

Process (reset, PCLK,Data_R) -- 數據有效狀態控制

Begin

If reset=’0‘ or Data_R=’0‘ then

Dstatus《=’0‘; -- 清除狀態

Else if PCLK’enent and PCLK=‘1’ then

Dstatus《=‘1’; -- 設置狀態

End if;

End process;

Process (Dstatus, Status_R) --讀取狀態和同步信號

Begin

If Status_R=‘0’ then

DO0《=Dstatus;

DO1《=VSYNC;

DO2《=HSYNC;

DO3《=FRAME;

Else

DO《=“ZZZZZZZZ”; -- 高阻狀態

End if;

End process; [page]

四、內存直接寫入接口設計

在處理器速度較慢且圖像數據輸出的頻率不能降低的情況下,采用上述I/O接口方法不能得到完整的圖像。另外,有些應用中要求能夠實時采集圖像。為此,我們設計了高速數據圖像采集方法?內存直接寫入法。由于SRAM訪問控制簡單,電路設計方便,被大量嵌入式系統采用,本文以SRAM作為存儲器。

1、電路原理和結構

內存直接寫入方法通過設計的圖像采集控制器(以下簡稱控制器)不需處理器參與,直接將圖像數據寫入系統中的內存中,實現高速圖像采集。

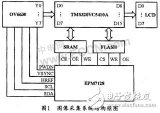

圖5是接口結構圖,當需要采集圖像時,處理器向控制器發出采集請求,請求信號capture_r從高到低。控制器接到請求脈沖后,發出處理器掛起請求信號HOLD,使處理器的外總線處于高阻狀態,釋放出總線。控制器收到處理器應答HOLDA后管理總線,同時檢測圖像同步信號。當檢測到圖像開始位置時,控制器自動產生地址和讀寫控制信號將圖像數據直接寫入內存中。圖像采集完成后,控制器自動將總線控制權交還處理器,處理器繼續運行,控制器中與采集相關的狀態復位。控制器可以根據同步信號或設定的采集圖像大小確定采集是否完成。

在圖5中,控制器包括同步信號檢測、地址發生器、SRAM寫控制器、總線控制器和處理器握手電路等主要部分。同步信號檢測確定每一場(幀)和每一行的起始位置;地址發生器產生寫SRAM所需的地址;SRAM寫控制器產生寫入時序;總線控制器在采集圖像時管理總線,采集完成后自動釋放;處理器握手電路接受處理器命令、發總線管理請求和應答處理器。

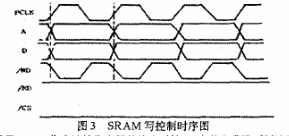

2、SRAM寫控制時序

采集圖像過程中,控制器自動將數據寫入到硬件設定的內存中。寫內存時,控制器產生RAM地址(A)、片選信號(/CS)、讀信號(/RD)和寫信號(/WD),同時鎖存傳感器輸出的數據并送到數據總線(D)上。每寫入一個數據后,地址(A)自動增1。采集時/CS保持有效(‘0’)狀態而/RD處于無效狀態(‘1’)。地址A的變化必須與/WD和數據鎖存器協調好才能保證圖像數據的有效性。

圖6是控制器產生的SRAM信號時序圖。用PCLK作為地址發生器的輸入時鐘,且在其上升沿更新地址值。同樣,在PCLK的上沿鎖存數據并輸出到總線上。將PCLK反相,作為/WD信號,使得在/WD的上升沿地址和數據穩定,確保寫入數據的有效性。

3、控制器主要功能的VHDL描述

描述控制器中全部功能的VHDL代碼較長,而且有些部分是常用的(如計數器等)。圖像采集狀態產生和同步信號的檢測是其中重要的部分。下面介紹這兩部分的VHDL描述。

圖像采集狀態 capture_s:

處理器的采集請求信號capture_r使capture_s從‘0’到‘1’,場地址發生器(計數器)的溢出位vcount_o,清除capture_s。

process (capture_r, reset, vcount_o)

begin

if reset=‘0’ or vcount_o=‘1’ then

capture_s《=‘0’; -- 清除

else if capture_r‘event and capture_r=’0‘ then

capture_s《=’1‘; -- 置狀態位

end if;

end process;

同步信號檢測:

只有在采集狀態capture_s有效時(‘1’)才檢測場同步信號,場同步信號下降沿置場有效狀態(vsync_s),場地址發生器溢出位vcount_o清除場有效狀態。只有在vsync_s有效情況下才檢測行同步信號,行同步信號下降沿置行有效狀態(hsync_s),行計數器溢出信號hcount_o清除行狀態。只有在行狀態有效的情況下計數器才工作,且將數據寫入RAM。

Process (capture_s,reset,vcount_o, vsync)

Begin

If reset=’0‘ or vcount_o=’1‘ or capture_s=’0‘ then

Vsync_s《=’0‘; -- 清除

Else if vsync’event and vsync=‘0’ then

Vsync_s《=‘1’; -- 置狀態位

End if;

End process;

Process (vsync_s, reset, hcount_o, hsync)

Begin

If vsync_s=‘0’ or reset=‘0’ or hcount_o=‘1’ then

Hsync_s《=‘0’; -- 清除

Else if hsync‘event and hsync=’0‘ then

Hsync_s《=’1‘; -- 置狀態位

End if;

End process;

五、討論

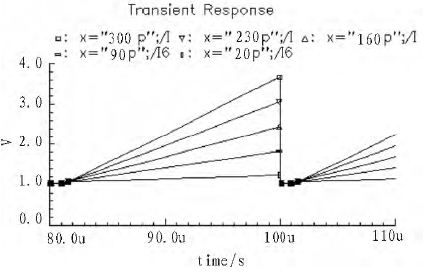

我們在基于TI公司的TMS320C3X系列DSP開發的嵌入式指紋圖像處理模塊中分別用上述兩種方法成功實現了指紋圖像的采集。

采用I/O接口方式最關鍵的是要求處理器的頻率遠高于圖像數據輸出的頻率。例如,如果處理的指令周期為20ns,讀取每個數據需要10個指令周期,則數據的輸出頻率不能超過5MHz,它低于一般的CMOS圖像傳感器件最快的數據輸出頻率。例如國內使用較多的OV7610和OV7620,其正常輸出數據頻率為13.5MHz。在應用過程中,通常改變傳感器中寄存器的設置值,降低其數據輸出頻率。

本文選用的是CMOS數字輸出圖像傳感器。對于模擬視頻信號,在設計時應加同步分離和A/D轉換電路。圖像采集的數字接口和邏輯控制與本文相同。

在我們系統中所采集的是單色圖像,如果采集彩色圖像邏輯設計是相同的所不同的只是數據寬度和后期處理方式。

具體應用中可根據需求對上述設計進行修改以滿足不同的要求。

責任編輯:gt

-

CMOS

+關注

關注

58文章

6011瀏覽量

238722 -

接口

+關注

關注

33文章

8990瀏覽量

153641 -

圖像傳感器

+關注

關注

68文章

1979瀏覽量

130686

發布評論請先 登錄

CMOS圖像傳感器的結構及工作原理

新型CMOS圖像傳感器設計

Micron CMOS圖像傳感器

基于I2C控制總線的CMOS圖像傳感器接口電路

基于DSP和CMOS圖像傳感器的實時圖像采集系統的實現方案

基于CMOS數字輸出圖像傳感器件實現圖像采集接口電路的設計

基于CMOS數字輸出圖像傳感器件實現圖像采集接口電路的設計

評論