TMS320DM6437的性能很高,但是開發(fā)的費用卻很廉價,這樣就可以面向更多的市場,主頻600 MHz,32位定點,采用達芬奇(DaVinci(TM))技術(shù)。該器件采用TI第3代超長指令集結(jié)構(gòu)(VelociTI.3)的TMS320C64x+DSP內(nèi)核,主頻可達600 MHz,支持8個8位或4個16位并行MAC運算,峰值處理能力高達4 800MIPS。

DSP的McBSP接口可由內(nèi)部時鐘發(fā)生器或外部器件提供收/發(fā)時鐘信號(CLKR/CLKX)及收/發(fā)幀同步信號(FSR/FSX)。EN_IN、EN_OUT為DSP控制FPGA中McBSP接口的使能信號,它們均與DSP的GPIO相連。當(dāng)EN_IN為高時,F(xiàn)PGA接收DSP的數(shù)據(jù);當(dāng)EN_OUT為高時,F(xiàn)PGA開始向DSP發(fā)送數(shù)據(jù)。

McBSP接口是全雙工串行接口,提供收發(fā)數(shù)據(jù)雙緩沖以處理連續(xù)的數(shù)據(jù)流,并可獨立配置收發(fā)部分,接收和發(fā)送都可使用獨立的幀信號和時鐘源。接收數(shù)據(jù)時,F(xiàn)PGA的數(shù)據(jù)通過McBSP傳到DSP的DRR寄存器中,觸發(fā)McBSP接收同步事件,EDMA將數(shù)據(jù)搬入DSP內(nèi)存。發(fā)送數(shù)據(jù)時,當(dāng)EDMA從DSP內(nèi)存中將數(shù)據(jù)搬入DSP的DXR寄存器時,利用McBSP發(fā)送同步事件,將數(shù)據(jù)傳輸給FPGA。

2 軟件程序設(shè)計

傳統(tǒng)的C6000型DSP對McBSP和EDMA進行操作時,多使用CSL(Chip Support Library)進行編程操作,由于TMS320DM6437不支持CSL,而是改用PSP(Proeessor Support Package),所以對TMS320DM6437 McBSP接口采用PSP提供的McBSP Driver,主要用McBSP Driver提供的LLC層API進行編程。以方便實驗程序的運行。

在很多實踐中實現(xiàn)DSP和FPGA通信時,McBSP所需的幀同步信號以及時鐘信號均由FPGA產(chǎn)生,McBSP發(fā)送過來32 bit的數(shù)據(jù),DSP內(nèi)部采用EDMA方式接收數(shù)據(jù),McBSP接收同步事件觸發(fā)EDMA傳輸。將數(shù)據(jù)放入DSP片內(nèi)二級存儲器的緩沖區(qū),等待DSP處理。為了寫入的數(shù)據(jù)不被覆蓋掉,片內(nèi)二級存儲器緩沖區(qū)采用乒乓緩沖結(jié)構(gòu),就有McBSP發(fā)送同步事件觸發(fā)EDMA傳輸。

2.1 McBSP配置

2.1.1 接收數(shù)據(jù)格式配置

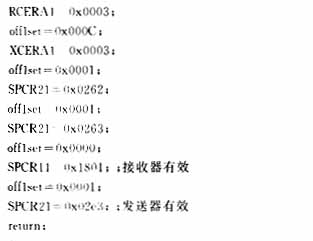

McBSP接收數(shù)據(jù)格式在數(shù)據(jù)結(jié)構(gòu)LLC_RcvDataSetup中設(shè)置,該數(shù)據(jù)結(jié)構(gòu)在McBSP Driver提供的頭文件llc_mcbsp Type.h中定義,在編譯工程文件的時候需包含此頭文件。接收數(shù)據(jù)為單幀數(shù)據(jù),一個數(shù)據(jù)幀長度為4個字節(jié),采用幀同步信號檢測模式,不進行壓縮,數(shù)據(jù)傳輸延遲一個比特,采用McBSP同步事件產(chǎn)生中斷。McBSP發(fā)送數(shù)據(jù)格式在數(shù)據(jù)結(jié)構(gòu)LLC_XmitDatasetup中設(shè)置,具體參數(shù)和接收數(shù)據(jù)格式保持一致。M-cBSP幀同步和時鐘參數(shù)在數(shù)據(jù)結(jié)LLC_mcbspClkSetup中設(shè)置,該結(jié)構(gòu)同樣在頭文件llc_mcbspType.h中定義。

2.1.2 啟動McBSP

首先調(diào)用MeBSP LLC層API對McBSP接口進行設(shè)置,準(zhǔn)備接收FPGA傳輸過來的信號。先調(diào)用函數(shù)LLC_mcbspOpen,該函數(shù)在llc_mcbsp.c中定義,函數(shù)原型為LLC_mcbspOpen(LLC_McbspObj*const pMcbspObj,Uint32InstanceId,Int32*pMcbspParam,CSL_Status*pStatus),所需參數(shù)分別為用戶定義的McBSP通道對象,McBSP通道ID,用戶定義的配置參數(shù)及狀態(tài)信息,返回參數(shù)為指向該通道的句柄hMcbsp。該句話就最為API的函數(shù)。

然后設(shè)置McBSP通道0,調(diào)用函數(shù)LLC_mcbspHwSetup(LLC_McbspHandle hMcbsp,const LLC_McbspHwSetup*setup)。第1個參數(shù)即為剛才返回的指向McBSP通道0的句柄,第2個參數(shù)為一個結(jié)構(gòu)體,包含了前面定義的接收和發(fā)送數(shù)據(jù)結(jié)構(gòu)以及幀同步和時鐘參數(shù)結(jié)構(gòu),這樣就按照實際應(yīng)用的要求完成了對McBSP0通道的設(shè)置。

最后利用函數(shù)LLC_mcbspHwControl使能McBSP接收和發(fā)送功能。函數(shù)原型為LLC_mcbspHwControl(LLC_McbspHandle hMcbsp,LLC_Mcbsp ControlCmd cmd,const void*arg)。第1個參數(shù)為指向McBSP通道0的句柄,第2個參數(shù)為硬件控制命令,第3個為對特定命令的補充說明。開啟McBSP接收發(fā)送功能時,硬件控制命令為LLC_MCBSP_CMD_RESET_CONTROL,使能發(fā)送功能時,命令補充說明為LLC_MCBSP_CTIRL_RX_ENABLE,使能接收功能時,命令補充說LLC_MCBSP_CTRL_TX_ENABLE。

2.2 EDMA配置

2.2.1 EDMA配置原理

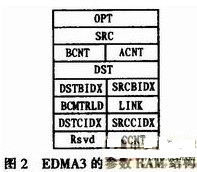

EDMA中傳輸?shù)臄?shù)據(jù)種類有3種:ARRAY,BLOCK,F(xiàn)RAME,分別對應(yīng)3種不同類型的傳輸。首先是一維傳輸,即每一個EDMA事件觸發(fā)的傳輸只傳輸一個ARRAY,該ARRAY所包含的字節(jié)數(shù)由參數(shù)RAM里的參數(shù)ACNT決定。然后是二維傳輸,每一個EDMA事件觸發(fā)傳輸一個FRAME,每個FRAME里包含的ARRAY數(shù)由參數(shù)BCNT決定。就像這樣在類推先去,三維傳輸即每次傳輸一個BLOCK,每個BLOCK里包含的FRAME數(shù)由參數(shù)CCNT決定。這樣的數(shù)據(jù)就更加有嚴(yán)密性。

一個參數(shù)RAM的長度為32個字節(jié)。首先是32 bit的可選參數(shù)OPT,對于可選參數(shù),通過對各個位置0或1設(shè)置事件優(yōu)先級,數(shù)據(jù)單元大小,源地址/目的地址變更模式,傳輸結(jié)束代碼,是否使能傳輸參數(shù)鏈接(LINK)功能,同步傳輸方式等。SRC和DST為EDMA傳輸所需的源地址和目的地址。SRCBIDX和DSTBIDX用于二維傳輸中,表示一個ARRAY的開始到下個ARRAY的開始所跨越的字節(jié)數(shù)。SRCCIDX和DSTCIDX用于三維傳輸中,一個FRAME的開始到下個FRAME的開始所跨越的字節(jié)數(shù)。

在有些日常生活中采用的雙緩沖結(jié)構(gòu),即在DSP緩沖區(qū)內(nèi)開辟2塊緩沖用于并行處理FPGA通過McBSP傳過來的數(shù)據(jù)。當(dāng)EDMA往PingBuffer里傳輸數(shù)據(jù)時,CPU即可處理PongBuffer里的數(shù)據(jù),當(dāng)工作完成后,彼此又交換緩沖區(qū),EDMA往PongBuffer里寫數(shù)據(jù),CPU處理PingBuffer里的數(shù)據(jù)。為了實現(xiàn)雙緩沖結(jié)構(gòu),采用了EDMA提供的LINK功能,即將不同的EDMA傳輸參數(shù)RAM鏈接起來,組成一個傳輸鏈,在傳輸鏈中,一個傳輸?shù)慕Y(jié)束會導(dǎo)致自動從參數(shù)RAM中裝載下一個傳輸需要的事件參數(shù)。在具體程序中,只需將Ping通道的參數(shù)RAM LINK到Pong通道,同時將Pong通道的參數(shù)RAMLINK到Ping通道即可。

2.2.2 EDMA接收數(shù)據(jù)配置實現(xiàn)

在使用EDMA3 Driver之前必須首先對其進行初始化。EDMA3 LLD提供了2個API進行相關(guān)工作。EDMA3_DRV_create和EDMA3_DBV_open。前者用于創(chuàng)建一個EDMA3 Driver對象,后者用于開啟對應(yīng)的EDMA3 Driver通道。

創(chuàng)建并開啟EDMA3 Driver通道后,即可為此通道分配資源以及初始化其配置。首先調(diào)用EDMA3_DRV_requestChannel請求分配一個DMA通道,隨后對該通道的參數(shù)RAM進行配置,以滿足傳輸需要。EDMA3_DRV_setSrcParams用于設(shè)置該EDMA通道接收數(shù)據(jù)源地址為McBSPO的DRR寄存器,地址為0x01D00000,地址計數(shù)模式為遞增模式。EDMA3_DRV_setDestParams設(shè)置該EDMA通道接收數(shù)據(jù)目的地址為DSP片內(nèi)存儲區(qū)PingBuf-fer首地址,確保第一次傳輸數(shù)據(jù)是到PingBuffer,地址計數(shù)模式同樣為遞增模式。EDMA3_DRV_setSrcIndex用于配置源地址計數(shù)索引值,由于源地址為McBSPO的DRR寄存器,固定不變,所以srcBidx=0,srcCidx=0。接著調(diào)用EDMA3_DRV_setDestIndex配置目的地址計數(shù)索引值,由于接收數(shù)據(jù)為32 bits,所以sreBidx=srcCidx=4,這是因為DSP內(nèi)的最小計數(shù)單元為一個字節(jié),8bit。EDMA3_DRV_setTransferPamms配置剩余的參數(shù)RAM傳輸參數(shù),包括設(shè)置ACNT=4,BCNT=2 048,CCNT=1,采用一維傳輸A-SYNC。

接下來是Ping/Pong傳輸?shù)某绦驅(qū)崿F(xiàn)。需再調(diào)用EDMA3_DRV_requestChannel兩次,替Ping/Pong各自分配一個通道,于是,一共有3個通道,對應(yīng)3個參數(shù)RAM。Ping通道的參數(shù)RAM與主通道的參數(shù)RAM完全一致,Pong通道的參數(shù)RAM與主通道相比,只需將Pong通道接收數(shù)據(jù)目的地址改為PongBuffer首地址。隨后調(diào)用EDMA3_DRV_linkChannel 3次,分別將主通道和Ping通道LINK,Ping通道和Pong通道相互LINK。

2.2.3 EDMA中斷實現(xiàn)

TMS320DM6437中,EDMA的128個通道只產(chǎn)生一種中斷,當(dāng)一個通道傳輸完成后,IPR(Interrupt Pending Register)寄存器里的相應(yīng)位會被置1,EDMA中斷處理器通過查詢IPR寄存器確定是哪個通道完成了傳輸,并調(diào)用相應(yīng)的中斷服務(wù)程序。

EDMA LLD中中斷的設(shè)置通過調(diào)用EDMA3_DRV_requestChannel實現(xiàn)。該函數(shù)的參數(shù)中跟中斷有關(guān)的為eventQ(與通道優(yōu)先級相關(guān)),tceCb(回調(diào)函數(shù),即通道傳輸完成后所調(diào)用的中斷服務(wù)程序)。設(shè)置eventQ=0,保證最高優(yōu)先級,tceCb=edma_isr,該函數(shù)的作用是在通道傳輸完成后發(fā)送一個旗語信號給信號處理程序,通知其對收到的數(shù)據(jù)進行處理。此外,還需調(diào)用EDMA3_DRV_setOptField將參數(shù)RAMOPT參數(shù)中TCINTEN位置1,以使能EDMA中斷。隨后,利用DSP/BIOS將EDMA中斷源和DSP的可屏蔽中斷5連接起來。

3 實現(xiàn)結(jié)果

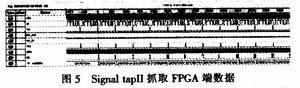

配置好MeBSP和EDMA后,啟動FPGA傳輸數(shù)據(jù),DSP做好接收和發(fā)送數(shù)據(jù)的準(zhǔn)備,實驗中,F(xiàn)PGA連續(xù)不斷地發(fā)送自加地數(shù)給DSP,而DSP只發(fā)送2048個32 bit的從0開始的自加數(shù)據(jù)給FPGA。該結(jié)果如圖5所示。著可以表明DSP內(nèi)部的PingBuffer區(qū)和PongBuffer區(qū)能連續(xù)不斷的收到FPGA傳輸過來的數(shù)據(jù)。

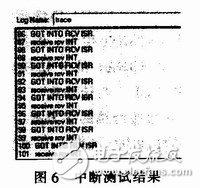

本例中設(shè)置傳完2 048個數(shù)據(jù)后EDMA發(fā)送事件觸發(fā)一次中斷,調(diào)用的中斷服務(wù)程序主要作用是發(fā)送一個旗語信號給信號處理程序,并打印出“GOT INTO RCV ISR”,進入中斷服務(wù)程序,隨后已被阻塞的信號處理程序線程收到旗語信號后,開始運行,并打印信息“receive rcv int”,中斷測試結(jié)果如圖6所示,可以看出中斷在連續(xù)不斷的被觸發(fā)!

4 結(jié)論

經(jīng)過以上的測試和實驗過程,TMS320DM6437的McBSP和EDMA實現(xiàn)了異步串口通信,在其測試中軟硬件的實施都很正常,并且切合實際的應(yīng)用和實施。可以看出該發(fā)放硬件部分容易實現(xiàn),而且非常簡單放心,且采用EDMA方式,很好的節(jié)約了資源,大大的提高了工作的效率和資源的利用。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21988瀏覽量

615117 -

發(fā)生器

+關(guān)注

關(guān)注

4文章

1400瀏覽量

62581 -

串口通信

+關(guān)注

關(guān)注

34文章

1636瀏覽量

56622

發(fā)布評論請先 登錄

McBSP串口配置的關(guān)鍵時

McBSP EDMA例程

兩路McBSP的數(shù)據(jù)輸出存在相對位移的問題,猜測可能與EDMA event Queue有關(guān)?

關(guān)于mcbsp模塊打開FIFO功能收不到EDMA中斷的情況

使用mcbsp EDMA AD數(shù)據(jù)采集請問ad中斷后怎么啟動mcbsp?

McBSP和McASP怎么同時使用edma3?

6748的mcbsp edma3 pingpong傳輸不進入中斷

mcbsp edma3 只能采集一個數(shù)據(jù)并且進不去中斷

基于TMS320DM6437的McBSP與EDMA實現(xiàn)串口通

一種通過SPI接口協(xié)議實現(xiàn)DSP與其它設(shè)備通信的方法

McBSP在語音信號處理中的應(yīng)用與實現(xiàn)

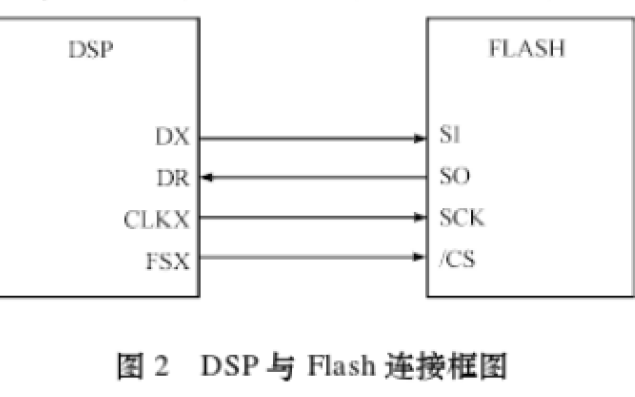

使用McBSP實現(xiàn)DSP與串行Flash的接口通訊

采用McBSP接口與EDMA配置實現(xiàn)異步串口通信,提高工作的效率

采用McBSP接口與EDMA配置實現(xiàn)異步串口通信,提高工作的效率

評論