引言

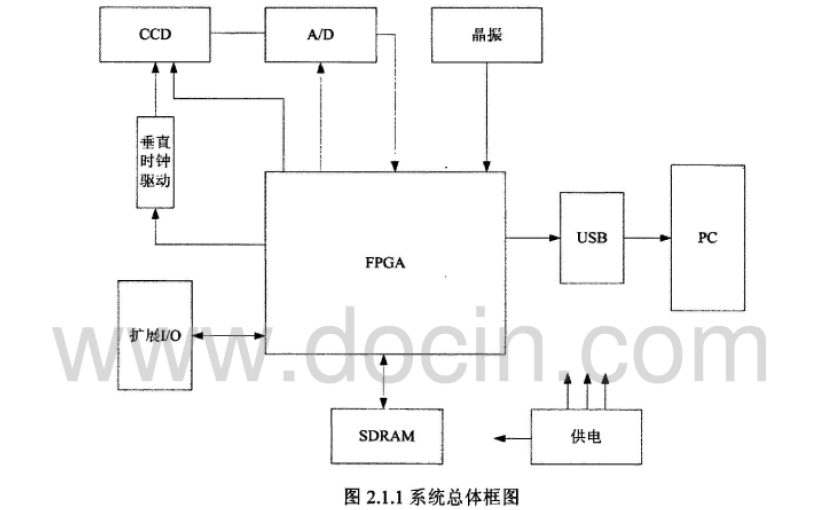

CCD(Charge Coupled Devices)電荷耦合器件是20世紀70年代初發(fā)展起來的新型半導體集成光電器件。近30年來,CCD器件及其應用技術的研究取得飛速進展,特別是在圖像傳感和非接觸測量領域的發(fā)展尤為迅速,它具有噪聲低、光譜響應寬、精度和靈敏度高、可靠性好等優(yōu)點。CCD成像系統(tǒng)主要由光學系統(tǒng)、驅動電路、信號處理電路和圖像處理電路組成。

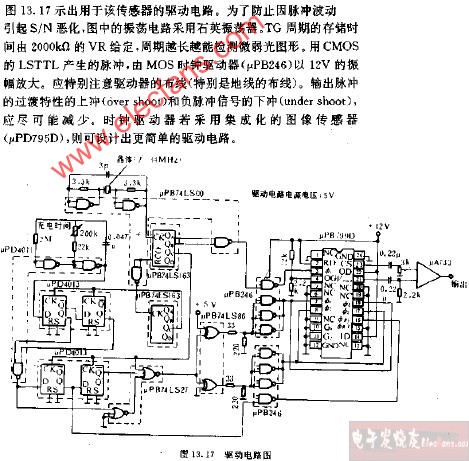

本文主要介紹CCD傳感器驅動電路的設計,包括驅動時序產生電路、電源變換電路和驅動器電路。其中,驅動時序產生電路向CCD傳感器提供正常工作所需要的各種時序脈沖;電源變換電路向CCD提供正常工作時所需的各種直流偏置電壓;驅動器電路用來提高驅動時序的驅動能力。

l CCD驅動時序電路的要求及實現

1.1 CCD圖像傳感器TH7888A

CCD圖像傳感器采用ATMEL公司的TH7888A。它是一種高性能的幀轉移面陣CCD器件,提供單路和雙路兩種輸出方式,輸出數據速率可達40 MHz,每秒30幀圖像。TH7888A具有較低的暗電流及像元讀出噪聲,可用電子快門來調節(jié)曝光時間,性能優(yōu)異。TH7888A由感光區(qū),存儲區(qū)和水平移位寄存器構成,有效像元數為1 024×1 024個。

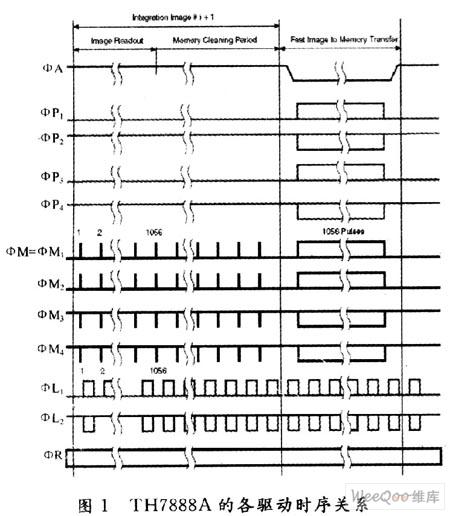

CCD的一個工作周期可分為兩個階段:光積分階段和電荷轉移階段。光積分階段進行感光陣列的電荷積累,存儲區(qū)到轉移寄存器的電荷轉移(行逆程)以及轉移寄存器向輸出放大器的電荷輸出(行正程);轉移階段主要進行幀轉移,即將感光區(qū)的光積分電荷轉移至存儲區(qū)。要完成如上功能就要給CCD提供嚴格的驅動時序時鐘。TH7888A的各驅動時序關系如圖1所示。

圖1中,φPA為幀時鐘,高電平時為光積分階段,低電平時為電荷轉移階段。φP1~φP4為幀轉移脈沖,在光積分階段時不變,在電荷轉移階段時同行轉移控制信號φM1~φM4一起完成整幀的轉移。在光積分階段,行逆程狀態(tài)時,幀存儲區(qū)各行的信號電荷在行轉移信號φM1,φM4控制下向水平移位寄存器方向平移一行,讀出寄存器時鐘φL1,φL2不變;行正程狀態(tài)時,水平移位寄存器中的像元電荷在讀出寄存器時鐘φL1,φL2的控制下逐次經過輸出放大器輸出。每讀出一行信號,進行一次行轉移。一幀圖像傳完后,再進行下一幀圖像的幀轉移。

1.2 基于FPGA的CCD驅動時序的實現

可編程邏輯器件FPGA具有集成度高、速度快、可靠性好及硬件可編程的特點,開發(fā)靈活、易于維護、非常適合CCD驅動的設計。設計選用的是Xilinx公司Spartan3系列的XC3S50,在分析CCD驅動時序關系的基礎上,采用硬件編程語言VHDL編寫,開發(fā)軟件為ISE 10.1。

程序輸入為40 MHz主時鐘CLK,由外部晶振提供,輸出為十三路驅動信號。設計采用單路輸出的方式,輸出數據速率選為10 MHz。使用全部1 024×1 024個有效像元,在水平方向上,有效像元加上隔離元、黑參考元等共1 056個像元。在垂直方向上有效像元加上啞像元、黑參考元等共1 056行。進行適量冗余設計,再考慮幀轉移和行轉移所占用的時間,幀頻為每秒8幀。復位時鐘OR由主時鐘四分頻得到。由于CCD各驅動信號間要嚴格地滿足時序關系,且波形比較復雜,程序采用多進程,多計數器循環(huán)嵌套的方式實現。幀時鐘φA為最外部循環(huán),在光積分階段,由行逆程和行正程組成第一部分內循環(huán),由主時鐘分頻、計數設計完成,同時產生行脈沖信號,對行脈沖信號計數產生幀周期;在電荷轉移階段幀轉移脈沖φP1~φP4(行轉移控制信號φM1~φM4)組成第二部分內循環(huán),信號間的時序關系由主時鐘分頻、移位實現。

在設計上,需要注意以下兩點:

(1)幀轉移脈沖φP1~φP4的占空比為5:3,因此先用一個八進制的計數器設計出占空比為5:3的脈沖,再由幀時鐘φA的控制及移位操作來實現其嚴格的時序。

(2)對于φA和φP1~φP4,手冊上對其波形的邊沿變化時間有限制,對于時間上限,由于信號從FPGA輸出之后是通過驅動器EL7212驅動后送入CCD的,而EL7212輸出波形的上升及下降時間的最大值已滿足此上限要求;對于時間下限,可在CCD管腳附近增加電容和電阻調節(jié)波形邊沿的陡峭度來滿足要求。

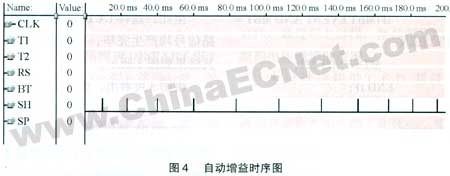

1.3 CCD驅動時序的仿真

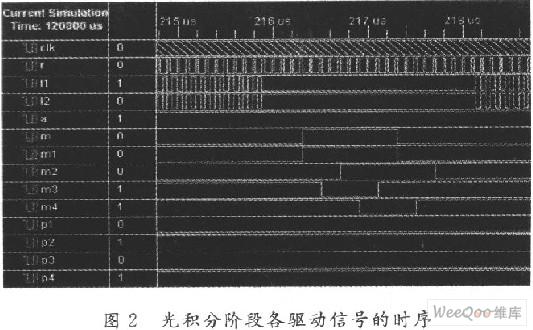

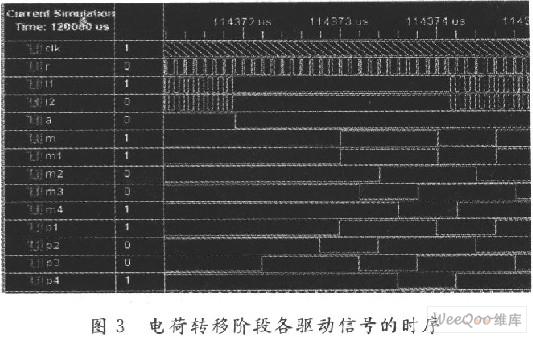

設計采用ISE 10.1自帶的仿真工具對時序進行仿真,并對Xilinx公司的FPGA芯片XC3S50進行配置下載,通過功能仿真驗證設計的可行性。驅動時序的仿真結果如圖2,圖3所示。

由圖可見,設計完成了CCD對驅動信號的要求。

2 電源變換電路

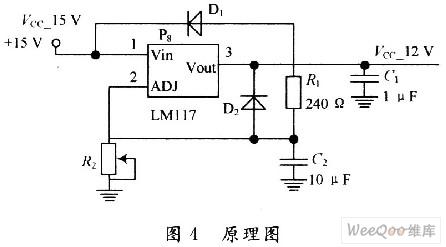

CCD電路的工作電壓取自二次電源。電路所需電壓種類繁多,如CCD傳感器需要+15 V電源和多種偏置電壓,CCD驅動器需要+12 V,+9 V,+8 V,+4 V電源,FPGA正常工作需要的3.3 V,2.5 V,1.2 V等。為了減少二次電源的種類,并考慮到與其他部件電源的共用性,相機系統(tǒng)采用兩種二次電源模塊:+15 V,+5 V。上述各種電壓均由這兩種電源變換而得。為保證FPGA芯片工作的穩(wěn)定,其電壓由Xilinx公司專用的電源轉換芯片提供。其他各種偏置電壓的電源轉換核心器件是LMll7。LMll7是正三端可調穩(wěn)壓器,這種穩(wěn)壓器具有良好的穩(wěn)壓性能,還具有短路保護、過流保護和溫度保護功能。

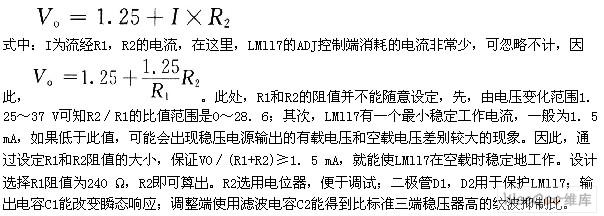

LMll7的輸出電壓范圍為1.2~37 V,H封裝負載電流最大為O.5 A,它的線性調整率和負載調整率比標準的固定穩(wěn)壓器好。通常LMll7輸入端不需要外接電容,除非輸入濾波電容到LMll7輸入端的連線超過15 cm。圖4為實現直流偏壓+12 V的原理圖。圖中,2、3腳之間為1.25 V電壓基準,改變R2阻值即可調整穩(wěn)壓電壓值。輸出電壓為:

3 CCD驅動器

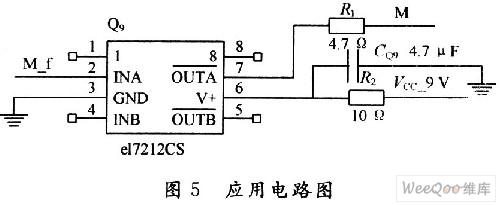

CCD驅動部分的作用是把CCD時序產生單元輸出的各種轉移脈沖信號進行功率放大,以滿足CCD對驅動波形電壓及電流以及時序的要求。驅動信號的好壞會對CCD的電荷轉移效率產生較大的影響,從而影響成像的質量。設計中使CCD正常工作需要的驅動信號和復位信號共13種,這些信號的電壓共有4種,不同的電壓由上述電源轉換器LMll7轉換輸出,再進入驅動器芯片對驅動信號和復位信號進行驅動。由于CCD為容性負載,在較大電壓擺幅的情況下需要在快速的變化沿時能夠提供足夠大的瞬態(tài)驅動電流,因此要選擇工作電流足夠大的器件以滿足要求。芯片選用的是Intersil公司的EL7212,和常用的ICL7667,DS0026相比,EL7212在速率、驅動能力、反應時間、抑噪等各方面表現更為優(yōu)秀,其上升沿和下降沿變化得更快,容性負載為1 000 pF時的典型值為10/13 ns,更適合用于高速相機。EL7212為單電源工作方式,其應用電路如圖5所示。圖5中,電阻R1用于減小內部功耗,電阻R2和電容用于防止過沖,電容盡量靠近管腳。

4 結語

在分析面陣CCD傳感器TH7888A的工作原理和驅動信號要求的基礎上,采用可編程邏輯器件FPGA和硬件描述語言VHDL設計出合理的驅動信號時序,并選用高性能的電壓轉換芯片和驅動器保證CCD的正常穩(wěn)定工作。實驗結果表明,設計的CCD驅動電路較好地滿足了CCD的工作要求。

-

電源

+關注

關注

185文章

18372瀏覽量

256344 -

傳感器

+關注

關注

2566文章

53008瀏覽量

767525 -

FPGA

+關注

關注

1645文章

22050瀏覽量

618564 -

CCD

+關注

關注

32文章

892瀏覽量

144464

發(fā)布評論請先 登錄

CCD的應用(CCD固態(tài)圖像傳感器)?

CCD傳感器驅動電路怎么設計?

基于CPLD的CCD驅動電路自動增益調整

CCD類圖像傳感器成像器件的噪聲研究

使用FPGA設計CCD驅動傳輸電路的資料說明

CCD傳感器是什么_CCD傳感器的應用

如何使用FPGA實現全幀CCD驅動的設計

基于FPGA器件的CCD傳感器驅動電路的方案設計

基于FPGA器件的CCD傳感器驅動電路的方案設計

評論