數(shù)據(jù)采集是工業(yè)測量和控制系統(tǒng)中的重要部分。它是測控現(xiàn)場的模擬信號源與上位機(jī)之間的接口,其任務(wù)是采集現(xiàn)場連續(xù)變化的被測信號。系統(tǒng)應(yīng)將所采集的模擬數(shù)據(jù)信號盡可能真實(shí)、不失真地顯示給控制人員。

隨著計(jì)算機(jī)技術(shù)和EDA技術(shù)的發(fā)展,由于復(fù)雜可編程邏輯器件(CPLD)具有高集成度、小體積、低成本、低功耗以及高穩(wěn)定性等諸多優(yōu)點(diǎn)而廣泛使用到諸如傳統(tǒng)工業(yè)控制等各個領(lǐng)域。基于ISA的接口電路,其布線要求遠(yuǎn)沒有PCI或USB接口板高。由于它能夠提供16位I/O操作,對I/O的直接讀寫可以完全不考慮復(fù)雜的驅(qū)動程序和應(yīng)用程序,因而在ISA總線上開發(fā)接口電路目前仍是首先考慮的方法。因此,這里提出一種基于CPLD和ISA總線的數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)。

1 系統(tǒng)硬件設(shè)計(jì)

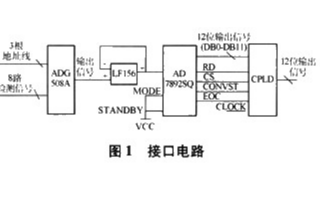

數(shù)據(jù)采集系統(tǒng)的硬件電路主要包括:CPLD邏輯控制電路、8254定時器電路、A/D轉(zhuǎn)換電路。該系統(tǒng)硬件設(shè)計(jì)框圖如圖1所示。

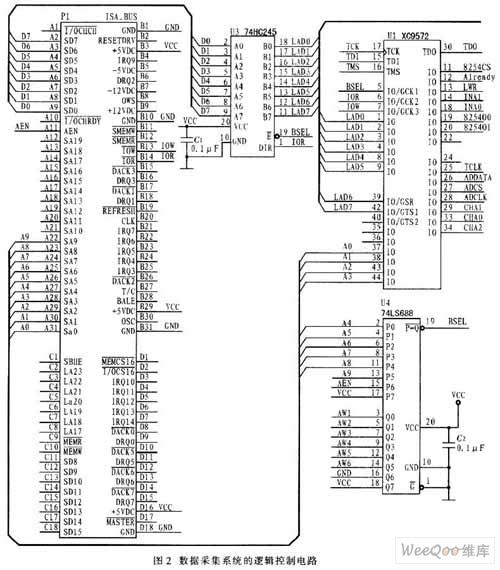

1.1 CPLD邏輯控制電路

該系統(tǒng)使用XC9572作為主控器件。XC9572是一款高性能可編程邏輯器件,內(nèi)含4個36 v 18功能模塊,具有l(wèi) 600個可用系統(tǒng)門。ISA總線上的地址、控制指令和數(shù)據(jù)被送進(jìn)CPLD,經(jīng)處理后送到相應(yīng)電路中。由A/D轉(zhuǎn)換電路得到的數(shù)據(jù)也返回到CPLD進(jìn)行處理,并經(jīng)ISA總線送至計(jì)算機(jī)中。

圖2為數(shù)據(jù)采集系統(tǒng)的邏輯控制電路,Ul是數(shù)據(jù)緩沖器74HC245,由lSA總線的讀/寫信號(IOR/IOW)和板卡選擇信號(BSEL)決定數(shù)據(jù)的流向。比較器74LS688和XFl組成板卡選擇信號發(fā)生電路。通過在XFl上的跳線可確定采集系統(tǒng)板的基地址。該系統(tǒng)基地址設(shè)置為280H。

ISA總線上的讀寫信號,經(jīng)緩沖器的數(shù)據(jù)信號(LADO~LAD7),地址信號(A0~A3)均與XC29572相連,CPLD發(fā)送A/D轉(zhuǎn)換器的片選信號(ADCS)、A/D時鐘信號(ADCLK)以及通道選擇信號(CHA0~CHA2)。

1.2 8254可編程定時器電路

8254可編程定時器內(nèi)部具有3個獨(dú)立的16位減法計(jì)數(shù)器,它可由程序設(shè)置成多種工作方式,有6種可選工作方式。計(jì)數(shù)器按照設(shè)置各工作方式寄存器中控制字工作,按十進(jìn)制計(jì)數(shù)或二進(jìn)制計(jì)數(shù),最高計(jì)數(shù)速率可達(dá)10 MHz。

該數(shù)據(jù)采集系統(tǒng)需要由8254提供AD轉(zhuǎn)換電路的時鐘信號和片選信號,通過改變8254的控制字改變數(shù)據(jù)采集系統(tǒng)的轉(zhuǎn)換頻率。8254定時器的輸入時鐘由外部晶振提供。定時器和定時器的輸出信號直接送入可編程邏輯器件XC9572,經(jīng)處理后提A/D轉(zhuǎn)換電路使用。上位機(jī)寫入的控制字經(jīng)ISA總線送至8254,同時XC9572給8254提供必要的控制信號,如:8254讀/寫信號、片選信號、地址信號等。

假設(shè)系統(tǒng)的外部時鐘為2 MHz,如果需要8254的定時器0輸出一個頻率為l MHz,占空比為50%的時鐘,則8254的定時器控制字可設(shè)置為:D7~D0=00110110,其中,D7D6=00,表示選擇定時器;D5D4=11,表示先讀/寫低8位,后讀/寫高8位數(shù)據(jù);D3D2Dl=011,表示工作方式3,方波發(fā)生器;D0=0,表示二進(jìn)制計(jì)數(shù)。

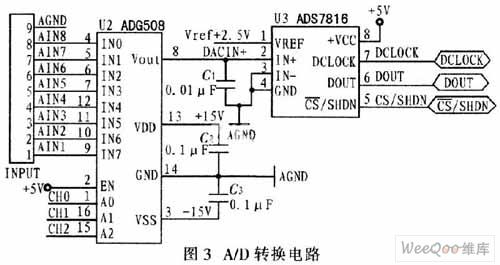

1.3 A/D轉(zhuǎn)換電路

A/D轉(zhuǎn)換電路完成數(shù)據(jù)采集和轉(zhuǎn)換,主要包括MD轉(zhuǎn)換和模擬信號采樣兩部分電路。

8通道模擬采樣開關(guān)ADG508用于采樣模擬信號。由CPLD送來的通道選擇信號(CH0~CH2)用于選擇輸入的通道號。被選通的通道采樣得到的模擬信號送給ADS7816的IN+端,進(jìn)行AD轉(zhuǎn)換,如圖3所示。

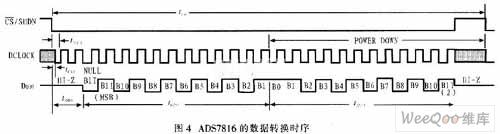

A/D轉(zhuǎn)換電路采用TI公司的ADS7816,該器件是12位串行A/D轉(zhuǎn)換器,采樣頻率高達(dá)200 kHz,轉(zhuǎn)換所需時間短,轉(zhuǎn)換精度高,輸出形式為位串行,因此在對ADS7816進(jìn)行讀數(shù)據(jù)操作時需注意數(shù)據(jù)轉(zhuǎn)換過程中的時序。

圖4是ADS7816的數(shù)據(jù)轉(zhuǎn)換時序。當(dāng)ADS7816的片選端下降沿到來時,開始啟動一次A/D轉(zhuǎn)換,保持轉(zhuǎn)換時鐘輸入和片選信號低電平,最初的1.5~2個時鐘時間里,完成模擬信號的采樣,這段時間ADS7816的輸出呈高阻狀態(tài)(HI-Z)。緊接著的1個時鐘周期里,DOUT輸出1個空位(NULL BIT)。隨后,ADS7816在12個連續(xù)的時鐘周期內(nèi)把12位的A/D轉(zhuǎn)換結(jié)果輸出,其中先輸出最高位(MSB),最后輸出最低位(LSB)。如果12位數(shù)據(jù)送出后仍有轉(zhuǎn)換時鐘且ADS7816的片選仍保持低電平,那么轉(zhuǎn)換器會從最低位起逐位重復(fù)輸出之前轉(zhuǎn)換的結(jié)果。當(dāng)下一個片選信號的下降沿到來時,A/D轉(zhuǎn)換器開始啟動下一次A/D轉(zhuǎn)換。

2 系統(tǒng)軟件設(shè)計(jì)

系統(tǒng)軟件設(shè)計(jì)包括基于VHDL的邏輯控制程序設(shè)計(jì)和基于C語言的上位機(jī)采集測試程序設(shè)計(jì)。

2.1 VHDL程序設(shè)計(jì)

系統(tǒng)設(shè)計(jì)硬件中,可編程邏輯器件完成的內(nèi)容有:接收上位機(jī)的地址和數(shù)據(jù),為模擬開關(guān)提供通道選擇信號,為A/D轉(zhuǎn)換電路提供時鐘信號和片選信號,接收ADS7816轉(zhuǎn)換的數(shù)據(jù),向上位機(jī)傳送轉(zhuǎn)換結(jié)果。

從圖4中可得到ADS7816在片選信號下降沿到來后的14.5~15個時鐘周期里,完成一次轉(zhuǎn)換并逐位輸出12位轉(zhuǎn)換結(jié)果。為了能夠得到完整的正確的A/D轉(zhuǎn)換結(jié)果,采用計(jì)數(shù)方式設(shè)置標(biāo)志位FLG。在ADS7816的片選信號為低電平的前15個時鐘周期中,即“計(jì)數(shù)器計(jì)數(shù)值≤14”時,F(xiàn)LG=l,表示A/D轉(zhuǎn)換正在進(jìn)行;當(dāng)“計(jì)數(shù)器的計(jì)數(shù)值>14”,則FLG=0,表示A/D轉(zhuǎn)換結(jié)束。當(dāng)FLG=0時,程序可讀取一次正確的A/D轉(zhuǎn)換數(shù)據(jù)。

因?yàn)锳DS7816的數(shù)據(jù)轉(zhuǎn)換結(jié)果是串行輸入到CPLD中,需在CPLD中將得到的數(shù)據(jù)進(jìn)行串并轉(zhuǎn)換后再通過ISA總線的8位數(shù)據(jù)線分2次送出。

系統(tǒng)進(jìn)行數(shù)據(jù)轉(zhuǎn)換前需先選擇輸入通道,確定采集哪一路信號。上位機(jī)輸入的通道號經(jīng)CPLD送至8路模擬采樣開關(guān)。

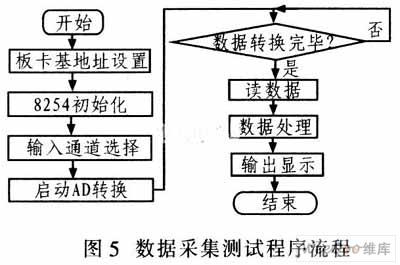

2.2 數(shù)據(jù)采集測試程序設(shè)計(jì)

上位機(jī)的數(shù)據(jù)采集測試程序采用C語言設(shè)計(jì)。因?yàn)橄到y(tǒng)采用ISA接口,所以功能測試無需編寫復(fù)雜的應(yīng)用程序,只需在Win98操作系統(tǒng)里編寫C語言的測試程序即可實(shí)現(xiàn)系統(tǒng)的數(shù)據(jù)采集功能。上位機(jī)的數(shù)據(jù)采集測試程序主要完成:采集系統(tǒng)的硬件初始化、通道選擇、數(shù)據(jù)采集、數(shù)據(jù)處理和數(shù)據(jù)輸出。其程序設(shè)計(jì)流程如圖5所示。

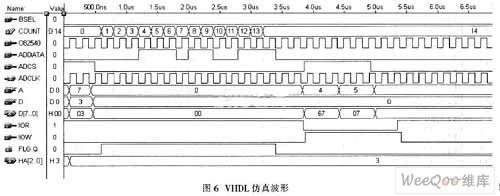

3 仿真和實(shí)驗(yàn)結(jié)果

圖6所示為寫入XC9572的VHDL程序的仿真波形,主要是CPLD控制A/D轉(zhuǎn)換的功能仿真。從仿真波形圖中可以看出,當(dāng)?shù)刂稟為7時,寫入通道號3,得到的輸入通道選通信號為3,實(shí)現(xiàn)通過上位機(jī)選擇輸入通道功能。當(dāng)ADCS的下降沿到來后開始啟動A/D轉(zhuǎn)換;ADCS下降沿起的第3個時鐘對應(yīng)的ADDATA為系統(tǒng)轉(zhuǎn)換的第1個數(shù)據(jù),直到這次轉(zhuǎn)換完畢。由給定的ADDATA數(shù)據(jù)得知,串行輸入的數(shù)據(jù)是767H(011l O110 0111B)。仿真結(jié)果中,地址為4時,數(shù)據(jù)的低8位結(jié)果為67H;地址為5時,數(shù)據(jù)的高8位結(jié)果為07H,仿真結(jié)果完全正確。

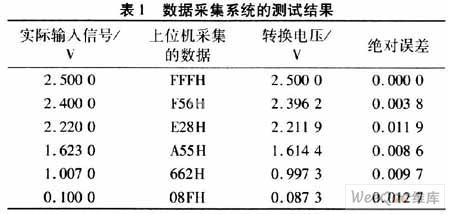

在Windows98下,使用基于C語言的數(shù)據(jù)采集測試程序,可得到如表l所示的測試數(shù)據(jù)。從所列數(shù)據(jù)看出,該數(shù)據(jù)采集系統(tǒng)采集數(shù)據(jù)正確,且精度高。

4 結(jié)論

基于CPLD的數(shù)據(jù)采集系統(tǒng)具有硬件線路簡單、精度高、采集速度快的特點(diǎn)。ISA總線和CPLD結(jié)合的數(shù)據(jù)采集系統(tǒng)有其獨(dú)特的優(yōu)勢。該數(shù)據(jù)采集系統(tǒng)可循環(huán)采樣多路(8路)模擬信號采樣。實(shí)際測試結(jié)果表明該設(shè)計(jì)方案可行,且具有很高的實(shí)用價值。

-

cpld

+關(guān)注

關(guān)注

32文章

1257瀏覽量

171165 -

計(jì)算機(jī)

+關(guān)注

關(guān)注

19文章

7638瀏覽量

90363 -

數(shù)據(jù)采集

+關(guān)注

關(guān)注

40文章

7038瀏覽量

115953 -

定時器

+關(guān)注

關(guān)注

23文章

3297瀏覽量

117455

發(fā)布評論請先 登錄

基于PCI 總線的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

基于復(fù)雜可編程邏輯器件(CPLD)的120MHZ高速A/D采集卡的設(shè)計(jì)

可編程邏輯器件

如何采用可編程邏輯器件和A/D轉(zhuǎn)換器組成高速數(shù)據(jù)采集卡?

怎么采用可編程邏輯器件設(shè)計(jì)數(shù)字系統(tǒng)?

PLD可編程邏輯器件

基于復(fù)雜可編程邏輯器件(CPLD)的120MHZ高速AD采集

可編程邏輯器件基礎(chǔ)及應(yīng)用實(shí)驗(yàn)指導(dǎo)書

基于單片機(jī)的復(fù)雜可編程邏輯器件快速配置方法

什么是PLD(可編程邏輯器件)

EDA技術(shù)與應(yīng)用(可編程邏輯器件)

采用復(fù)雜可編程邏輯器件實(shí)現(xiàn)多路信號采集系統(tǒng)的設(shè)計(jì)

采用復(fù)雜可編程邏輯器件與ISA總線相結(jié)合實(shí)現(xiàn)數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

采用復(fù)雜可編程邏輯器件與ISA總線相結(jié)合實(shí)現(xiàn)數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

評論