順序控制邏輯電路廣泛應(yīng)用于機(jī)器人、全自動(dòng)家用電器、工業(yè)自動(dòng)化設(shè)備及其它自動(dòng)化裝置中,它常采用CPLD器件進(jìn)行設(shè)計(jì)與實(shí)現(xiàn)。

如果直接采用原理圖輸入工具或VHDL語言描述的方法來設(shè)計(jì)順序控制邏輯電路,則設(shè)計(jì)效率不高。這是因?yàn)轫樞蚩刂七壿嬰娐分邪罅康腎/O信號(hào),控制邏輯就是這些I/O信號(hào)的邏輯組合,這些I/O信號(hào)在整個(gè)控制邏輯中會(huì)被大量引用,而原理圖輸入工具中的元件如邏輯門和觸發(fā)器等的輸入引腳數(shù)是固定的,邏輯引用不夠靈活,同時(shí),I/O信號(hào)的大量引用又會(huì)使連線過于復(fù)雜。VHDL是一種文本設(shè)計(jì)工具,不是順序控制邏輯電路設(shè)計(jì)的專用工具,直接用它編寫的順序控制邏輯程序結(jié)構(gòu)零亂,不夠直觀,編程及調(diào)試效率都不高。

梯形圖的原理與特性

梯形圖是可編程邏輯控制器(PLC)實(shí)現(xiàn)順序控制邏輯的專用設(shè)計(jì)工具,用梯形圖描述的控制邏輯非常直觀易懂。梯形圖工具使用簡(jiǎn)便,開發(fā)效率高,對(duì)電路設(shè)計(jì)者的要求很低,因此,電路設(shè)計(jì)者可以將更多精力用在順序控制邏輯功能的實(shí)現(xiàn)與優(yōu)化上。

梯形圖以兩根平行的豎線分別表示電源線和地線,在這兩根豎線之間,用橫線表示電氣連接線,將各種代表邏輯量(“ON”或“OFF”)的元件觸點(diǎn)及輸出執(zhí)行元件的線圈用橫線串接成一條電氣回路。多條這樣的回路并列在一起,形狀如同階梯,就構(gòu)成了實(shí)現(xiàn)所需順序控制邏輯的梯形圖。

一個(gè)典型的順序控制電路的梯形圖如圖1所示。在梯形圖的每個(gè)回路中,當(dāng)所有串聯(lián)的觸點(diǎn)全部都處于“ON”狀態(tài)時(shí),回路就處于導(dǎo)通狀態(tài),回路末端的輸出執(zhí)行元件線圈被接通。例如,當(dāng)X0為“ON”,X1為“OFF”時(shí),執(zhí)行元件Y0就被接通,產(chǎn)生輸出動(dòng)作。執(zhí)行元件不能多個(gè)串聯(lián),其觸點(diǎn)所代表的邏輯量可以在梯形圖中被多次反復(fù)引用。電路的各I/O信號(hào)也可以在梯形圖中被多次反復(fù)引用。

梯形圖-VHDL設(shè)計(jì)方法

如果將梯形圖法應(yīng)用于CPLD開發(fā)中,采用基于梯形圖的VHDL設(shè)計(jì)方法,就可將兩種設(shè)計(jì)工具的長(zhǎng)處相結(jié)合,從而提高順序邏輯電路設(shè)計(jì)開發(fā)的效率,簡(jiǎn)化設(shè)計(jì)難度。

梯形圖-VHDL設(shè)計(jì)方法的總體思路是,將開發(fā)過程分為兩個(gè)階段:第一階段先采用梯形圖對(duì)順序邏輯電路的邏輯進(jìn)行描述和設(shè)計(jì),第二階段通過VHDL語言來實(shí)現(xiàn)梯形圖的邏輯功能,并通過CPLD專用的開發(fā)軟件對(duì)所設(shè)計(jì)的邏輯進(jìn)行仿真調(diào)試。

在這里,梯形圖的作用是作為順序邏輯電路的邏輯原型,是VHDL語言編程的依據(jù)。用梯形圖完成的是電路的邏輯功能設(shè)計(jì),而VHDL語言程序用于實(shí)現(xiàn)其邏輯功能。二者分工協(xié)作,相得益彰。其中梯形圖-VHDL設(shè)計(jì)方法的關(guān)鍵在于梯形圖的VHDL語言描述。

梯形圖的VHDL描述方法

梯形圖由三種要素構(gòu)成,即輸入信號(hào)、輸出執(zhí)行元件和連接線。在VHDL程序中必須采用特殊方法對(duì)這三要素進(jìn)行有效的描述。

(1)輸入信號(hào)Xi(i=0,1,…,M)

M個(gè)輸入信號(hào)必須在實(shí)體的端口說明語句(PORT語句)中予以說明。在PORT語句中,各輸入信號(hào)可以單獨(dú)說明,也可將一組或一類輸入信號(hào)用一個(gè)標(biāo)準(zhǔn)位向量(STD_LOGIC_VECTOR)說明。

可以規(guī)定輸入信號(hào)為邏輯“1”時(shí),其狀態(tài)為“ON”;而為邏輯“0”時(shí),其狀態(tài)為“OFF”。梯形圖中對(duì)輸入信號(hào)Xi的引用對(duì)應(yīng)于VHDL程序中對(duì)Xi的直接引用,而梯形圖中對(duì)的引用則對(duì)應(yīng)于VHDL程序中對(duì)(NOT Xi)的引用。

(2)輸出執(zhí)行元件Yj(j=0,1,…,N)

N個(gè)輸出執(zhí)行元件(即輸出信號(hào))也必須在實(shí)體的端口說明語句(PORT語句)中予以說明。如果某輸出信號(hào)在梯形圖中的其它位置需要被引用,則在PORT語句中必須將其端口模式設(shè)置為“BUFFER(輸出并向內(nèi)部反饋)”。在PORT語句中,各輸出信號(hào)可以單獨(dú)說明,也可將一組或一類輸出信號(hào)用一個(gè)標(biāo)準(zhǔn)位向量(STD_LOGIC_VECTOR)說明。

可以規(guī)定輸出信號(hào)為邏輯“1”時(shí),其狀態(tài)為“ON”;而為邏輯“0”時(shí),其狀態(tài)為“OFF”。梯形圖中對(duì)輸出信號(hào)Yj的引用對(duì)應(yīng)于VHDL程序中對(duì)Yj的直接引用,而梯形圖中對(duì)的引用則對(duì)應(yīng)于VHDL程序中對(duì)(NOT Yj)的引用。

(3)連接線

梯形圖中的連接線有四種:回路最左側(cè)的橫線為回路起始線(母線);回路中部的橫線為“與”邏輯連接線;回路中部的豎線為“或”邏輯連接線;回路右側(cè)與輸出執(zhí)行元件相連的線為輸出線。

在VHDL程序中,可用“與”邏輯運(yùn)算符“AND”代替梯形圖中的“與”邏輯連接線,用“或”邏輯運(yùn)算符“OR” 替梯形圖中的“或”邏輯連接線,用信號(hào)賦值運(yùn)算符“《=” 代替梯形圖中的輸出線。

這樣,梯形圖中的每一個(gè)電氣回路都可很方便地用一條對(duì)輸出信號(hào)的賦值語句來描述。賦值語句的左邊是輸出信號(hào),右邊是一個(gè)由各輸入/輸出信號(hào)及與/或運(yùn)算符構(gòu)成的邏輯表達(dá)式。

雖然在VHDL程序中也可以用IF分支語句來描述梯形圖各回路中信號(hào)的邏輯關(guān)系,但這樣會(huì)使程序結(jié)構(gòu)很雜亂,調(diào)試很困難,可讀性也較差,因此不推薦用IF語句來描述梯形圖回路中的邏輯,而建議采用邏輯表達(dá)式給輸出信號(hào)賦值的描述方法。

對(duì)于梯形圖中那些不向外輸出信號(hào)的內(nèi)部元件來說,如定時(shí)器、狀態(tài)寄存器、移位寄存器等,可采用元件例化語句調(diào)用有關(guān)的庫(kù)元件功能進(jìn)行描述,并在結(jié)構(gòu)體中為其輸出聲明一個(gè)中間信號(hào)。當(dāng)這類元件有輸出信號(hào)時(shí),將其輸出信號(hào)賦值給聲明好的中間信號(hào),電路中其它位置就可對(duì)該中間信號(hào)或者它的取反信號(hào)進(jìn)行引用。 通過以上各描述方法,就可將用梯形圖設(shè)計(jì)的電路邏輯原型方便地逐行轉(zhuǎn)換為VHDL程序。在進(jìn)行電路邏輯功能設(shè)計(jì)時(shí),就不必為VHDL程序的語法和程序結(jié)構(gòu)花費(fèi)過多的時(shí)間,能更加專注于電路邏輯功能設(shè)計(jì)與優(yōu)化,同時(shí)也使所編寫的VHDL程序邏輯更加清晰,可讀性更好。

應(yīng)用實(shí)例

以下通過圖1所示的典型的順序控制電路的實(shí)例來說明梯形圖的VHDL描述方法。

在圖1中,X0、X2和X4分別是三個(gè)輸出回路的啟動(dòng)信號(hào),X1、X3和X5分別是三個(gè)輸出回路的停止信號(hào),Y0、Y1和Y2分別是三個(gè)輸出回路的輸出執(zhí)行元件。只有當(dāng)Y0啟動(dòng)輸出后,才允許Y1啟動(dòng);只有當(dāng)Y1啟動(dòng)輸出后,才允許Y2啟動(dòng)。reset為CPLD芯片的上電復(fù)位信號(hào),低電平有效。

實(shí)現(xiàn)該電路控制的VHDL程序邏輯如下:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY sequence IS

PORT(X0, X1, X2, X3, X4, X5: IN STD_LOGIC;

RESET: IN STD_LOGIC;

Y0, Y1, Y2 : BUFFER STD_LOGIC);

END sequence;

ARCHITECTURE ladder OF sequence IS

BEGIN

PROCESS(RESET, X0,X1,X2,X3,X4,X5)

BEGIN

IF (RESET=‘0’) THEN

Y0《=‘0’; Y1《=‘0’; Y2《=‘0’;

ELSE

Y0《=(X0 OR Y0)AND (NOT X1);

Y1《=(X2 OR Y1)AND (NOT X3)AND Y0;

Y2《=(X4 OR Y2)AND (NOT X5)AND Y1;

END IF;

END PROCESS;

END ladder;

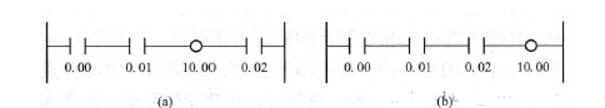

利用MAX+PLUS II的定時(shí)仿真工具對(duì)上面的程序進(jìn)行仿真,結(jié)果如圖2所示。從時(shí)序仿真的結(jié)果可以看到,電路的輸出邏輯與梯形圖原型的邏輯完全一致。

結(jié)語

本文通過對(duì)一個(gè)典型順序控制電路梯形圖的VHDL程序設(shè)計(jì)與時(shí)序仿真,表明梯形圖-VHDL設(shè)計(jì)方法是正確可行的。梯形圖法的引入使VHDL程序的設(shè)計(jì)得到簡(jiǎn)化,所設(shè)計(jì)出的程序結(jié)構(gòu)簡(jiǎn)練,輸出邏輯表達(dá)清楚。梯形圖與VHDL程序分工明確,電路邏輯功能設(shè)計(jì)的工作由梯形圖來承擔(dān),而VHDL程序只需負(fù)責(zé)對(duì)梯形圖的邏輯功能進(jìn)行描述并生成CPLD的下載文件。這樣,對(duì)兩種設(shè)計(jì)工具各取所長(zhǎng),就使得用CPLD開發(fā)順序邏輯控制電路和系統(tǒng)的效率得到提高。

-

cpld

+關(guān)注

關(guān)注

32文章

1257瀏覽量

171043 -

plc

+關(guān)注

關(guān)注

5031文章

13744瀏覽量

472288 -

vhdl

+關(guān)注

關(guān)注

30文章

819瀏覽量

129581

發(fā)布評(píng)論請(qǐng)先 登錄

PLC梯形圖程序的設(shè)計(jì)方法與技巧

PLC梯形圖編程方法(PPT版)

plc梯形圖如何看對(duì)錯(cuò)

請(qǐng)問一下梯形圖的VHDL設(shè)計(jì)方法怎么進(jìn)行CPLD的開發(fā)設(shè)計(jì)?

如何去實(shí)現(xiàn)一個(gè)基于梯形圖的軟PLC設(shè)計(jì)

PLC梯形圖是如何編程的呢?

PLC梯形圖編程有哪些規(guī)范_plc梯形圖編程實(shí)例

PLC梯形圖的經(jīng)驗(yàn)設(shè)計(jì)方法

PLC梯形圖編程的方法

基于梯形圖的VHDL設(shè)計(jì)方法進(jìn)行CPLD的開發(fā)設(shè)計(jì)

基于梯形圖的VHDL設(shè)計(jì)方法進(jìn)行CPLD的開發(fā)設(shè)計(jì)

評(píng)論