引言

21世紀是電子信息產業主導的知識經濟時代,信息領域正在發生一場巨大變革,其先導力量和決定性因素正是微電子集成電路。硅片技術的日益成熟,特別是深亞微米(DSM,Deep Sub-Micron)和超深亞微米(VDSM,Very Deep Sub-Micron)技術,極大促進了集成電路產業的快速發展。

集成電路發展經歷了電路集成、功能集成、技術集成,直至今天基于計算機軟硬件的知識集成,這標志著傳統電子系統已全面進入現代電子系統階段,這也被譽為進入3G時代,即單片集成度達到1G個晶體管、器件工作速度達到1GHz、數據傳輸速率達到1Gbps。

EDA(Electronic Design Automation,電子設計自動化)技術基于計算機輔助設計,它融合了應用電子技術、計算機技術、信息處理技術、智能化技術的最新成果,以實現電子產品的自動設計。EDA是現代電子設計技術的核心,在現代集成電路設計中占據重要地位。FPGA(Field Programmable Gate Array,現場可編程門陣列)作為可編程邏輯器件的典型代表,它的出現及日益完善適應了當今時代的數字化發展浪潮,它正廣泛應用在現代數字系統設計中。

EDA技術與FPGA原理

1.EDA技術特征

EDA是電子設計領域的一場革命,它源于計算機輔助設計(CAD,Computer Aided Design)、計算機輔助制造(CAM,Computer Aided Made)、計算機輔助測試(CAT,Computer Aided Test)和計算機輔助工程(CAE,Computer Aided Engineering)。利用EDA工具,電子設計師從概念、算法、協議開始設計電子系統,從電路設計、性能分析直到IC版圖或PCB版圖生成的全過程均可在計算機上自動完成。

EDA代表了當今電子設計技術的最新發展方向,其基本特征是設計人員以計算機為工具,按照自頂向下的設計方法,對整個系統進行方案設計和功能劃分,由硬件描述語言完成系統行為級設計,利用先進的開發工具自動完成邏輯編譯、化簡、分割、綜合、優化、布局布線(PAR,Place And Route)、仿真及特定目標芯片的適配編譯和編程下載,這被稱為數字邏輯電路的高層次設計方法。

作為現代電子系統設計的主導技術,EDA具有兩個明顯特征:即并行工程(Concurrent Engineering)設計和自頂向下(Top-down)設計。其基本思想是從系統總體要求出發,分為行為描述(Behaviour Description)、寄存器傳輸級(RTL,Register Transfer Level)描述、邏輯綜合(Logic Synthesis)三個層次,將設計內容逐步細化,最后完成整體設計,這是一種全新的設計思想與設計理念。

2.FPGA原理

今天,數字電子系統的設計方法及設計手段都發生了根本性變化,正由分立數字電路向可編程邏輯器件(PLD,Programmable Logic Device)及專用集成電路(ASIC,Application Specific Integrated Circuit)轉變。FPGA與CPLD(Programmable Logic Device,復雜可編程邏輯器件)都屬于PLD的范疇,它們在現代數字系統設計中正占據越來越重要的地位。

FPGA是由用戶編程來實現所需邏輯功能的數字集成電路,它不僅具有設計靈活、性能高、速度快等優勢,而且上市周期短、成本低廉。FPGA設計與ASIC前端設計十分類似,在半導體領域中FPGA應用日益普及,已成為集成電路中最具活力和前途的產業。同時,隨著設計技術和制造工藝的完善,器件性能、集成度、工作頻率等指標不斷提升,FPGA已越來越多地成為系統級芯片設計的首選。

FPGA由PAL(可編程陣列邏輯)、GAL(通用陣列邏輯)發展而來,其基本設計思想是借助于EDA開發工具,用原理圖、狀態機、布爾表達式、硬件描述語言等方法進行系統功能及算法描述,設計實現并生成編程文件,最后通過編程器或下載電纜用目標器件來實現。

FPGA器件采用邏輯單元陣列(LCA,Logic Cell Array)結構、SDRAM工藝,其中LCA由三類可編程單元組成。

(1)可配置邏輯塊(CLB,Configurable Logic Block):被稱為核心陣列,是實現自定義邏輯功能的基本單元,散布于整個芯片;

(2)輸入/輸出模塊(IOB,Input/Output Block):排列于芯片四周,為內部邏輯與器件封裝引腳之間提供可編程接口;

(3)可編程互連資源(PI,Programmable Interconnect):包括不同長度的連線線段及連接開關,其功能是將各個可編程邏輯塊或I/O塊連接起來以構成特定電路。

全球生產FPGA的廠家很多,但影響力最大的是Xilinx公司和Altera公司,世界上第一片FPGA是在20世紀80年代中期Xilinx公司率先推出的。不同廠家生產的FPGA在可編程邏輯塊的規模、內部互連線結構及所采用的可編程元件上存在較大差異,實際使用時應注意區分。

FPGA設計應用及優化策略

1.FPGA設計層次分析

FPGA設計包括描述層次及描述領域兩方面內容。通常設計描述分為6個抽象層次,從高到低依次為:系統層、算法層、寄存器傳輸層、邏輯層、電路層和版圖層。對每一層又分別有三種不同領域的描述:行為域描述、結構域描述和物理域描述。

系統層是系統最高層次的抽象描述,針對于電子系統整體性能。算法層又稱為行為層,它是在系統級性能分析和結構劃分后對每個模塊的功能描述。算法層所描述的功能、行為最終要用數字電路來實現。而數字電路本質上可視為由寄存器和組合邏輯電路組成,其中寄存器負責信號存儲,組合邏輯電路負責信號傳輸。寄存器傳輸層描述正是從信號存儲、傳輸的角度去描述整個系統。寄存器和組合邏輯本質上是由邏輯門構成,邏輯層正是從邏輯門組合及連接角度去描述整個系統。

FPGA各個描述層次及綜合技術關系如圖1所示。傳統的綜合工具是將寄存器傳輸級(RTL)的描述轉化為門級描述。隨著以行為設計為主要標志的新一代系統設計理論的不斷成熟,能夠將系統行為級描述轉化為RTL描述的高層次綜合技術不斷涌現。

作為現代集成電路設計的重點與熱點,FPGA設計一般采用自頂向下、由粗到細、逐步求精的方法。設計最頂層是指系統的整體要求,最下層是指具體的邏輯電路實現。自頂向下是將數字系統的整體逐步分解為各個子系統和模塊,若子系統規模較大則進一步分解為更小的子系統和模塊,層層分解,直至整個系統中各子模塊關系合理、便于設計實現為止。

2.VHDL在FPGA設計中的應用

集成電路設計規模及復雜度不斷增大,用傳統原理圖方法進行系統級芯片設計已不能滿足設計要求,而硬件描述語言(HDL,Hardware Description Language)在進行大規模數字系統設計時具有諸多優勢,因此利用硬件描述語言進行系統行為級設計已成為FPGA與ASIC設計的主流。目前最流行、最具代表性的硬件描述語言是美國國防部(DOD)開發的VHDL(VHSIC Hardware Description Language)和GDA(Gateway Design Automation)公司開發的Verilog HDL。

VHSIC代表Very High Speed Integrated Circuit,因此VHDL即甚高速集成電路硬件描述語言。VHDL語法嚴格,1987年即成為IEEE標準,即IEEE STD 1076-1987,1993年進一步修訂成為IEEE STD 1076-1993。

VHDL作為IEEE標準,已得到眾多EDA公司支持,其主要優點有:

● 描述能力強,支持系統行為級、寄存器傳輸級和門級三個層次設計;

● 可讀性好、移植性強,其源文件既是程序又是文檔,便于復用和交流;

● 支持自頂向下的設計和基于庫(Library-based)的設計;

● 支持同步、異步及隨機電路的設計;

● 與工藝無關,生命周期長。

VHDL語言主要應用在行為層和寄存器傳輸層,這兩層可充分發揮出VHDL面向高層的優勢。利用VHDL實現數字電路的實質是利用綜合工具將高層次描述轉化為低層次門級描述,其中綜合可分為三個層次:高層次綜合(High-Level Synthesis)、邏輯綜合(Logic Synthesis)和版圖綜合(Layout Synthesis)。

3.基于VHDL的FPGA系統行為級設計

具體包括以下重要環節:設計輸入(Design Entry)、設計綜合(Design Synthesis)、設計約束(Design Constraints)、設計實現(Design Implement)、設計仿真(Design Simulation)和器件編程(Device Programming)。

設計輸入主要采用HDL(硬件描述語言)、ECS(Engineering Schematic Capture,原理圖編輯器)和FSM(Finite State Machine,有限狀態機);

設計綜合就是依據邏輯設計描述和約束條件,利用開發工具進行優化處理,將HDL文件轉變為硬件電路實現方案,其實質就是優化設計目標的過程;

設計約束主要包括設計規則約束、時間約束、面積約束三種,通常時間約束的優先級高于面積約束;

設計實現對于FPGA分為編譯規劃、布局布線(PAR,Place And Route)、程序比特流文件產生;對于CPLD則是編譯、配置、比特流文件產生;

設計仿真分為功能仿真和時序時延仿真。功能仿真在設計輸入之后、綜合之前進行,只進行功能驗證,又稱為前仿真。時序時延仿真在綜合和布局布線之后進行,能夠得到目標器件的詳細時序時延信息,又稱為后仿真;

器件編程是指在功能仿真與時序時延仿真正確的前提下,將綜合后形成的位流編程下載到具體的FPGA/CPLD芯片中,又稱芯片配置。FPGA/CPLD編程下載通常可使用JTAG編程器、PROM文件格式器和硬件調試器三種方式,其中JTAG(Joint Test Action Group,聯合測試行動組)是工業標準的IEEE 1149.1邊界掃描測試的訪問接口,用作編程功能可省去專用的編程接口,減少系統引出線,有利于各可編程邏輯器件編程接口的統一,因此應用廣泛。

4.FPGA設計優化及方案改進

在FPGA設計中,必須首先明確HDL源代碼編寫非常重要;不同綜合工具包含的綜合子集不同致使有些HDL語句在某些綜合工具中不能綜合;同一邏輯功能可用不同HDL語句進行描述,但占用資源卻可能差別很大。同時應當深刻理解并發性是硬件描述語言與普通高級語言的根本區別,因而設計硬件電路不能受傳統順序執行思維的束縛。

此外,我們應當清楚速度優化與面積優化在FPGA設計中占有重要地位。對于大多數數字系統設計而言,速度常常是第一要求,但FPGA結構特性、綜合工具性能、系統電路構成、PCB制版情況及HDL代碼表述都會對工作速度產生重要影響。我們通過在電路結構設計中采用流水線設計、寄存器配平、關鍵路徑法可以進行速度優化。

(1)流水線設計

流水線(Pipelining)技術在速度優化中相當流行,它能顯著提高系統設計的運行速度上限,在現代微處理器、數字信號處理器、MCU單片機、高速數字系統設計中都離不開流水線技術。圖4與圖5是流水線設計的典型圖示,其中圖4未使用流水線設計,圖5采用了2級流水線設計,在設計中將延時較大的組合邏輯塊切割成兩塊延時大致相等的組合邏輯塊,并在這兩個邏輯塊中插入了觸發器,即滿足以下關系式:Ta=T1+T2,T1≈T2。通過分析可知,圖4中Fmax≈1/Ta;圖5中流水線第1級最高工作頻率Fmax1≈1/T1,流水線第2級最高工作頻率Fmax2≈1/T2≈1/T1,總設計最高頻率為Fmax≈Fmax1≈Fmax2≈1/T1,因此圖5設計速度較圖4提升了近一倍。

(2)寄存器配平(Register Balancing)

寄存器配平是通過配平寄存器之間的組合延時邏輯塊來實現速度優化,兩個組合邏輯塊延時差別過大,導致設計總體工作頻率Fmax取決于T1,即最大的延時模塊,從而使設計整體性能受限。通過對圖7設計進行改進,將延時較大的組合邏輯1的部分邏輯轉移到組合邏輯2中,成為圖8結構,以減小延時T1,使t1≈t2,且滿足T1+T2=t1+t2。寄存器配平后的圖8結構中Fmax≈1/t1》1/T1,從而提高了設計速度。

(3)關鍵路徑法

關鍵路徑是指設計中從輸入到輸出經過的延時最長的邏輯路徑,優化關鍵路徑是提高設計工作速度的有效方法。圖9中Td1》Td2,Td1》Td3,關鍵路徑為延時Td1的模塊,由于從輸入到輸出的延時取決于延時最長路徑,而與其他延時較小的路徑無關,因此減少Td1則能改善輸入到輸出的總延時。

在優化設計過程中關鍵路徑法可反復使用,直到不可能減少關鍵路徑延時為止。許多EDA開發工具都提供時序分析器可以幫助找到延時最長的關鍵路徑,以便設計者改進設計。對于結構固定的設計,關鍵路徑法是進行速度優化的首選方法,可與其他方法配合使用。

在FPGA設計中,面積優化實質上就是資源利用優化,面積優化有多種實現方法,諸如資源共享、邏輯優化、串行化,其中資源共享使用較多,下面舉例說明。

在利用FPGA設計數字系統時經常遇到同一模塊需要反復被調用,例如多位乘法器、快速進位加法器等算術模塊,它們占用芯片資源很多,使系統成本及器件功耗大幅上升,因而使用資源共享技術能夠顯著優化資源。圖10和圖11是資源共享的一個典型實例,由圖可見使用資源共享技術節省了一個多位乘法器,從而達到減少資源消耗、優化面積的目的。

最后針對FPGA的設計實現提出一些改進方案,FPGA實現分為編譯規劃、布局布線(PAR,Place And Route)、程序比特流文件生成三個階段,當設計不滿足性能指標或不能完全布線時,可進行以下改進工作:

● 使用定時約束(Timing Constraints);

● 增大布局布線級別(PAR Effort);

● 對關鍵通路(Critical Paths)的數字邏輯重新設計;

● 運行重布線(Re-entrant Routing);

● 運行MPPR(Multi-Pass Place & Route,多通路布局布線);

● 運行平面布局(Floorplan)查看布局圖及連通性。

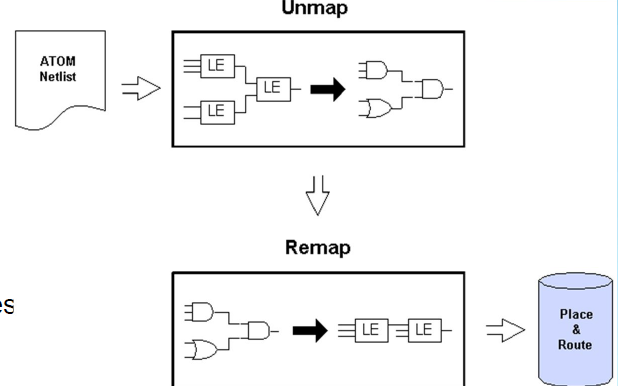

下面重點介紹Re-entrant Routing與MPPR,它們都可改進布局布線結果,提高系統性能。其中Re-entrant Routing是指已運行過PAR后再次運行PAR,但跳過布局過程直接進行布線,如圖12所示。MPPR則是根據不同功耗表(Cost tables)來運行PAR多次,通過對每一個PAR迭代評分來確定最好路徑并保留,其中評分依據是未布線的連線個數、連線延遲與時序約束。

結束語

當今社會,集成電路產業已成為高技術產業群的核心戰略產業,已逐漸演化為設計、制造、封裝、測試協調發展的產業結構,它正進入以知識產權為創新核心的新時期。這標志著集成電路產業的競爭已由技術競爭、資本競爭進入到智力和知識產權競爭的高級階段。

FPGA在集成電路設計應用中占有重要地位,現場可編程性是FPGA最突出的優點。用戶通過利用強大的開發工具,能在最短時間內對FPGA內部邏輯進行反復設計及修改,直至滿意為止,這大大縮短了產品設計開發周期,提高了最終產品性能。因而FPGA以其獨有的技術優勢在電子設計領域得到越來越廣泛的應用。隨著科學發展及工藝進步,作為重中之重的集成電路設計業必將遇到更大的挑戰及發展機遇。

-

FPGA

+關注

關注

1645文章

22050瀏覽量

618480 -

計算機

+關注

關注

19文章

7663瀏覽量

90804 -

eda

+關注

關注

71文章

2930瀏覽量

177975

發布評論請先 登錄

EDA技術特征與FPGA設計應用及優化策略分析

EDA技術特征與FPGA設計應用及優化策略分析

評論