1 引言

在通信領域尤其是無線通信方面,隨著技術不斷更新和新標準的發布,設計者需要一個高速通用硬件平臺來實現并驗證自己的通信系統和相關算法。FPGA(現場可編程門陣列)作為一種大規模可編程邏輯器件,體系結構和邏輯單元靈活、集成度高、適用范圍寬,并且設計開發周期短、設計制造成本低、開發工具先進并可實時在線檢驗,廣泛應用于產品的原型設計和產品生產。

與傳統的DSP(數字信號處理器)或GPP(通用處理器)相比,FPGA在某些信號處理任務中表現出非常強的性能,具有高吞吐率、架構和算法靈活、并行計算、分配存儲以及動態配置等優勢,因此非常適合用于設計驗證高速通信系統的基帶處理部分。

本文提出一種基于Xilinx公司Virtex-Ⅱ系列300萬門級FPGA器件的通信系統基帶設計驗證平臺,適用于高速通信系統基帶的原型設計和相關算法的實現,并已成功應用于基于IEEE 802.1la的OFDM基帶系統設計。

2 系統平臺組成和功能

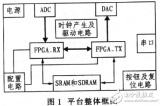

通信系統基帶設計驗證平臺主要有以下組成部分:電源部分、FPGA和外圍電路、時鐘和復位電路以及模數和數模轉換電路。平臺整體框圖見圖1。

各單元模塊的功能如下:

電源部分:負責給FPGA和其他電路供電。

FPGA和外圍電路:主要由兩片300萬門級的FPGA器件構成,配置電路用于啟動后完成對FPGA的自動配置。其他主要外圍電路還有存儲器(SRAM和SDRAM)及串口通信電路。

時鐘和復位電路:為FPGA提供系統時鐘和復位信號。

模數和數模轉換電路:主要是1片用于將數字信號轉換成模擬信號的ADC,以及l片將模擬信號轉換成數字信號的DAC。

整個系統平臺的工作原理是:兩片FPGA分別設計成發射機(圖l中的FPGA_TX)和接收機(圖l中的FPGA_RX)。測試向量進入發射機后,經過基帶編碼和調制,通過DAC轉換成基帶模擬信號。ADC及接收電路接收電纜傳輸過來的信號,將其轉換成數字信號,經接收機解調和解碼后還原為原始數據,并與測試向量比較,獲得誤碼率等性能指標。

3 功能單元的電路實現

3.1 FPGA及其配置電路

VirtexⅡ系列FPGA是Xilinx公司推出的針對高性能可編程解決方案的首款平臺級FPGA器件。Virtex-Ⅱ系列器件采用先進的O.15 μm/0.12 μmCMOS 8層金屬混合工藝設計,內核電壓為1.5 V,根據輸入輸出參考電壓的不同設計可支持多種接口標準,內部時鐘頻率可達420 MHz,被認為是高速低耗的理想設計。

Virtex-Ⅱ系列器件特性:

(1)內部時鐘頻率可達420 MHz,輸入輸出速率可高達840MHz。

(2)內嵌18x18專用硬件乘法電路和超前進位邏輯鏈(Look Ahead Carry)實現高性能的算術處理功能。

(3)高性能的內部存儲器Select RAM,每個塊存儲器容量為18 KB。最多提供3 MB的塊存儲資源以及1.5 MB的分布式存儲器資源。

(4)多達12個數字時鐘管理模塊(Digital Clock Manager,DCM)和16個全局時鐘多路復用緩沖器,提供了靈活的系統時鐘解決方案。

(5)Virtex-Ⅱ采用數控阻抗匹配技術(Digital Controlled Impedance,DCI),可減小因阻抗匹配問題而造成的系統不穩定,并減小PCB因終端匹配電阻導致的復雜性。

本平臺采用兩片300萬門的Virtex-Ⅱ FPGA器件,型號為XC2V3000C,從兼容性和擴展性考慮,選用FFl152封裝,該封裝與XC2V4000/6000/8000的FPGA引腳兼容,便于系統升級。

Virtex-ⅡFPGA的配置信息存儲于SRAM中,掉電后配置信息丟失,上電后需要重新配置下載。Virtex-Ⅱ系列器件配置有5種模式,JTAG/Botmdarv Scan、Master Scrial、Slave Serial、Master SelectMAP、Slave SelectMAP。其中Master SelectMAP和MasterSerial需要使用Xilinx專用的PROM。

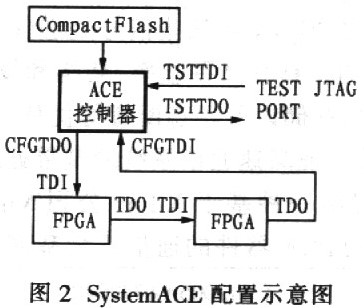

本設計采用JTAG/Boundary Scan配置模式,主要通過四個專用配置信號線完成所有配置任務。提供兩種配置方式,一是在線下載配置,通過下載電纜將FPGA的JTAG口與計算機并口相連,使用軟件完成在線下載。另一種是采用SystemACE方案,上電后,通過SystemACE控制器讀取CF存儲器中的配置文件,通過JTAG配置相連的FPGA器件。

SystemACE CompactFlash(CF)使用基于CFACompactFlash標準的存儲器,由CompactFlash存儲模塊和ACE控制器組成。ACE控制器具有內置的控制邏輯,可以通過任何一個ACE控制器接口(CompactFlash接口、CFGJTAG接口、TESTJTAG接口和系統微處理器接口)對目標FPGA鏈進行配置。其中CompactFlash接口提供對CompactFlash存儲卡的支持。單片Virtex-ⅡFPGA所需的配置數據大小為300 Kbit-29.O Mbit,這意味著使用一個Svs-temACE CF方案可以配置超過250片最大容量的Virtex-Ⅱ系列FPGA。設計者可以根據需要靈活地改變ACE Flash的密度。

SystemACE配置示意圖如圖2所示。完成FP-GA設計后,通過軟件生成所設計的下載配置文件,通過CF卡讀寫器將文件置于CF存儲卡中。當平臺上電后,ACE控制器讀取CF卡中的配置文件,通過JTAG鏈將數據下載到各FPGA,完成自動配置。也可以通過JTAG下載電纜連接TEST JTAG接口,直接對FPGA進行在線配置。

3.2 時鐘電路和復位及電壓監視電路

本平臺采用兩個相互獨立的有源晶體振蕩器提供20 MHz時鐘,分別作為接收機和發射機的時鐘源。由于板上多處地方需要20 MHz時鐘(如ADC和DAC),而僅靠晶體振蕩器供給時鐘除導致驅動力較弱外,還可能會產生較大時鐘偏移或抖動。選用時鐘驅動器IDT74FCT38074為系統提供時鐘,這是一款3.3 V供電,CMOS工藝的1驅4時鐘驅動器,輸入時鐘最高為166 MHz,同時提供4路低偏移同相時鐘。通過兩片IDT74FCT38074,分別為接收機和發射機各個模塊提供精確時鐘。輸入時鐘進入FPGA后又可以通過DCM的分頻倍頻處理,為FP-GA內部各個功能模塊提供所需的時鐘。

在Virtex-Ⅱ器件內部,所有DCM模塊通過時鐘多路復用器邏輯分配到器件內部。所提供的16個全局時鐘緩沖器可實現16個時鐘域的控制,保證了DCM模塊的時鐘輸出具有最小的傳輸延遲(Skew)。

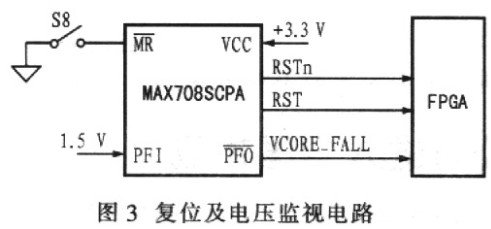

復位及電壓監視電路采用MAX708SCPA,提供上電自動復位及手動復位。MAX708SCPA的PFI引腳為監視電壓輸入端,當PFI輸入電壓低于1.25 V時,PFO引腳輸出低電平表示電壓過低,本設計中用于監視FPGA 1.5 V內核電壓。開關按鈕S8提供手動復位。其電路示意圖如圖3所示。

3.3 數模和模數轉換電路

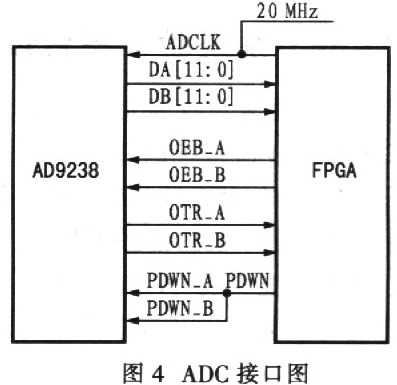

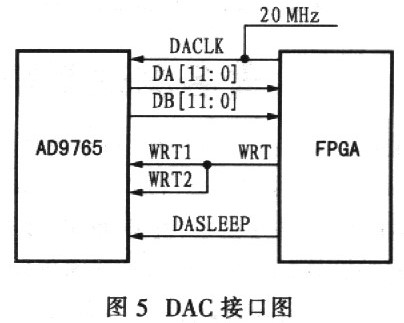

本平臺用于驗證通信基帶系統,需要將發射機輸出的I路、Q路信號通過數模轉換器(DAC)轉換成模擬信號,接收機則通過模數轉換器(ADC)將接收信號轉換成數字信號。本平臺設計采用的ADC和DAC分別為ADI公司的AD9238和AD9765。

AD9238是雙通道12位ADC。速度等級分為20MS/s、40MS/s和65MS/s。功耗為180mW“600mW,適用于要求低功耗和較小PCB面積的應用。AD9238的信噪比(SNR)為70 dB,無雜散信號動態范圍(SFDR)為85 dBc。帶有片內寬帶差分采樣保持放大器(SHA),允許用戶選擇多種輸入范圍和失調電壓,包括單端輸入。AD9765是雙端口、高速率、雙通道、12 bit的CMOS數模轉換器(DAC)。它集成了2個高性能的12 bit TxDAC。更新速率可達125 MS/s,無雜散信號動態范圍(SFDR)為75 dBc,O.1%的增益偏移匹配率。輸出為差分電流、滿幅度為20mA。

本設計中,AD9238工作在2Vp-p差分工作模式,采用內部參考電壓,兩通道工作在共享電壓參考模式。輸入差分幅度為2 V。信號時鐘輸入可以采用時鐘驅動器的20MHz輸出或由FPGA提供,最高采樣率為40 MS/s。AD9238的兩通道選擇AD8138作為運放驅動器,為ADC提供差分輸入信號。AD9765工作在雙端口模式,兩通道增益控制可分別調整,采用內部l.2 V參考電壓。時鐘輸入也可以采用時鐘驅動器的20 MHz輸出或由FPGA提供。AD9238和AD9765與FPGA的連接示意圖分別如圖4和圖5所示。

3.4 電源電路

本系統正常工作需要兩種供電電壓。一種為FPGA器件的內核電壓1.5 V;另一種為FPGA器件的輸入輸出接口電壓3.3 V,該電壓同時還用于其他器件供電。

本設計采用適合FPGA應用的低電壓、大電流線性穩壓器(LDO)供電方案。電源輸入采用標準的ATX電源接口,可以由ATX電源供電,其中+12 V輸入直接給風扇供電,用于FPGA散熱。+5 V輸入通過Tl公司的TPS75533和TPS75415分別轉換為3.3 V和l.5 V電壓輸出。TPS75533是一款最低壓差可為250 mV的LDO,可提供3.3 V,5 A輸出。TPS75415可提供1.5 V,2 A輸出,其快速瞬態響應可有效改善系統性能。LDO采用線性調節原理,輸出紋波很小,外圍電路簡單,只要求外接輸入和輸出電容即可工作。缺點是電壓轉換效率不高,發熱量大,對散熱控制方面要求較高。TPS75533采用TO-220封裝,可以通過背部散熱片有效散熱,而TPS75415采用PowerPADTM的TSSOP小封裝,在提供2W散熱功率,提高散熱性的同時節省了占用面積。

3.3 V和1.5 V電壓之間加穩壓二極管和肖特基二極管構成的保護電路,保證FPGA的內核電壓與接口電壓之差在一定范圍內,防止器件損壞。

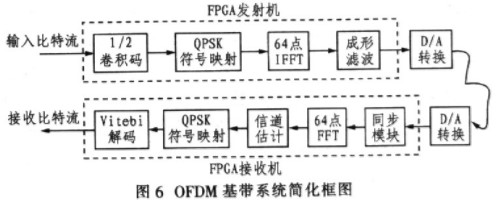

4 OFDM基帶系統驗證平臺設計

基于FPGA的通信系統基帶設計驗證平臺非常適用于高速無線通信系統的基帶設計。采用該平臺可驗證基于IEEE 802.1la的OFDM基帶系統的簡化原型設計。設計框圖如圖6所示。

經驗證,該平臺能實現OFDM原型機的發送和接收功能,并能有效驗證同步和信道估計算法的實際性能。

5 結束語

基于FPGA的通信系統基帶設計驗證平臺采用大容量、高性能的FPGA器件,為通信系統的基帶設計提供了一個有效的硬件實現平臺。基于FPGA的實現和驗證與計算機仿真相結合,將大大加速通信系統基帶部分的快速原型設計,極大地方便了對實時性和運算量有較高要求的各類算法的驗證。

-

dsp

+關注

關注

556文章

8157瀏覽量

357461 -

FPGA

+關注

關注

1645文章

22048瀏覽量

618329 -

無線

+關注

關注

31文章

5555瀏覽量

176016

發布評論請先 登錄

一種適用于無線通信系統的半盲ICA算法

【電子書】無線通信FPGA設計(final)PDF

求大神分享適用于2G/3G/4G的無線終端基帶芯片

如何利用FPGA設計摩爾斯電碼的無線通信發射模塊?

常見的無線通信協議有哪些

適用于NFC和驗證的子系統設計

基于FPGA的通信系統基帶驗證平臺設計方案解析

適用于高速無線通信系統的FPGA基帶驗證平臺的設計

適用于高速無線通信系統的FPGA基帶驗證平臺的設計

評論