1 、引言

便攜式、小型的儀表和設備是一個非常重要的應用領域,在未來一段時間內會有比較大的市場。而FPGA等現場可編程器件也是正在興起與普及的一種器件,把FPGA更好地運用到上述儀表和設備中,可以減少這些儀器、設備的開發周期,大幅度提升這些儀器的性能,減少總成本和體積等。

在許多應用場合,如大型設備中的板卡,比較適合采用標準的FPGA編程電路。但是對于便攜式設備的應用場合,采用標準電路聯系FPGA與CPU需要消耗的資源太多。許多DSP芯片只有2個通用I/O引腳,所以如果能只使用1~2個引腳就完成FPGA編程功能,意義將非常重大。

2 、標準的FPGA編程電路

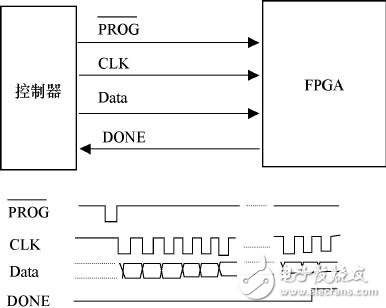

以Xilinx的Spartan系列FPGA為例,圖1是一個標準的編程電路。電路中控制器使用了4條控制信號線PROG,CLK,Data,DONE。首先Prog信號控制FPGA的初始化,一個Prog信號的低電平使FPGA進入編程狀態,在編程過程及以后的運行過程中,Prog信號保持高電平;在編程過程中,Data信號與CLK信號配合,在每個Clk信號的上升沿,FPGA鎖定/讀取一個Data信號,如此循環,直到控制器將需要編程的程序全部送到FPGA中;當FPGA正確接收到編程程序以后,就會產生一個DONE信號,通知控制器一切完畢。

該電路是Xilinx公司推薦的一個FPGA的標準電路,對于許多常規應用場合,它還是比較合適的,但是對于手持式儀表等尺寸非常小的設備,由于控制器本身只有1~2個I/O控制線,而上述標準電路占用4個I/O口,就有可能無法應用。

3 、精簡的FPGA編程方法

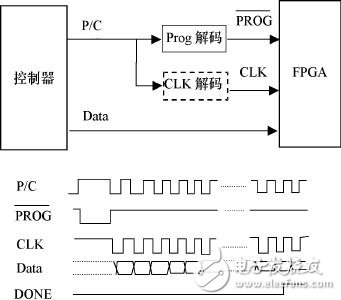

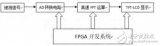

本文給出了一種精簡的FPGA編程電路如圖2所示。控制器的I/O控制信號線包括P/C和Data。P/C控制信號產生圖2中所示的波形,經過Prog解碼電路(如圖4所示)得到Prog信號,經過CLK解碼電路(在本例中也可以不經過),得到CLK信號,它們與Data一起組成完整的FPGA控制信號,完成對FPGA的編程控制。

圖1 通常的FPGA下載電路

圖2 精簡的FPGA下載電路之一

該電路只使用2根I/O控制信號線,比標準編程電路要少,利用特殊控制信號的編碼與解碼,得到完成FPGA的編程工作。

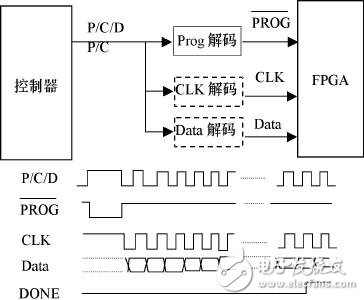

更進一步,也可以只使用一個I/O控制信號線,如圖3所示,使用Prog解碼電路(如圖4所示)、CLK解碼電路和Data解碼電路(如圖5所示),得到FPGA編程所必須的Prog信號、CLK信號和Data信號。該方法比圖2所示的電路所需要的控制線還要少。

圖3 精簡的FPGA下載電路之二

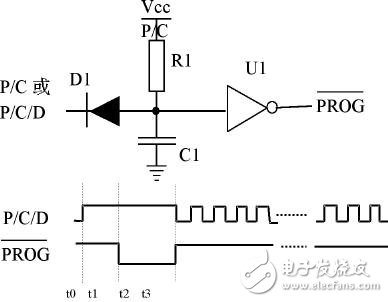

圖4 Prog解碼電路

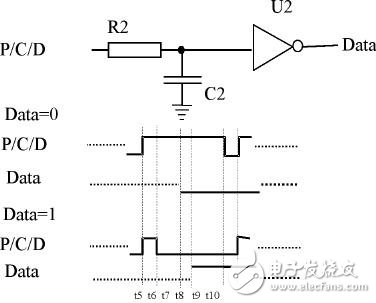

圖5 Data解碼電路

本方法利用比標準FPGA編程電路更少的I/O控制線,經過解碼電路的解碼得到FPGA編程所需要的控制信號。對于不同公司的產品,本方法只要稍加變動就可以使用。

4 、應用案例

以Xilinx的Spartan II系列產品為例,圖4為Prog控制信號解碼電路,圖5為Data信號解碼電路。不妨假定CLK信號的周期為Tclk,Prog解碼電路中的時間常數為tProg=R1*C1,Data解碼電路的時間常數為tData=R2*C2。

Prog控制信號解碼電路的原理: P/C信號或P/C/D信號由Prog編碼和CLK(Data)編碼組成,其中Prog編碼是一個周期比較長的高電平,見圖4的t2-t0,它大于Prog解碼電路的時間常數tProg,CLK(Data)編碼是周期比較短的脈沖,小于解碼電路的時間常數tProg,所以Prog信號可以被解碼得到,而其他不相關信號則被過濾掉。一般可以選擇Prog編碼周期t2-t0》5tProg,而CLK(Data)編碼周期t3-t2《1/5tProg。當FPGA編程結束以后,P/C信號,或者P/C/D信號應當立即復位,否則Prog會出現錯誤。

Data解碼電路的原理可以分成Data=0和Data=1兩種情況:

Data=“0時”,當P/C/D信號的前一個數據的上升沿t5結束,并保持一段時間,到達t6后,繼續保持高電平,經過大約tData(與先前狀態有關),Data控制信號線就會出現低電平,即信號0,為了更加可靠,可以等一段時間,到達時刻t9時P/C/D信號再給出一個負脈沖用于鎖定數據。當然負脈沖的寬度應當比較窄,否則Data信號會反轉,通常負脈沖寬度t10-t9《1/4tCLK。

Data=“1時”,當P/C/D信號的前一個數據的上升沿t5結束,并保持一段時間,到達t6后,立即進入低電平,經過大約tData(與先前狀態有關),Data控制信號線就會出現高電平,即信號1,為了更加可靠,可以等一段時間,到達時刻t10時,P/C/D信號再給出一個上升沿用于鎖定數據。

這樣Data信號也可以被正確地解碼出來。在本例中CLK信號無須專門的解碼電路,P/C/D信號可以直接作為CLK控制信號使用。

本方法經過實驗驗證,其中R1=10KW,C1=0.1mF, R2=1KW, C2=0.01mF,D1為1N5817,U1/U2為74HC14。當然也可以根據需要進行調整。

5 、結語

FPGA是一種功能非常強大,非常靈活的器件,正在向各種中、高檔的應用普及,采用本文提出的精簡FPGA編程方法,節省了控制器的I/O線,克服了FPGA在便攜式設備中應用的一個瓶頸。文中給出了其基本原理并通過了實驗,具有一定的使用價值。

-

FPGA

+關注

關注

1644文章

21991瀏覽量

615273 -

控制器

+關注

關注

114文章

17023瀏覽量

183289 -

編程

+關注

關注

88文章

3686瀏覽量

94958

發布評論請先 登錄

一種基于FPGA的UART實現方法設計

一種基于FPGA的DSU硬件實現方法

一種基于FPGA和MCU的總線轉換方案設計

一種基于FPGA的可配置FFT IP核實現設計

分享一種基于Actel Flash FPGA的高可靠設計方案

用FPGA實現糾錯編碼的一種方法

一種基于FPGA的數字頻譜儀設計與實現

一種基于CPLD加載FPGA的方案設計詳解

一種精簡FPGA編程電路的實現方案

一種精簡FPGA編程電路的實現方案

評論