基于軟件無線電的某機載多模式導(dǎo)航接收機能較好地解決導(dǎo)航體制不兼容對飛行保障區(qū)域的限制,但由于各體制信號差異較大,各自實現(xiàn)其硬件將相當(dāng)龐大,若對本系統(tǒng)中數(shù)字信號處理的核心FPGA芯片使用可重構(gòu)的配置方法,將導(dǎo)航接收機的多種模式以時分復(fù)用的方式得以實現(xiàn),可以重復(fù)利用FPGA的硬件資源,達到了縮小體積,減小功耗,增加靈活性和降低系統(tǒng)硬件復(fù)雜程度等目的。本系統(tǒng)中的核心器件是新一代高檔FPGA,適合于計算量大的數(shù)字信號處理,包含實現(xiàn)數(shù)字信號處理的DSP塊、數(shù)字鎖相環(huán)、硬件乘法器以及各種接口等多項技術(shù),支持遠程更新,但其配置數(shù)據(jù)大,實現(xiàn)較為復(fù)雜。采用CPLD+FLASH方案,有效的解決了這一問題。

1 FPGA及其可重構(gòu)技術(shù)簡介

現(xiàn)代高速度FPGA運行時需將其配置數(shù)據(jù)加載到內(nèi)部SDRAM中,改變SDRAM里面的數(shù)據(jù),可使FPGA實現(xiàn)不同的功能,即所謂的可重構(gòu)技術(shù)。可重構(gòu)技術(shù)包括靜態(tài)系統(tǒng)重構(gòu)和動態(tài)系統(tǒng)重構(gòu)。在FPGA處于工作狀態(tài)時對其部分配置數(shù)據(jù)進行更改稱為動態(tài)配置,否則稱為靜態(tài)配置。由于本系統(tǒng)在工作時需要改變整個FPGA功能,所以采用靜態(tài)配置。這種配置是完全的,它對整個FPGA的功能、參數(shù)完全更改,而且其引腳功能也被更改。

系統(tǒng)的關(guān)鍵部件為一片高檔密度FPGA EP2S30,其要求的一次配置數(shù)據(jù)達1.205MBytes,故其配置采用“Flash存儲器+CPLD主控器”的方案。

EP2S30支持5種配置方案,即AS(Active Serial)模式、PS(Passive Serial)模式、FPP(Fast Passive Parallel)模式、PPA(Passive parallel Asynchronous)模式和JTAG配置模式等。為縮短配置時間,本系統(tǒng)采用FPP模式,配置數(shù)據(jù)不壓縮,使各配置數(shù)據(jù)長度一致,以便于分配Flash存儲空間,且只需要同數(shù)據(jù)率相同的時鐘信號。

2 可重構(gòu)系統(tǒng)硬件設(shè)計

2.1 芯片介紹

2.1.1 FPGA芯片

采用Altera公司StratixⅡ系列FPGA,具有多達33880個等價邏輯單元(LE)和13552個自適應(yīng)邏輯單元(ALM),支持可編程片上系統(tǒng)(SOPC),有多達1369Kbits片上RAM,支持NIOS嵌入式處理器,片上有多達16個DSP塊和64個18位×18位硬件乘法器以及6個PLL模塊,支持遠程更新。其片內(nèi)資源完全可以實現(xiàn)系統(tǒng)所需的數(shù)字下變頻(DDC)、幅度調(diào)制與解調(diào)、方位和距離脈沖形成以及控制信號的產(chǎn)生等。但其配置數(shù)據(jù)達1.205MBytes,要完成多模式可重構(gòu)配置,其配置數(shù)據(jù)存儲器必須有足夠大的空間。

2.1.2 Flash芯片

為實現(xiàn)快速配置,綜合存儲容量、工作電壓以及等各方面的要求,F(xiàn)lash芯片選用AMD公司AM29LV065,其為8M×8bits Flash存儲器,內(nèi)部被分為128個64Kbytes扇區(qū),可以存儲6套配置方案數(shù)據(jù)。支持3.3V電壓讀寫和擦除,支持扇區(qū)擦除和整片擦除,這一特性有利于實現(xiàn)某一配置數(shù)據(jù)單獨更改。地址不變時能自動進入休眠狀態(tài),將數(shù)據(jù)鎖存,從而減小功耗。

2.1.3 控制芯片

控制芯片采用Altera公司MAX7000AE系列CPLD EPM7064A,其具有ISP功能,為3.3V內(nèi)核,IO口靈活方便,避免了采用單片機作為控制芯片時IO口不夠用的問題。

2.2 硬件連接

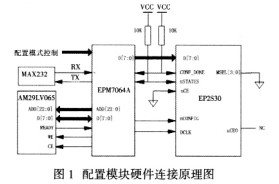

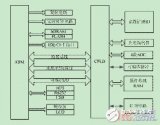

配置系統(tǒng)硬件連接如圖1所示。

配置系統(tǒng)中配置主控制器EPM7064A是整個配置系統(tǒng)的核心,它在數(shù)據(jù)加載過程中與PC機通訊,產(chǎn)生Flash命令控制字并將配置數(shù)據(jù)寫入Flash存儲器,同時對Flash存儲空間進行自動分配;在配置過程中根據(jù)系統(tǒng)的配置模式控制信號將Flash中的數(shù)據(jù)讀出并配置到FPGA中,同時完成FPGA配置所需的時序,并檢測FPGA的狀態(tài),若配置成功進入休眠狀態(tài)以節(jié)省功耗,若配置不成功將對FPGA進行復(fù)位并重新配置。

為簡化CPLD的控制時序,便于對FPGA進行自動配置,將Flash的存儲空間按順序劃分為6個塊,分別存儲6個配置數(shù)據(jù)。每個塊包含20個扇區(qū),1.25MBytes存儲空間。

3 CPLD控制部分軟件設(shè)計與實現(xiàn)

3.1 EPM7064A的Verilog HDL描述

EPM7064A是整個配置電路的核心,它完成Flash配置數(shù)據(jù)的加載和配置時序的產(chǎn)生。按照由上至下的進行設(shè)計,將其分成三個主要功能模塊,即數(shù)據(jù)加載過程中與PC機通訊的UART模塊、寫Flash時序產(chǎn)生模塊和配置時序產(chǎn)生模塊,分別由Verilog HDL硬件描述語言實現(xiàn)。

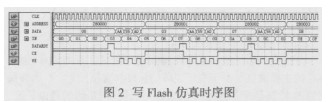

數(shù)據(jù)加載過程中,EPM7064A的UART模塊與PC機通訊,同時產(chǎn)生Flash編程控制字,將PC機送來的數(shù)據(jù)寫入指定的塊。其主要工作過程是串口模塊接收到一個字節(jié)數(shù)據(jù)后,其DATARDY有效,觸發(fā)Flash寫模塊先將三個控制字數(shù)據(jù)AA、55、A0寫入Flash,然后將接收到的數(shù)據(jù)寫入Flash。寫Flash仿真時序圖如圖2所示。

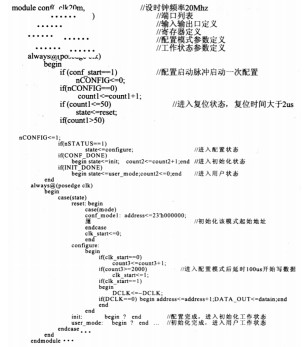

數(shù)據(jù)讀取和配置時序模塊的主要程序代碼如下:

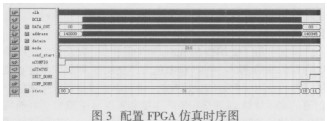

程序代碼在QUARTUSⅡ6.0下的仿真時序如圖3所示。其簡要工作過程是,外部conf_start信號啟動一次配置,EPM7064A將nCONFIG和nSTATUS信號拉低,F(xiàn)PGA進入復(fù)位狀態(tài),根據(jù)mode取得相應(yīng)的Flash初始地址,復(fù)位完成FPGA將nSTATUS釋放,延時大約100us后EPM7064開始給FPGA提供時鐘和數(shù)據(jù),直到將配置數(shù)據(jù)全部寫入FPGA,配置完成后FPGA將CONF_DONE釋放,表明配置完成,F(xiàn)PGA進入初始化狀態(tài),經(jīng)過內(nèi)部初始化后,INIT_DONE變高,表明FPGA進入工作狀態(tài),各引腳將根據(jù)用戶定義的狀態(tài)工作。若配置過程中nSTATUS被FPGA拉低,則表明有配置錯誤,重新進行配置,在任何工作狀態(tài)下外部指令都可以再次啟動配置。

3.2 配置文件的獲取

在FPGA的工程設(shè)計編譯后產(chǎn)生的.pof和.sof文件只能直接用于在PS模式下對FPGA進行配置,要用Flash存儲配置數(shù)據(jù),需要將配置數(shù)據(jù)轉(zhuǎn)換成.hexout或.hex格式,QUARTUSⅡ6.0提供兩種方法得到所需的文件,一是編譯時改變編譯選項自動生成所需文件,二是將已有配置文件轉(zhuǎn)換為所需文件格式。

4 結(jié)束語

將可重構(gòu)配置方法成功應(yīng)用于某導(dǎo)航接收機中,充分利用了硬件資源。這種可重構(gòu)配置方法能根據(jù)指令自動更改FPGA配置程序,重構(gòu)系統(tǒng)功能,實現(xiàn)了多模式導(dǎo)航體制融為一體,系統(tǒng)靈活性和可擴展性大大增強,以較低的成本實現(xiàn)復(fù)雜系統(tǒng),具有一定的工程實用價值。

-

FPGA

+關(guān)注

關(guān)注

1642文章

21920瀏覽量

612161 -

無線電

+關(guān)注

關(guān)注

60文章

2161瀏覽量

117482 -

導(dǎo)航

+關(guān)注

關(guān)注

7文章

542瀏覽量

42931

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA可重構(gòu)設(shè)計的結(jié)構(gòu)基礎(chǔ)

基于FPGA的可重構(gòu)系統(tǒng)結(jié)構(gòu)分析

cpld與flash配置fpga

有什么FPGA可重構(gòu)方法可以對EPCS在線編程?

用DSP實現(xiàn)CPLD多方案現(xiàn)場可編程配置

用DSP實現(xiàn)CPLD多方案現(xiàn)場可編程配置

基于DSP+CPLD可重構(gòu)數(shù)控系統(tǒng)的設(shè)計

基于ARM和CPLD的可重構(gòu)檢測系統(tǒng)設(shè)計

基于DSP+CPLD可重構(gòu)數(shù)控系統(tǒng)的設(shè)計

基于DSP和CPLD可重構(gòu)數(shù)控系統(tǒng)的設(shè)計與仿真

使用CPLD和Flash實現(xiàn)FPGA的配置

基于CPLD的FPGA快速動態(tài)重構(gòu)設(shè)計

采用ARM和CPLD結(jié)構(gòu)的檢測系統(tǒng)可重構(gòu)設(shè)計方法

采用CPLD+FLASH方案的可重構(gòu)配置方法

采用CPLD+FLASH方案的可重構(gòu)配置方法

評論