引言

隨著電子技術(shù)的發(fā)展,當(dāng)前數(shù)字系統(tǒng)的設(shè)計(jì)正朝著速度快、容量大、體積小、重量輕的方向發(fā)展。推動(dòng)該潮流迅猛發(fā)展的引擎就是日趨進(jìn)步和完善的高密度現(xiàn)場(chǎng)可編程邏輯器件設(shè)計(jì)技術(shù)。高密度現(xiàn)場(chǎng)可編程邏輯器件(CPLD/FPGA)能夠?qū)⒋罅窟壿嫻δ芗捎谝粋€(gè)單片IC之中,對(duì)基于E2PROM(或FlashMemory)工藝的器件,配置數(shù)據(jù)在掉電后不會(huì)丟失,可以直接采用ByteBlaster并口下載電纜對(duì)他們進(jìn)行配置,但基于該架構(gòu)的器件的集成度較低,一般在10萬(wàn)門以下;然而對(duì)基于SRAM工藝的器件,配置數(shù)據(jù)在器件掉電后會(huì)丟失,但基于該架構(gòu)的器件的集成度相對(duì)較高,一般在1萬(wàn)門以上。

由于當(dāng)前項(xiàng)目開發(fā)中所需使用的可編程邏輯器件的集成度要求越來越高,基于SRAM工藝的器件得到越來越廣泛的使用,那么此時(shí)如何將配置數(shù)據(jù)成功地寫入目標(biāo)器件,并且保證其在掉電再上電后能夠自動(dòng)恢復(fù)配置數(shù)據(jù),成為電子設(shè)計(jì)工程師能否正確使用基于SRAM工藝的器件必須掌握的一項(xiàng)技術(shù)。

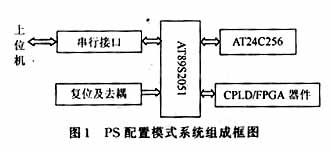

2系統(tǒng)組成

該系統(tǒng)的硬件電路由AT89S2051單片機(jī)、AT24C256串行E2PROM,MAX232串行接口電路、復(fù)位及去耦合電路和被配置CPLD/FPGA器件組成,如圖1所示。

3系統(tǒng)硬件設(shè)計(jì)

3.1芯片選型

(1)單片機(jī)單片機(jī)采用ATMEL公司生產(chǎn)的AT89S2051單片機(jī),該芯片與MCS51系列單片機(jī)兼容。內(nèi)含:2kBFlashE2PROM,128BRAM,15根I/O引線,2個(gè)16位定時(shí)器/計(jì)數(shù)器,1個(gè)5向量?jī)杉?jí)中斷結(jié)構(gòu),1個(gè)全雙工串行口和1個(gè)精密模擬電壓比較器等。

(2)串行E2PROM由于基于SRAM工藝的可編程邏輯器件(CPLD/FPGA)的配置數(shù)據(jù)在掉電后會(huì)丟失,需要外加存儲(chǔ)器以保存配置數(shù)據(jù)。為了盡量減小電路板的面積,選用8腳的串行E2PROMAT24C256。AT24C256是ATMEL公司生產(chǎn)的2線制串行電可擦寫只讀存儲(chǔ)器,具有自定時(shí)寫周期特性,容量32kB。該器件特別適合于對(duì)功耗有嚴(yán)格要求的應(yīng)用場(chǎng)合。

(3)通信接口采用MAXIM公司生產(chǎn)的串行接口芯片MAX232將PC機(jī)與下載配置電路連接起來。下載配置電路通過該串口接收PC機(jī)下傳的命令,執(zhí)行相應(yīng)的操作再將處理結(jié)果上傳到PC機(jī)。MAX232是通用+5V供電的多通道RS232總線收發(fā)器,尤其適合在電池供電的系統(tǒng)中應(yīng)用。

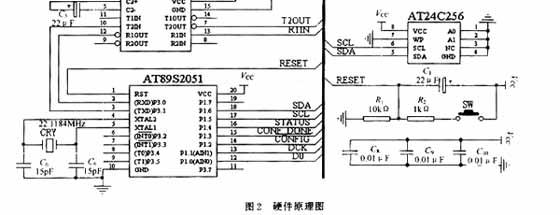

3.2硬件原理圖

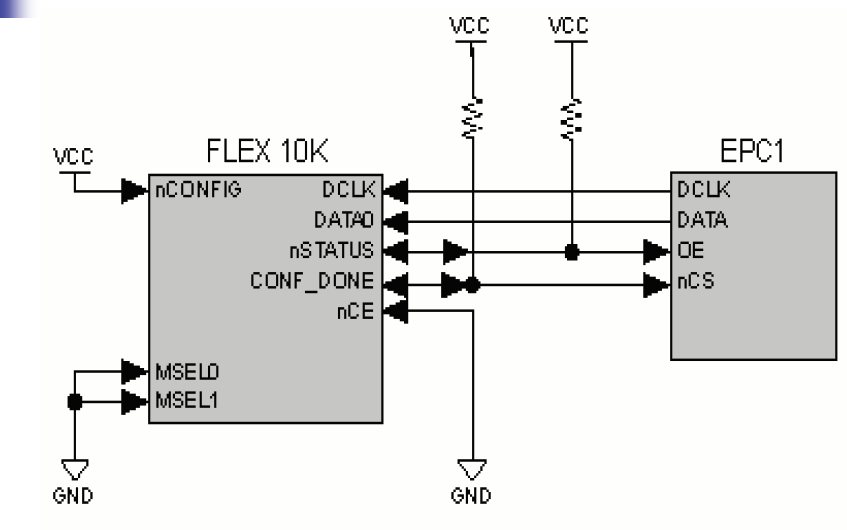

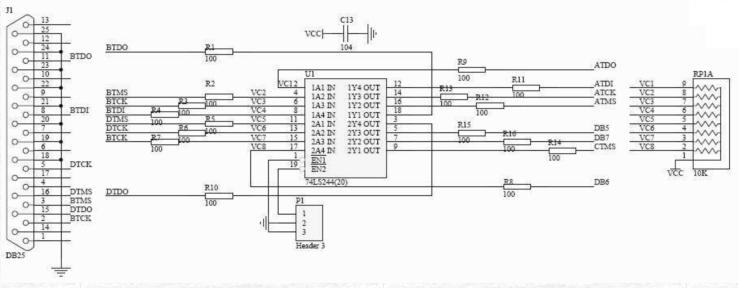

硬件原理如圖2所示。上電后,單片機(jī)首先調(diào)用子程序完成如下操作:將掉電前已經(jīng)存儲(chǔ)在AT24C256串行E2PROM中的器件配置文件讀出;采用被動(dòng)串行模式(PS)將該文件配置到CPLD/FPGA器件中,從而實(shí)現(xiàn)器件掉電再上電后自動(dòng)恢復(fù)配置數(shù)據(jù)的功能。然后,單片機(jī)就會(huì)工作在動(dòng)態(tài)停機(jī)狀態(tài),在此過程中,單片機(jī)可以響應(yīng)串口中斷。

如果單片機(jī)響應(yīng)串口中斷并且接收到一個(gè)數(shù)據(jù),那么單片機(jī)首先判斷該數(shù)據(jù)所表示的命令類型,若是配置命令,單片機(jī)就進(jìn)入配置狀態(tài)。在配置狀態(tài)下,單片機(jī)一邊接收配置數(shù)據(jù),一邊將這些數(shù)據(jù)寫到CPLD/FPGA器件中;若是寫E2PROM命令,單片機(jī)就進(jìn)入寫E2PROM狀態(tài),此時(shí)單片機(jī)會(huì)一邊接收配置數(shù)據(jù),一邊將這些數(shù)據(jù)寫到配置用E2PROM中(注意此時(shí)這些數(shù)據(jù)并沒有被配置到CPLD/FPGA器件中);若是讀E2PROM命令,單片機(jī)就進(jìn)入讀E2PROM并配置CPLD/FPGA器件狀態(tài),此時(shí)單片機(jī)會(huì)一邊讀E2PROM中的配置數(shù)據(jù),一邊將讀出的配置數(shù)據(jù)寫到CPLD/FPGA器件中。

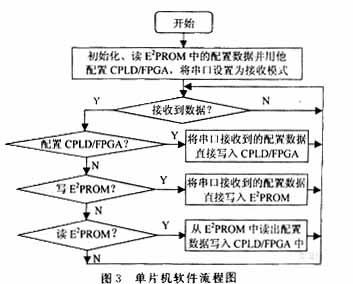

4系統(tǒng)軟件設(shè)計(jì)

軟件包括:主程序、下載配置子程序、寫E2PROM子程序、讀E2PROM子程序及通用延時(shí)子程序構(gòu)成。其軟件流程圖如圖3所示。

現(xiàn)將以上所提及的各個(gè)子程序的用途簡(jiǎn)介如下:

下載配置子程序的作用是將從串口接收的配置數(shù)據(jù)直接寫到目標(biāo)器件中,即直接寫到可編程邏輯器件(CPLD/FPGA)中。

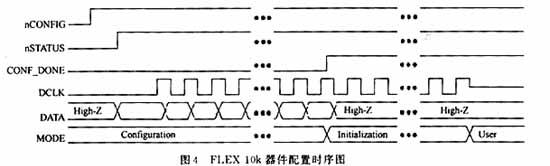

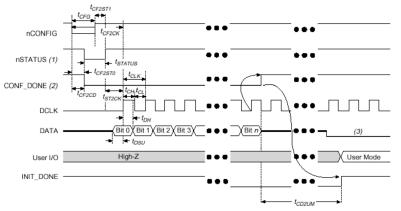

在編寫該子程序時(shí),必須注意目標(biāo)器件的寫入時(shí)序。必須根據(jù)目標(biāo)器件生產(chǎn)廠家提供的時(shí)序圖,用單片機(jī)語(yǔ)言編程將其配置時(shí)序準(zhǔn)確地描述出來,只有這樣才能正確地將配置數(shù)據(jù)寫入到目標(biāo)器件中。例如,我們?nèi)粢_配置ALTERA公司生產(chǎn)的FLEX10k系列器件,就必須嚴(yán)格遵守以下時(shí)序圖,如圖4所示。

寫E2PROM子程序的作用是將從串口接收的配置數(shù)據(jù)直接寫到AT24C256串行E2PROM中保存起來,以備需要時(shí)可以用這些保存的數(shù)據(jù)重新配置器件。讀E2PROM子程序的作用是從AT24C256中將配置數(shù)據(jù)讀出,同時(shí)將這些配置數(shù)據(jù)寫到目標(biāo)器件中,以實(shí)現(xiàn)對(duì)目標(biāo)器件的重新配置。

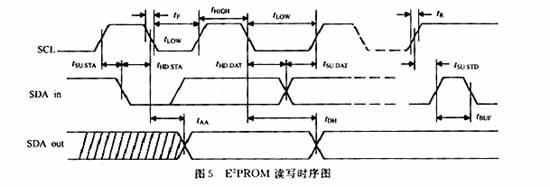

在編寫這兩個(gè)子程序時(shí),必須注意AT24C256的數(shù)據(jù)寫入和數(shù)據(jù)讀出時(shí)序,只有嚴(yán)格遵守該時(shí)序圖,才能正確地對(duì)該存儲(chǔ)器進(jìn)行讀寫操作。其讀寫時(shí)序如圖5所示。

通用延時(shí)子程序可以靈活地設(shè)定延時(shí)時(shí)間間隔。當(dāng)程序中需要延時(shí)的時(shí)候只要先給該子程序提供一個(gè)延時(shí)時(shí)間常數(shù),再調(diào)用延時(shí)子程序即可。例如,通常在系統(tǒng)復(fù)位時(shí)為了讓處理器復(fù)位后系統(tǒng)中其他器件能可靠復(fù)位而調(diào)用的上電延時(shí)子程序就可以采用該通用延時(shí)子程序來實(shí)現(xiàn)。

5結(jié)語(yǔ)

本系統(tǒng)可用于配置所有ALTERA公司生產(chǎn)的基于SRAM架構(gòu)的CPLD器件和XILINX公司生產(chǎn)的基于SRAM架構(gòu)的FPGA器件以及其他主流器件制造公司生產(chǎn)的基于SRAM架構(gòu)的器件,具有很強(qiáng)的通用性。由于該電路使用的元器件非常少,也可以將其制作成面積很小、便于攜帶的通用下載配置板使用。該下載配置電路經(jīng)本人實(shí)際制作、調(diào)試、使用,其工作穩(wěn)定可靠,具有很好的應(yīng)用前景。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22034瀏覽量

617848 -

單片機(jī)

+關(guān)注

關(guān)注

6067文章

44973瀏覽量

649943 -

cpld

+關(guān)注

關(guān)注

32文章

1257瀏覽量

171434

發(fā)布評(píng)論請(qǐng)先 登錄

FPGA/CPLD與單片機(jī)相比有哪些優(yōu)勢(shì)?

采用AT89S2051單片機(jī)配合串行E2PROM存儲(chǔ)器實(shí)現(xiàn)CPLD/FPGA器件的被動(dòng)串行模式的下載配置

FPGA和單片機(jī)串行通信接口的實(shí)現(xiàn)

單片機(jī)與FPGA CPLD總線接口邏輯設(shè)計(jì)

基于單片機(jī)的CPLD/FPGA被動(dòng)串行下載配置的實(shí)現(xiàn)

基于單片機(jī)的Cyclone系列FPGA配置方法

用單片機(jī)配置CPLD器件

FPGA器件的在線配置方法

ALTERA CPLD器件的配置與下載

使用CPLD和Flash實(shí)現(xiàn)FPGA的配置

FPGA與單片機(jī)實(shí)現(xiàn)數(shù)據(jù)串行通信的解決方案

微處理器系統(tǒng)中連接簡(jiǎn)單的被動(dòng)串行配置方法和被動(dòng)并行異步配置方法

FPGA教程之CPLD和FPGA的配置與下載的詳細(xì)資料說明

如何采用單片機(jī)實(shí)現(xiàn)CPLD/FPGA器件的被動(dòng)串行模式的下載配置

如何采用單片機(jī)實(shí)現(xiàn)CPLD/FPGA器件的被動(dòng)串行模式的下載配置

評(píng)論