1 引言

CPLD稱為復雜可編程邏輯設計芯片,它是大規模可編程器件,具有高集成度、高可靠性、高速度的特點。CPLD是利用EDA技術進行電子系統設計的載體。硬件描述語言是EDA技術進行電子系統設計的主要表達手段,VHDL語言是常用的硬件描述語言之一;軟件開發工具是利用EDA技術進行電子系統設計的智能化的自動化設計工具,常用開發工具有QuartusⅡ,Ispexpert,Foundation等。CPLD以高速、高可靠性、串并行工作方式等特點在電子設計中廣泛應用。它打破了軟硬件之間的界限,加速了產品的開發過程。同樣單片機具有性價比高、功能靈活、良好的數據處理能力等特點。CPLD芯片與單片機結合在高性能儀器儀表中應用廣泛。

1 電路的仿真設計

1.1 硬件電路功能

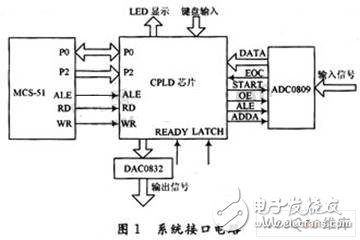

用一片MCS-51芯片、一片CPLD/FPGA芯片、模/數轉換器ADC0809和數/模轉換器DAC0832構成一個數據采集系統,并用CPLD/FPGA實現數據采樣、D/A轉換輸出、有關數據顯示的控制,單片機完成對A/D轉換數據運算。電路如圖1所示。

系統功能如下:系統按一定速率采集輸入電壓U1,經AD0809轉換為8位數字量data;輸入數據與通過CPLD/FPGA采樣后輸入單片機進行相關運算,最后通過CPLD/FPGA送至DAC0832轉換為△U;數據采集和處理均在數據采集系統控制器的管理下有序進行。工作速率由時鐘信號CLK的速率決定。

1.2 單片機與CPLD/FPGA接口設計

單片機采用以總線方式與可編程芯片進行數據與控制信息通信,此方式有許多優點:

(1)速度快。其通信工作時序是純硬件行為,對于MCS-51單片機只需一條單字節指令就能完成所需的讀/寫時序如MOV@DPTR A和MOV A@DPTR。

(2)節省CPLD芯片的I/O口線。如果將圖中的譯碼器設置足夠的譯碼輸出以及安排足夠的鎖存器就能僅通過19根I/O口線在FPGA/CPLD與單片機之間進行各種類型的數據與控制信息交換。

(3)相對于非總線方式單片機的編程簡捷控制可靠。

(4)在FPGA/CPLD中通過邏輯切換單片機易于與SRAM或ROM接口。這種方式首先由FPGA/CPLD與接口的高速A/D等器件進行高速數據采樣并將數據暫存于SRAM中。采樣結束后通過切換使單片機與SRAM以總線方式進行數據通信以便發揮單片機強大的數據處理能力。

系統工作過程如下:ALE為地址鎖存使能信號,當下降沿來時,將P0口將低8位地址送人可編程芯片CPLD/FPGA中的地址鎖存器,然后在P2口和P0口形成的16位地址及WR信號共同作用下,將P0口的數據送入可編程芯片。單片機通過兩條指令MOVXDPTR#ADDR和MOVX@DPTR A將數據寫入芯片。在P2口和P0口形成的16位地址及RD信號共同作用下,將AD0809轉換后數據data送入單片機的P0口。單片機通過兩條指令MOVX DPTR#ADDR和MOVXA@DPTR將數據讀入P0口。設置A/D轉換器件片選信號ad_e和DA轉換器件片選信號da_e,設置數據輸入/輸出口data[7..0]。單片機與FPGA通信接口程序(名為MCS51)通過編譯后,生成的邏輯符號如圖2所示。

CPLD使用EPM7128時鐘為16 MHz有源晶振,首先使用CLK對復位信號采樣,8051的復位信號要求是高電平維持2個機器周期,2個機器周期就是2×12=24個振蕩周期,對復位信號連續采樣10次,若是一直為高電平,就產生片內復位使能信號。其他片內寄存器以這個復位信號做同步復位,對WR,RD,ALE都做了采樣,避免毛刺干擾。

1.3 AD0809與CPLD/FPGA狀態機接口設計

1.3.1 AD0809狀態機功能設計

狀態機的最簡結構一般由兩個進程構成,即主控時序進程和主控組合進程。一個進程描述時序邏輯輸出,另一個進程描述組合邏輯包括進程間狀態值的傳遞邏輯以及狀態轉換值的輸出。將AD0809與CPLD/FPGA的接口設計系統劃分為兩部分,即數據單元和控制單元。數據單元包括保存運算數據和運算結果的數據寄存器,也包括完成數據運算的組合邏輯電路。控制單元用來產生信號序列,以決定何時進行何種數據運算,控制單元要從數據單元得到條件信號,以決定繼續進行那些數據運算。數據單元要產生輸出信號、數據運算狀態等有用信號。數據單元和控制單元中,有兩個非常重要的信號,即復位信號和時鐘信號。復位信號保證了系統初始狀態的確定性,時鐘信號則是時序系統工作的必要條件。狀態機通常在復位信號到來的時候恢復到初始狀態,每個時鐘到來的時候內部狀態發生變化。從AD0809的初始狀態開始,也就是狀態機復位以后開始的狀態。在建立每個狀態時都寫出關于這個狀態的文字功能描述,AD0809狀態機功能描述與相應引腳的取值如下:

S0態:初始狀態,選擇通道1的模擬信號輸入,ADDC=‘1’,ALE=START=OE=LOCK=‘0’;

S1態:通道鎖存狀態。ALE=‘1’,START=OE=LOCK=‘0’:

S2態:啟動A/D轉換狀態。ALE=‘1’,START=‘1’,OE=LOCK=‘0’;

S3態:A/D轉換等待狀態,ALE=START=‘0’,OE=LOCK=‘0’;

IF EOC=‘0’保持當前狀態不變,繼續等待A/D轉換,ELSE轉換結束,進入下一狀態;

S4態:數據輸出允許狀態,A/D轉換完畢,開啟數據輸出允許信號,ALE=‘0’,START’0’,OE=‘1’,LOCK=‘0’;

S5態:數據鎖存狀態,開啟數據鎖存信號,將轉換結果送鎖存器鎖存,ALE=‘0’,START=‘0’,OE=‘1’,LOCK=‘0’;

S6態:延時狀態,為了保證數據可靠鎖存,延時一個時鐘狀態周期;ALE=‘0’,START=‘0’,OE=‘1’,LOCK=‘1’;

其他狀態:返回到初始狀態,ALE=START=OE=LOCK=‘0’。

1.3.2 ADC0809狀態機程序設計

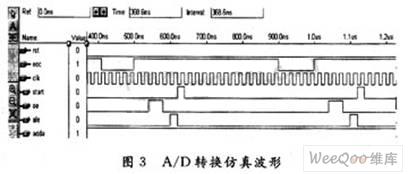

ADC0809為單極性輸入,8位轉換精度逐次逼進式A/D轉換器。其采樣速度為每次轉換約100μs。在轉換開始前由地址鎖存允許信號ALE將3位地址鎖入鎖存器中以確定轉換信號通道。EOC為轉換結束狀態信號,由低電平轉為高電平時指示轉換結束,此時可讀入轉換好的8位數據。EOC在低電平時指示正在進行轉換。START為轉換啟動信號,上升沿啟動。OE為數據輸出允許高電平有效。CLK為ADC轉換時鐘輸入端口500 kHz左右。為了達到A/D器件的最高轉換速度,A/D轉換控制器必須包含監測EOC信號的邏輯,一旦EOC從低電平變為高電平即可將OE置為高電平,然后傳送或顯示已轉換好的數據[D0..D7]。狀態機由三個進程組成ADC,AD_STATE和DATA_LOCK。ADC是此狀態機的主控組合邏輯進程,確定狀態的轉換方式和反饋控制信號的輸出工作過程中首先監測系統復位信號RST,當其為高電平時使此進程復位至初始態ST0。啟動A/D轉換信號START在狀態ST3搜索轉換狀態信號EOC由0變1時即在狀態ST4開啟輸出。使能信號OE在下一狀態使LOCK產生一個上跳沿從而在此時啟動進程DATA_LOCK將由0809轉換好的8位數據鎖進鎖存器ADC_DATA。根據時序電路圖通過狀態機設計程序完成與CPLD/FPGA芯片的連接。圖3為狀態機程序仿真結果。

1.4 BCD碼轉換與顯示電路設計

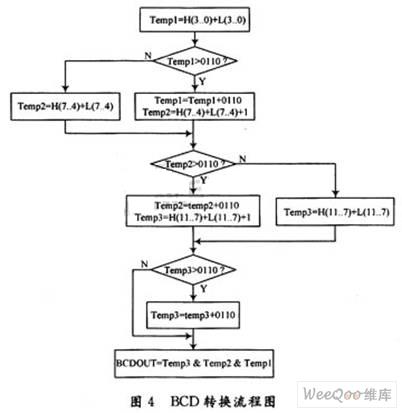

當ADC0809的基準電壓(Vref)為5.12 V時,最小電壓準位是5.12/28=0.2 V。分析模擬輸入電壓與輸出電壓的對應關系可知,當ADC0809的D[7..0]收到的數據信號為10000110(即86H)時,則高4位1000為2.56 V,而低4位0110為0.12 V,所以最后的電壓輸出結果是2.68 V。為了方便后續的電壓數據顯示,在此將輸出電壓表示成12位的BCD碼形式。將高4位數據D(7..4)轉換為對應的高12位BCD碼H(11..0);將低4位數據D(3..0)轉換為對應的低12位BCD碼L(11..0)。在程序中首先用VHDL語言描述一個新的進程Process(regl),然后采用case…when…語句,生成并行結構的電路。

將生成的高12位BCD碼與低12位的BCD碼相加,得到12位的BCD碼,該結果即為所求的BCD碼結果。如上述的256 V的BCD碼是0010 0101 0110,0.12 V的BCD碼是0000 0001 0010,所以相加的結果是0010 0110 1000,即為2.68 V。因此在電路中必須設計一個12位的BCD碼加法程序,實現由8位二進制轉換為12位BCD碼硬件電路。在程序設計中應當注意的是BCD碼相加時,由最低4位加起,且每4位相加的結果超過1001時,應加0110調整。該段程序的描述是通過一個進程Process(HB,LB,CEN)來實現。其中HB表示生成的高12位BCD碼,LB表示生成的低12位BCD碼,CEN表示系統提供的時鐘信號。在時鐘上升沿時刻進行BCD碼相加,并判斷結果是否超過1001,判斷程序采用if…then…語句,實現條件判斷電路。按照圖4完成BCD碼程序轉換設計。將以上兩段程序進行組合,最終獲得由VHDL語言描述的BCD碼轉換程序。

1.5 A/D轉換與BCD碼合成系統電路

將A/D轉換電路與BCD碼轉換電路組成統一系統,通過硬件編程語言VHDL中的進程語句將編制成功的A/D轉換電路描述語句和BCD碼轉換電路描述語句組合成一個整體程序,通過QuartusⅡ軟件生成系統圖,如圖5所示。

A/D轉換結果由3位十進制數表示,每位十進制數由4位BCD碼表示,總共有12位BCD碼輸出。將電路輸出BCDOUT(11..0)分成BCDOUT(11..8),BCDOUT(7..4)和BCDOUT(3..0)三部分,通過三個進程Process()分別用VHDL語言編程描述LED顯示驅動。對整個系統進行波形仿真,得到仿真波形如圖6所示,最后在Gw48-CK實訓開發系統完成功能驗證。

2 結 語

將CPLD和微機控制技術相結合,在智能儀表設計和控制系統設計領域提高了系統設計的靈活性,縮短了產品開發周期,同時使系統易于升級和擴展。因為采用了CPLD(復雜可編程邏輯器件),極大提高了系統I/O口利用率,縮小了印刷電路板面積,提高了系統集成度,在多輸入/多輸出的數據采集和控制系統領域有十分廣闊應用前景。

-

芯片

+關注

關注

459文章

52494瀏覽量

440705 -

cpld

+關注

關注

32文章

1257瀏覽量

171493 -

可編程邏輯

+關注

關注

7文章

526瀏覽量

44757

發布評論請先 登錄

如何利用UCOSII中的統計任務 OS_TaskStat()知道了CPU利用率100%把利用率降下來?

如何利用CPLD實現直流固態功率控制器的設計

openEuler 資源利用率提升之道 01:概論

CPU利用率問題求解

提高客車生產鋼材利用率的途徑

活性物質利用率

專家談如何提高服務器利用率

單液滴連續光固化打印極大提高了光固化3D打印的材料利用率

物流倉庫管理系統可提高出入庫效率及提高面積利用率

如何增加半導體產能利用率?

GPU利用率低的本質原因

利用CPLD提高了系統IO口利用率與系統集成度

利用CPLD提高了系統IO口利用率與系統集成度

評論