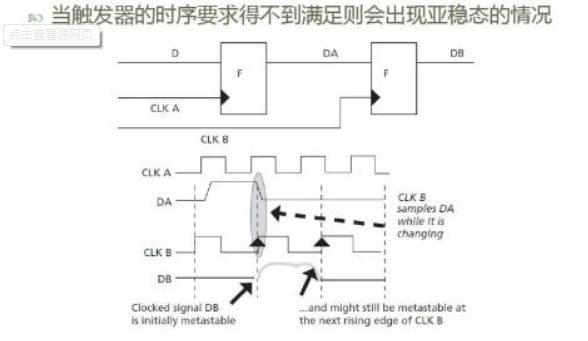

亞穩態是指觸發器無法在某個規定時間段內達到一個可確認的狀態。當一個觸發器進入亞穩態時,既無法預測該單元的輸出電平,也無法預測何時輸出才能穩定在某個正確的電平上。在亞穩態期間,觸發器輸出一些中間級電平,或者可能處于振蕩狀態,并且這種無用的輸出電平可以沿信號通道上的各個觸發器級聯式傳播下去。

解決方法主要有:

(1) 降低系統時鐘;

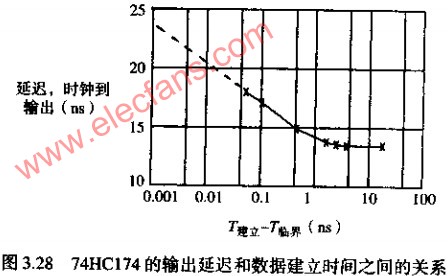

(2) 用反應更快的觸發器(FF),鎖存器(LATCH);

(3) 引入同步機制,防止亞穩態傳播;

(4) 改善時鐘質量,用邊沿變化快速的時鐘信號;

(5) 使用工藝好、時鐘周期裕量大的器件。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

觸發器

+關注

關注

14文章

2032瀏覽量

61891 -

亞穩態

+關注

關注

0文章

47瀏覽量

13478

原文標題:【M博士問答】如何解決亞穩態?

文章出處:【微信號:Mouser-Community,微信公眾號:貿澤電子設計圈】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

xilinx資料:利用IDDR簡化亞穩態

`作者:Primitivo Matas Sanz,技術專家,西班牙馬德里Telefonica I+D 公司,技術專家現身說教,使用觸發器鏈(賽靈思FPGA 中ILOGIC 塊的組成部分)限制設計中

發表于 03-05 14:11

FPGA觸發器的亞穩態認識

的問題。亞穩態的特點: 1. 增加觸發器進入穩定狀態的時間。 亞穩態的壞處之一是會導致觸發器的TCO時間比正常情況要大。多出來的時間tR (resolution time) 就是

發表于 12-04 13:51

FPGA設計的D觸發器與亞穩態

本系列整理數字系統設計的相關知識體系架構,為了方便后續自己查閱與求職準備。對于FPGA和ASIC設計中,D觸發器是最常用的器件,也可以說是時序邏輯的核心,本文根據個人的思考歷程結合相關書籍內容和網上文章,聊一聊D觸發器與亞穩態的

D觸發器與亞穩態的那些事

本系列整理數字系統設計的相關知識體系架構,為了方便后續自己查閱與求職準備。對于FPGA和ASIC設計中,D觸發器是最常用的器件,也可以說是時序邏輯的核心,本文根據個人的思考歷程結合相關書籍內容和網上文章,聊一聊D觸發器與亞穩態的

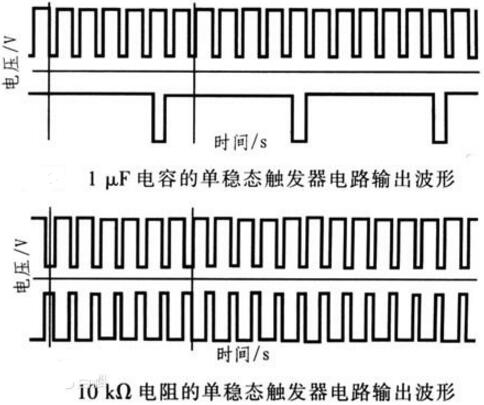

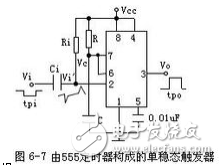

單穩態觸發器的暫穩態時間與什么有關

單穩態觸發器是一種能夠在某個時間間隔內將輸入信號的電平轉換為期望的輸出信號電平的數字電路。在單穩態觸發器中,暫穩態時間是指當

單穩態觸發器暫穩態由什么來維持

單穩態觸發器(Monostable Trigger)是一種數字電路,它在接收到一個觸發信號后,能夠保持輸出狀態一段時間,然后自動返回到初始狀態。單穩態

如何解決觸發器亞穩態問題?

如何解決觸發器亞穩態問題?

評論