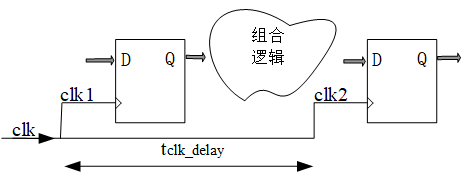

時序邏輯電路示意圖如下。前后兩級寄存器之間有一個組合邏輯運算電路。

假設寄存器的建立時間要求為tsetup, 保持時間要求為thold, 輸出延時為tcq(這些參數只要工藝庫或者器件確定了,就是確定的);組合邏輯電路的運算延時為tlogic; 兩級寄存器之間的clk線路延時為tclk_delay;clk的隨機抖動為tjitter;tcycle為時鐘周期。故電路必須滿足如下建立時間,保持時間要求:

tsetup_slack=tcycle-(tcq+tlogic) -tsetup+tclk_delay-tjitter>0

thold_slack=tcq+tlogic-thold-tclk_delay-tjitter>0

當tsetup_slack要求不滿足時,我們可以選擇增大tcycle。當然這就使得電路的整體時鐘頻率下降,從而速度下降。

從另一個角度考慮,我們可以通過減少tlogic來使得電路的建立時間裕量滿足要求。 達到這個目的,只有兩個辦法:

第一是優化,簡化組合邏輯電路,使得電路的延時下降。如果是ASIC設計,我們可以結合卡諾圖,布爾邏輯等式代換,狄摩根定律等去對邏輯電路盡量做到優化。如果是FPGA設計,我們可以結合FPGA器件的底層單元(例如查找表(LUT))的基本邏輯功能去做邏輯優化。

例如,在做ASIC的時候,要實現如下邏輯功能:

| 輸入 | 輸出 | ||

| A | C | D | B |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

經過卡諾圖化簡得到布爾表達式如下:

B=C’D+A’D+ACD’

還可以進一步化簡

B=C’D+A’D+ACD’=(A’+C’)D+ACD’=(AC)’D+ACD’=(AC)^D

最后發現只要一個與門,后面跟一個異或門就可以實現這個邏輯。

(1)所以我們在寫verilog的時候如果用門級電路去描述這個邏輯電路時:

assign B = (A&D)^D;

或者用結構化的方式去描述時:

and(AC,A,C);

xor(B,AC,D);

其綜合對應出來的電路便可能是最簡單的,當然這跟綜合庫有關。

(2)但是如果我們用行為級的方式去描述這個邏輯時,例如如下。

always @( * )

if( {A,C,D} == 3b001 || {A,C,D} == 3b011 || {A,C,D}==101 ||{A,C,D} == 3b110)

B = 1b1;

else

B = 0;

那么其綜合得到的電路就是不可控的了,雖然EDA工具會對其做優化。因此這樣綜合出來的電路如果不是最簡的,那么其延時就大。

所以在描述電路的時候,如果時序要求很高,最好要考慮邏輯化簡和器件適應。

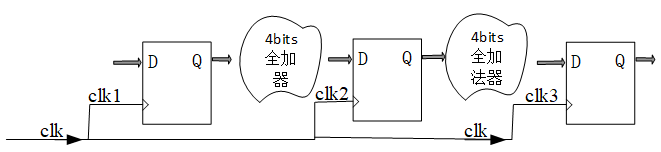

第二種方式便是利用流水線技術,使得兩級寄存器之間組合邏輯電路的運算量減少,從而使得tlogic減少。

例如對于一個組合邏輯電路,其功能是實現8bit數的全加器。我們可以將其劃分成兩個4bit數的全加器。如下圖,原本是要實現兩個8bit數A[7:0],B[7:0],外加一個進位位c_in相加的,如下。

assign{c_out,sum[7:0]} =A[7:0] + B[7:0] +c_in ;

現在變成了前面一個全加器實現

assign {c_out1,sum1[3:0]} = A[3:0] + B[3:0] + c_in ;

后面一個全加器實現

assign{c_out,sum2[3:0]} = A[7:4] + B[7:4] + c_out1 ;

最后再將sum1,sum2合并得到sum,如下。

assign sum = {sum2,sum1};

第一個全加器算出{c_out1,sum1[3:0]} = A[3:0] + B[3:0] + c_in 之后,在時鐘有效沿到來時,將c_out1,sum1[3:0],A[7:4],B[7:4] 送到中間一級寄存器暫存;然后第二個電路做{c_out,sum2[3:0]} = A[7:4] + B[7:4] + c_out1 運算,并將結果sum1,sum2合并得到sum。這樣一來每兩級寄存器之間的全加器變成了4bit的全加器,電路延時肯定得到降低了。從而tlogic降低。

當然還可以進一步優化,使得流水級數更多。一般來說保持時間不會出現違例情況,因為寄存器的輸出延時tcq,一般要大于thold。如果出現違例,從式子

thold_slack=tcq+tlogic-thold-tclk_delay-tjitter>0

我們可以考慮適當增加tlogic,或者后端布局布線時去減少tclk_delay。

-

邏輯電路

+關注

關注

13文章

502瀏覽量

43212 -

寄存器

+關注

關注

31文章

5425瀏覽量

123602 -

時序

+關注

關注

5文章

397瀏覽量

37816

原文標題:時序違例的修正與時序優化的思考方向

文章出處:【微信號:LF-FPGA,微信公眾號:小魚FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

vivado:時序分析與約束優化

基于FPGA時序優化設計

時序約束的步驟分析

如何降低面積和功耗?如何優化電路時序?

時序違例的修正與時序優化的思考方向

時序違例的修正與時序優化的思考方向

評論