設(shè)計(jì)背景:

FPGA的學(xué)習(xí)也算是是一種日積月累才能有成就的過程,前面我們學(xué)習(xí)了各個(gè)模塊,各個(gè)芯片的配置等等,之后筆者通過兩個(gè)簡單的例子來讓大家去系統(tǒng)的學(xué)習(xí)和認(rèn)識FPGA。所學(xué)習(xí)的電子琴設(shè)計(jì)也算是一次簡單的各個(gè)模塊的聯(lián)系調(diào)用的一個(gè)過程,對以后工作中的學(xué)習(xí)有很好的幫助。

設(shè)計(jì)原理:

本次的設(shè)計(jì)主要是通過控制ps2鍵盤來使蜂鳴器發(fā)出哆來咪法嗦拉西7種音來,音符主要又高低音等等,本設(shè)計(jì)只選擇發(fā)出高音的多來咪發(fā)嗦啦西。本設(shè)計(jì)中還用到了VGA的設(shè)計(jì),通過VGA來在顯示屏上畫出如下圖的黑白的電子琴鍵:

當(dāng)按下多來咪發(fā)嗦啦西時(shí),對應(yīng)的鍵值變顏色表示按下,不變色表示不按下,顏色自己可以調(diào)節(jié),但是琴的按鍵必須為黑白色來顯示出來。

當(dāng)按下按鍵的時(shí)候,蜂鳴器來鳴響對應(yīng)時(shí)間的音符,本設(shè)計(jì)蜂鳴器響的時(shí)間為0.25S一個(gè)音符持續(xù)的時(shí)間。

本次設(shè)計(jì)用到的PS2和VGA的設(shè)計(jì)原理筆者在這里就不過多的介紹了,不明白的可以翻看前面發(fā)的文檔內(nèi)容。

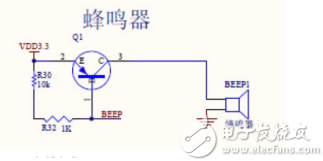

在本設(shè)計(jì)中介紹蜂鳴器的使用和各音符發(fā)聲的頻率大小。本設(shè)計(jì)用的是無源蜂鳴器,原理圖如下:

由于FPGA的驅(qū)動(dòng)能力不夠,我們添加了一個(gè)三極管來驅(qū)動(dòng)這個(gè)無源蜂鳴器,而無源蜂鳴器的主要特點(diǎn)是內(nèi)部不帶振蕩源,所以如果使用直流信號是無法使無源蜂鳴器鳴叫的,必須使用方波去驅(qū)動(dòng)它。

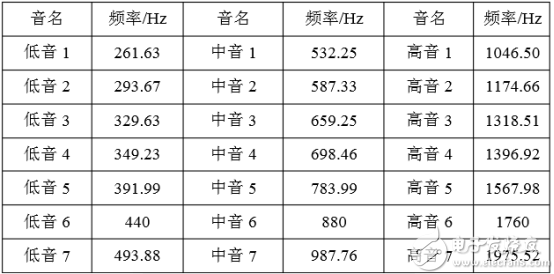

現(xiàn)在我們明白了,只要往蜂鳴器發(fā)送一定頻率的方波,就可以使得蜂鳴器發(fā)出聲音,然后現(xiàn)在的問題是,我們究竟要往蜂鳴器發(fā)送什么頻率的方波信號呢?具體的頻率可以查看下圖:

現(xiàn)在我們知道了如何讓蜂鳴器響起,又知道發(fā)送什么頻率可以讓蜂鳴器響起什么的聲音,所以我相信我們已經(jīng)有能力讓蜂鳴器響起我們需要的音樂了。

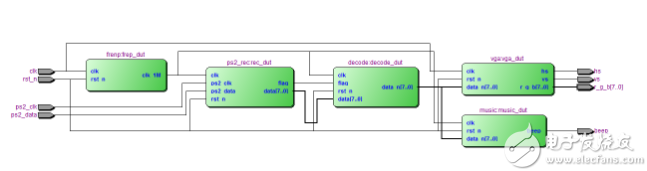

設(shè)計(jì)架構(gòu)圖:

設(shè)計(jì)代碼:

頂層模塊

0modulemusic_ps2(clk,rst_n,hs,vs,r_g_b,ps2_clk,ps2_data,beep);

1

2 inputclk;

3 inputrst_n;

4

5 outpuths;

6 outputvs;

7 output[7:0]r_g_b;

8 outputbeep;

9

10 inputps2_clk;

11 inputps2_data;

12

13 wireflag;

14 wire[7:0]data,data_n;

15 wireclk_1M;

16

17

18 frenp frep_dut(

19 .clk(clk),

20 .rst_n(rst_n),

21 .clk_1M(clk_1M)

22 );

23

24 ps2_rec rec_dut(

25 .clk(clk_1M),

26 .rst_n(rst_n),

27 .ps2_clk(ps2_clk),

28 .ps2_data(ps2_data),

29 .flag(flag),

30 .data(data)

31 );

32

33 decode decode_dut(

34 .clk(clk_1M),

35 .rst_n(rst_n),

36 .flag(flag),

37 .data(data),

38 .data_n(data_n)

39 );

40

41 music music_dut(

42 .clk(clk_1M),

43 .rst_n(rst_n),

44 .data_n(data_n),

45 .beep(beep)

46 );

47

48 vga vga_dut(

49 .clk(clk),

50 .rst_n(rst_n),

51 .hs(hs),

52 .vs(vs),

53 .r_g_b(r_g_b),

54 .data_n(data_n)

55 );

56

57endmodule

蜂鳴器模塊

0modulemusic(clk,rst_n,data_n,beep);端口列表

1

2 inputclk;

3 inputrst_n;

4 input[7:0]data_n;//輸入的鍵值

5 outputregbeep;//蜂鳴器

6

7 reg[10:0]music_data;

8 wire[10:0]data;

9

10 always@(posedgeclk)

11 if(!rst_n)

12 begin

13 music_data <=0;

14 end

15 else

16 case(data_n)

17 1 : music_data <=478;//蜂鳴器的高音1

18 2 : music_data <=425; //蜂鳴器的高音2

19 3 : music_data <=379; //蜂鳴器的高音3

20 4 : music_data <=358;//蜂鳴器的高音4

21

22 5 : music_data <=319; //蜂鳴器的高音5

23 6 : music_data <=284; //蜂鳴器的高音6

24 7 : music_data <=253; //蜂鳴器的高音7

25 default:music_data <=0;

26 endcase

27

28

29 reg[20:0]count,cnt;

30

31 always@(posedgeclk)

32 if(!rst_n &&!data_n)

33 begin

34 count <=0;

35 end

36 else

37 if(count <250_000-1)

38 begin

39 count <=count +1;

40 end

41 else

42 begin

43 count <=0;

44 end

45

46 //計(jì)數(shù)0.25S的時(shí)間

47 assigndata =(count ==250_000-1)?music_data :data;

48

49 always@(posedgeclk)

50 if(!rst_n)

51 begin

52 cnt <=1;

53 beep <=0;

54 end

55 else

56 if(data ==0)//控制蜂鳴器不響

57 begin

58 cnt <=1;

59 beep <=0;

60 end

61 elseif(cnt <data)//計(jì)數(shù)對應(yīng)的頻率

62 begin

63 cnt <=cnt +1;

64 end

65 else

66 begin

67 cnt <=1;//蜂鳴器響

68 beep <=~beep;

69 end

70

71

72

73endmodule

代碼驗(yàn)證正確無誤,筆者在這邊就不過多的驗(yàn)證,大家可以自主的補(bǔ)全代碼,后續(xù)代碼會在論壇中發(fā)出來供大家參考個(gè)學(xué)習(xí)。

-

FPGA

+關(guān)注

關(guān)注

1645文章

22050瀏覽量

618718

發(fā)布評論請先 登錄

FPGA在機(jī)器學(xué)習(xí)中的具體應(yīng)用

DS28E38 adi

flash MP3語音IC芯片廠介紹兒童電子琴智能語音方案

基于FPGA的電子琴設(shè)計(jì)

DAC38J84 SYSREF的時(shí)鐘頻率如何確定?

DAC38J84使用JESD與FPGA對連,CGS階段過不去怎么解決?

dac38j82 IOUTx為什么沒有波形輸出?

ED6H系列FPGA口袋實(shí)驗(yàn)室

FPGA加速深度學(xué)習(xí)模型的案例

UCC38C42系列高速BiCMOS電流模式PWM控制器

九芯電子電子琴語音芯片的無限可能——N930X-S16 MP3解碼芯片

FPGA學(xué)習(xí)系列:38. 電子琴的設(shè)計(jì)

FPGA學(xué)習(xí)系列:38. 電子琴的設(shè)計(jì)

評論