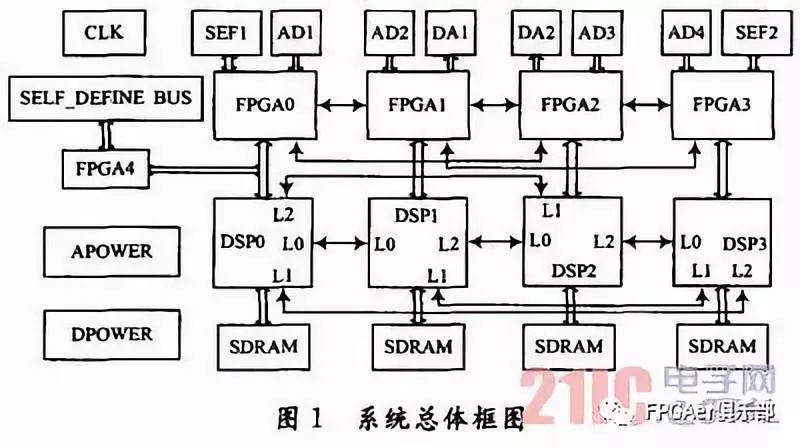

實驗與實際應用表明,該系統具有很強的數據處理能力和很好的穩定性。關鍵詞:高速中頻;信號處理;FPGA;DSP0 引言 現代社會正向數字化、信息化方向高速發展,在這一過程中,往往需要高速信號的實時性數字化處理。例如,隨著科技的進步,現代雷達等應用信號的數字化處理上有了長足的發展,但也帶來了新的問題,這些應用的數字信號處理具有海量運行需求的應用背景,如巡航導彈末制導雷達地形匹配、合成孔徑雷達的成像處理、相控陣雷達的時空二維濾波處理等領域。目前,單片DSP難以勝任許多信號處理系統的要求。而常見的解決方案也是高速A/D采樣與信號處理功能是在多塊不同的板卡上實現,這給實際應用帶來很多不便。 鑒于上述現有技術所存在的問題,本設計平臺的目的是:(1)實現高速中頻信號(如雷達信號)的數字化處理并進行實時傳輸數據或進行數據的實時計算,并能通過輸出電路進行結果顯示;(2)自定義控制總線可以實現對高速中頻信號處理板進行靈活控制,具有較強的可配置性和豐富的靈活性;(3)高速A/D采樣與D/A回放及數據處理單元集成在一塊板上,在集成度高的同時也降低了高速信號在傳輸過程中出現差錯的概率。1 平臺設計方案 高速中頻采樣信號處理平臺由主控制電路、高速A/D與D/A電路、信號處理單元電路、光纖通道電路、時鐘管理電路、存儲單元和外部接口電路組成,其總體框圖如圖1所示。

在實際應用過程中,四路A/D通道可以接收不同的信號源的信號,D/A通路可以對外進行數據顯示等多種功能,時鐘管理電路管理內外時鐘的使用及對板上系統供給工作時鐘,兩路光纖通道可以與其他高速設備相連接,自定義總線可以與CPU或主控制器相連接對平臺進行有效靈活的控制。

1.1 高速A/D與D/A設計 四路高速A/D采樣通道采用兩片NS公司的ADC081000實現,每片有兩個A/D通道,相比多片A/D器件的通道間相位恒定設計是一個難點而言,單片A/D器件可以更容易實現兩路通道間的相位恒定。ADC081000是一款高性能的A/D采集芯片,單通道8 b采樣頻率為1 GHz。本平臺中A/D通道間采樣數據的相位恒定是利用采樣時鐘相位間的恒定來實現的。在設計時,使時鐘芯片到兩片A/D器件間的時鐘線等長,兩片A /D器件到FPGA間的時鐘線與數據線也分別等長,并且還利用一片FPGA設計了對兩片A/D器件的軟啟動控制,這就更保證了四路通道間采樣時鐘的相位恒定。 兩路高速D/A通道采用兩片AD公司的AD9736實現,AD9736單通道14 b,采樣頻率可達1 200 MSPS。兩路高速D/A通路也利用一片FPGA作控制,實現通道間相位差的恒定。

1.2 信號處理單元設計 信號處理單元包括FPGA和DSP兩大部分。FPGA部分主要由四片Virtex-4 SX55組成,四片FPGA間實現有串行連接和相隔間的連接。FPGA電路主要是實現對高速A/D采集數據的預處理和高速D/A回放數據處理,并且控制高速A/D電路采樣時鐘的相位恒定與高速D/A電路采樣時鐘的相位恒定,同時也根據需要與相應的DSP進行數據交換或傳遞。FPGA電路上連接的光接口電路也可以實現與其他系統進行高速、實時的數據交換。A/D采樣之后的數字信號速率非常高,要從這些高速信號中得到有用的基帶信號,需要有效地對其進行數字下變頻、抽取、濾波等處理,這些功能都可以通過FPGA來實現。FPGA具有較高的處理速度和較高的穩定性,同時又具有設計靈活、易于修改和維護的優點,可以適應不同系統的要求,提高了系統的適用性及可擴展性。DSP電路是本平臺信號處理的核心,完成大部分的數據處理工作,由四片ADSP TS201組成,四片DSP間實現了兩兩間的Link口互連,構成了分布式并行系統,可以把復雜的算法分割成小的任務給各處理器完成,從而減少任務的執行時間。 根據設計需要,平臺數據的傳輸量很大,多DSP之間的數據傳輸速度尤為重要,采用Link口來傳輸數據,可以在不增加輔助電路的前提下,DSP間的直接互聯。而且,基于Link口的數據傳輸采用專門的數據通道,不占有系統總線資源,消除了傳輸過程中的總線仲裁,減少了網絡延遲帶來的不確定因素。四片DSP間Link口的傳遞數據能力高達600 MB/s。DSP主要是通過軟件設計來實現數字基帶信號處理以及比特流控制、編碼解碼等高速的數據交換和處理功能。對DSP開發的軟件工具是ADI公司的VisualDSF++4.0,它是TigerSHARC系列DSP的集成開發環境,支持匯編語言、C語言、C++等開發語言,能讓程序員使用這些工具編寫出相對于特定DSP的高性能應用程序,發揮強大的處理能力。在本平臺中,每片DSP的地位都是對等的,能夠根據不同的要求,硬件結構不用改變,只須在DSP的軟件算法中稍加改動,系統就能實現新的功能。

1.3 主控制電路設計 主控制電路與信號處理單元電路和外部接口電路相連,其核心是一片規模較小的FPGA。它主要是控制信號處理單元的同步復位及工作控制,可以將從外部主機接收到信號傳遞給信號處理單元,也可將信號處理單元的有關信息傳遞到外部主機中。

1.4 其他主要電路設計 時鐘管理電路主要是負責板上FPGA、DSP、光口、高速A/D與D/A等正常工作所需要時鐘生成與配置。外部存儲電路是FPGA與DSP正常工作時所需要的外部RAM空間大小的設計。外部接口電路是本平臺與其他設備進行連接的控制接口。光纖通道電路由兩路光纖通道組成,每路可以工作在2.5 Gb/s,可以與其他系統進行數據交換。2 性能測試 決定平臺性能的指標有多個,選取最主要的三個進行測試,結果如下。

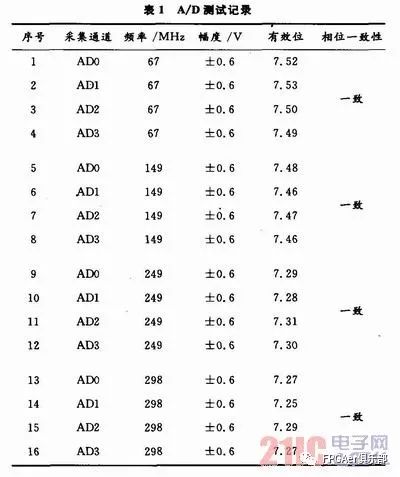

2.1 A/D采樣的有效位數 有效位數是用來表述A/D器件的一項總體指標,對精確評價系統性能非常重要。對于A/D采樣有效位的測試,采用A/D器件的最大量程輸入,在FPGA中取得數據,用Matlab來對數據處理進行計算得到的。四路A/D采樣通道有效位的測試數據如表1所示。

2.2 A/D通道間相位恒定A/D通道間的相位恒定指標直接測試比較困難,在平臺設計中已經保證了同一芯片兩路A/D通道間的相位差是恒定的,只要測試兩片A /D芯片輸出時鐘相位差是否恒定即可判定。表1中也顯示了兩片A/D器件輸出時鐘的相位差測試結果。2.3 DSP運算速度DSP的運算速度和精度決定著系統的數據處理能力,同時也會對整個系統的性能和結構產生重要的影響。DSP的處理能力可以用1 024點的復數FFT計算時間進行比較。Link口傳遞速度的測試,可以將Link口的工作時鐘設定在600 MHz,按4 b進行數據傳遞,如果接收到數據沒有錯誤,即可認定Link口的工作速率可以達到600 MB/s。經過測試,在工作頻率為600 MHz,按4 b進行數據傳遞的情況下,各個Link均通過測試,也就是說每個Link口工作速率都可以達到600 MB/s。經過測試,平臺上兩個光口的傳輸速度均達到了2.5 Gb/s。DSP運算速度測試結果見表2。

3 結語 通過上述測試結果可以看出,本平臺設計合理,FPGA與DSP的結合使用,能充分發揮各自的優勢,實現對高速、多路、海量信號的實時處理。另外,高度集成化設計,大大減少了平臺所占用的空間體積,也使功耗大大減小。平臺在兵器某所項目驗證中,接入實際雷達信號進行測試,各項指標均達到了設計要求。

-

dsp

+關注

關注

556文章

8158瀏覽量

357834 -

FPGA

+關注

關注

1646文章

22054瀏覽量

618820

原文標題:基于FPGA+DSP的高速中頻采樣信號處理平臺的實現

文章出處:【微信號:FPGAer_Club,微信公眾號:FPGAer俱樂部】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

中科億海微SoM模組——FPGA+DSP核心板

普源DHO4804示波器實時采樣率在高速信號測試中的應用

進群免費領FPGA學習資料!數字信號處理、傅里葉變換與FPGA開發等

用ADS7864和DSP5402進行信號采集與處理,請問哪里可以查看關于ADS7864的AD采樣程序源代碼?

求助,關于高速ADC采樣的幾個問題求解

FPGA 實時信號處理應用 FPGA在圖像處理中的優勢

FPGA 與微控制器優缺點比較

基于DSP TMS320C6678+FPGA XC7V690T的6U VPX信號處理卡

基于FPGA+DSP的高速中頻采樣信號處理平臺

基于FPGA+DSP的高速中頻采樣信號處理平臺

評論