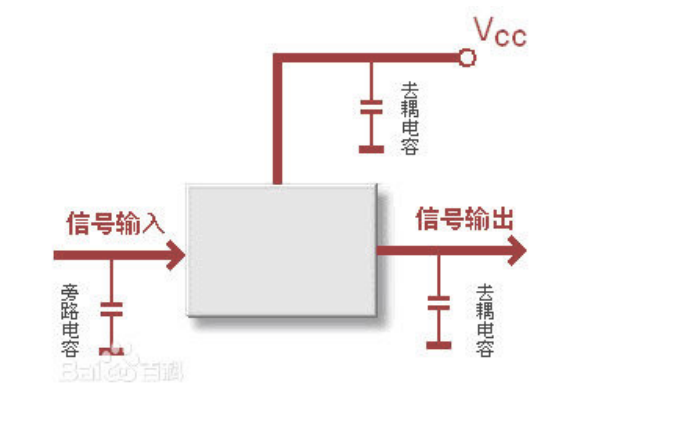

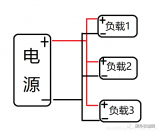

對于噪聲敏感的IC電路,為了達到更好的濾波效果,通常會選擇使用多個不同容值的電容并聯方式,以實現更寬的濾波頻率,如在IC電源輸入端用1μF、100nF和10nF并聯可以實現更好的濾波效果。那現在問題來了,這幾個不同規格的電容在PCB布局時該怎么擺,電源路徑是先經大電容然后到小電容再進入IC,還是先經過小電容再經過大電容然后輸入IC。

電子電器

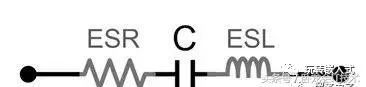

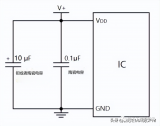

我們知道,在實際應用中,電容不僅僅是理想的電容C,還具有等效串聯電阻ESR及等效串聯電感ESL,如下圖所示為實際的電容器的簡化模型:

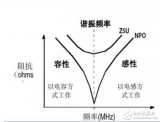

在高速電路中使用電容需要關注一個重要的特性指標為電容器的自諧振頻率,電容自諧振頻率公式表示為:

自諧振頻率點是區分電容器是容性還是感性的分界點,低于諧振頻率時電容表現為電容特性,高于諧振頻率是電容表現為電感特性,只有在自諧振頻率點附近電容阻抗較低,因此,實際去耦電容都有一定的工作頻率范圍,只有在其自諧振頻率點附近頻段內,電容才具有很好的去耦作用,使用電容器進行電源去耦時需要特別注意這一點。

電容的特性阻抗可表示為:

可見大電容(1uF)的自諧振點低于小電容(10nF),相應的,大電容對安裝的PCB電路板上產生的寄生等效串聯電感ESL的敏感度小于小電容。

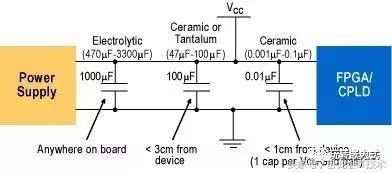

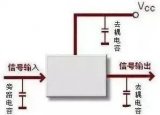

SO,小電容應該盡量靠近IC的電源引腳擺放,大電容的擺放位置相對寬松一些,但都應該盡量靠近IC擺放,不能離IC距離太遠,超過其去耦半徑,便會失去去耦作用。

以上情況適用于未使用電源平面的情況,對于高速電路電路,一般內層會有完整的電源及地平面,這時去耦電容及IC的電源地引腳直接過孔via打到電源、地平面即可,不需用導線連接起來。

-

pcb

+關注

關注

4368文章

23492瀏覽量

409871 -

電容

+關注

關注

100文章

6254瀏覽量

154292

原文標題:有多個電容,那么這些電容怎么布局才能更好的起到去耦作用?

文章出處:【微信號:mcuworld,微信公眾號:嵌入式資訊精選】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

去耦電容和旁路電容都是起到抗干擾的作用

去耦電容的容值計算和布局布線

去耦電容有什么作用

如何布局電容才能起到去耦作用

如何布局電容才能起到去耦作用

評論