前言

vivado自帶很多命令幫助編譯器更好的實(shí)現(xiàn)設(shè)計(jì)者的想法,用得好會(huì)變成開發(fā)利器。比如,max_fanout命令,本身是用來約束扇出,減少布線擁塞的常用命令。然而很多讀者向我反映,使用這個(gè)命令之后發(fā)現(xiàn)沒有任何事情發(fā)生,完全沒有任何效果。這里我就帶大家理一理這個(gè)命令的使用方法。

max_fanout 起作用的條件

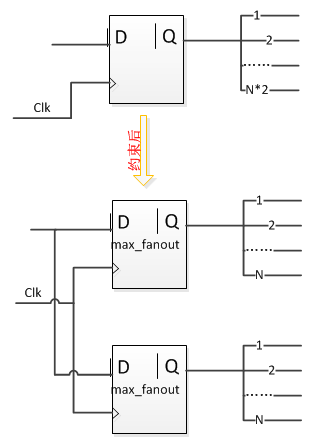

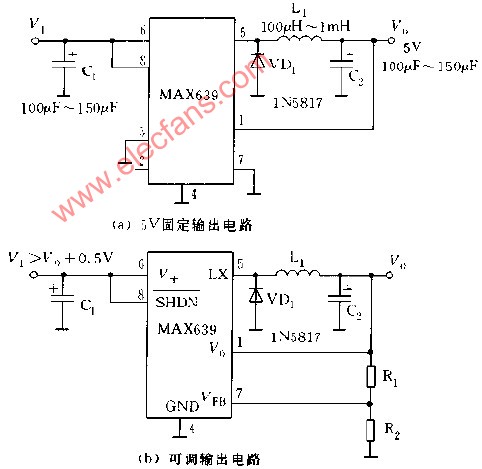

打算降低扇出的網(wǎng)絡(luò)必須是reg驅(qū)動(dòng)。因?yàn)榻档蜕瘸龅脑砭褪莚eg驅(qū)動(dòng)超過N(設(shè)置參數(shù))條網(wǎng)絡(luò)的時(shí)候,就復(fù)制一個(gè)同樣的reg驅(qū)動(dòng)其他N條網(wǎng)絡(luò),如果復(fù)制2個(gè)還不夠就一直復(fù)制到足夠?yàn)橹梗妶D1。

-flatten_hierarchy不能設(shè)置為none。圖形界面設(shè)置位置見圖2。

如果需要優(yōu)化的信號(hào)在IP核內(nèi)部那么在布局完成后使用下面的命令phys_opt_design -force_replication_on_nets [get_nets net_name]來保證IP核取消對(duì)內(nèi)部網(wǎng)絡(luò)的保護(hù),能夠正常復(fù)制高扇出網(wǎng)絡(luò)。

圖1.寄存器復(fù)制示意圖

圖2.flatten_hierarchy設(shè)置位置

max_fanout 的使用形式

1. verilog綜合屬性設(shè)置:(*MAX_FANOUT = 50 *) reg test;

這里的綜合屬性必須設(shè)置在要降低扇出的寄存器前面,否則一定不會(huì)按照設(shè)計(jì)者意圖綜合。這種方法缺點(diǎn)是不能作用于IP核內(nèi)部的某個(gè)信號(hào)。

2.set_property MAX_FANOUT 50 [get_nets {test}]或者

set_property MAX_FANOUT 50 [get_cells {test_r}]

注意get_cells選中的必須是要求編譯器復(fù)制它來降低扇出的寄存器,因?yàn)関erilog代碼里面和最終實(shí)現(xiàn)的電路里面的寄存器名字很可能不一樣,所以建議綜合完成后在原理圖里面去找到對(duì)應(yīng)寄存器,然后復(fù)制他的名字,這樣就不會(huì)弄錯(cuò)。很多時(shí)候讀者使用命令的時(shí)候cells的名字就弄錯(cuò)了!用get_nets命令也一樣最好去原理圖里面找對(duì)應(yīng)的網(wǎng)絡(luò),復(fù)制名字。xdc約束可以作用于IP核內(nèi)部的某個(gè)信號(hào)。

max_fanout 的參數(shù)意義

(*MAX_FANOUT = 50 *) reg test;里面的參數(shù)就只有一個(gè)——50,網(wǎng)絡(luò)扇出超過50就會(huì)復(fù)制一個(gè),保證每個(gè)復(fù)制的寄存器下面的扇出都不超過此參數(shù)。xdc約束也一樣,不再敖述。

注意,圖1的綜合設(shè)置里面有-fanout_limit這個(gè)參數(shù),并且默認(rèn)是10000。這里是約束全局扇出的,但是max_fanout命令的優(yōu)先級(jí)會(huì)高于這里的設(shè)置參數(shù)。所以編譯器會(huì)優(yōu)先按照你的綜合屬性或者XDC約束來進(jìn)行優(yōu)化。

-

寄存器

+關(guān)注

關(guān)注

31文章

5433瀏覽量

124331 -

編譯器

+關(guān)注

關(guān)注

1文章

1661瀏覽量

50183

原文標(biāo)題:max_fanout命令的正確打開方式

文章出處:【微信號(hào):HaveFunFPGA,微信公眾號(hào):玩兒轉(zhuǎn)FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

PADS BGA Fanout扇出教程

濾波電容FANOUT時(shí)怎么操作?

verilog寫好之后,sdc約束文件到底該怎么確定?

Matlab使用方法和程序設(shè)計(jì)

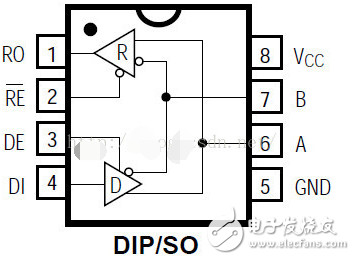

MAX3485芯片使用方法

示波器的使用方法(三):示波器的使用方法詳解

時(shí)序設(shè)計(jì)基本概念之fanout

max_fanout的使用方法和技巧

max_fanout的使用方法和技巧

評(píng)論