醫(yī)療和工業(yè)應(yīng)用繼續(xù)收集更多數(shù)據(jù),隨著設(shè)備和系統(tǒng)從可穿戴ECG監(jiān)護儀到工廠自動化中的預(yù)測性維護應(yīng)用程序的連接越來越多,這種需求將繼續(xù)增長。然而,數(shù)據(jù)僅與其精度一樣有價值,為此,逐次逼近寄存器,模數(shù)轉(zhuǎn)換器(SAR-ADC)為給定的模擬輸入信號提供成功且準確的數(shù)字結(jié)果。當與適當?shù)?a target="_blank">驅(qū)動器運算放大器(運算放大器)結(jié)合使用時尤其如此。

對于醫(yī)療和工業(yè)監(jiān)控,準確度和精度至關(guān)重要。 SAR-ADC產(chǎn)生指定的位數(shù)。但是,如果輸入信號由于噪聲或振蕩而不穩(wěn)定,則轉(zhuǎn)換器只能可靠地產(chǎn)生輸入信號的不穩(wěn)定性。面臨的挑戰(zhàn)是確保模擬系統(tǒng)噪聲和運算放大器帶寬與SAR-ADC相輔相成。

本文簡要討論了支持抗混疊濾波器的設(shè)計和互補運算放大器的正確選擇。最后總結(jié)了兩個最終設(shè)計。第一設(shè)計將使用ADI公司的AD4003BRMZ,18位,2 MSPS,SAR-ADC和ADI公司的ADA4940-1ACPZ-R7全差分運算放大器。

設(shè)計二將使用德州儀器'ADS8860IDRCT,16位,1 MSPS,SAR-ADC和德州儀器的THS4531ID,全差分運算放大器。請注意,仿真和臺架驗證是此設(shè)計過程的最后一步。

理解SAR-ADC/放大器接口背后動力學(xué)的關(guān)鍵是將設(shè)計分解為可管理的塊。

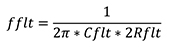

SAR-ADC輸入結(jié)構(gòu)

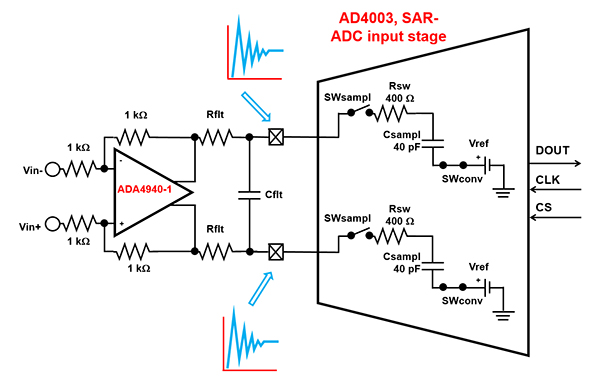

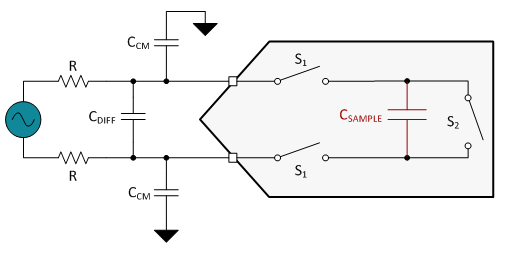

SAR-ADC輸入結(jié)構(gòu)的基本模型主要由兩個開關(guān)(SWsampl,SWconv),輸入開關(guān)電阻(Rswitch)和采樣電容Csampl組成(圖1)。

圖1:良好工作的SAR-ADC輸入模型有助于確定合適的放大器驅(qū)動器和抗混疊濾波器。 (圖像來源:Digi-Key Electronics)

在信號采集之前,采樣開關(guān)SWsampl打開,轉(zhuǎn)換開關(guān)SWconv打開。 SWsampl的閉合啟動信號采集狀態(tài),在Csampl上建立電壓和電荷水平。在采集或采樣周期(tAQU)結(jié)束時,SWsampl打開。通過此操作,信號與SAR-ADC的輸入引腳隔離,器件繼續(xù)比較每個N位,分別確定正確的1或0值。

在此采集期間,有一個初始值SAR-ADC輸入端的高頻電壓/電流尖峰最終會穩(wěn)定,以反映放大器的輸出電壓。如果電路中不存在Rflt和Cflt元件,則運算放大器必須能夠在采集周期結(jié)束時將Csampl充電至低于最低有效位(LSB)的1/2。這需要一個非常高速的放大器,可以保持Csampl容性負載的穩(wěn)定性。這種高速放大器還會給系統(tǒng)帶來更多噪聲并增加系統(tǒng)功耗。

另一種系統(tǒng)是重新插入Rflt和Cflt,允許使用低頻放大器。此外,附帶的R/C對用作抗混疊濾波器。

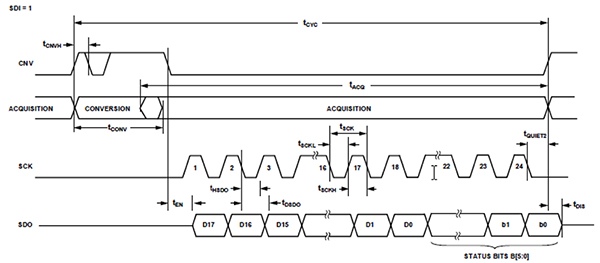

模擬器件AD4003的采集或采樣時間tAQU和吞吐率(tCVC),2 MHz采樣,18位SAR-ADC分別為290納秒(ns)和500 ns(圖2)。

圖2:AD4003 3線無忙指示器串行接口時序圖,包括狀態(tài)位(SDI高)。當先前的轉(zhuǎn)換結(jié)果出現(xiàn)在SDO輸出引腳上時,會發(fā)生信號采集tAQU。 (圖像來源:ADI公司)

正確的驅(qū)動放大器選擇非常重要。作為起點,放大器必須是單位增益穩(wěn)定的。除此之外,產(chǎn)品選擇期間關(guān)注的主要參數(shù)是放大器的壓擺率。

輸入信號伏特每微秒最小壓擺率(SRmin)等于p * fin * Vout-pp * 10 -6 。例如,如果頻率和輸出峰峰值電壓(Vout-pp)分別為500kHz和2伏,則信號轉(zhuǎn)換速率為1.256伏/微秒(V/μsec)。一個好的經(jīng)驗法則是選擇轉(zhuǎn)換速率大于或等于2 * SRmin的運算放大器。 ADA4940-1的指定壓擺率為90 V/μsec。

確定Cflt的值

Cflt的作用有三個:吸收開始時的高頻瞬變采集時間,為SAR-ADC的輸入提供充足的電荷,并在采集時間結(jié)束時穩(wěn)定SAR-ADC輸入電壓。當Cflt的值至少比SAR-ADC采樣電容Csampl的值高10倍時,這是可能的。這確保了95%的所需電荷可用于采樣電容。

對于ADI公司的AD4003,Cflt必須等于或大于400皮法(pF)(再次參見圖1)。在本文的第一個設(shè)計中,使用AD4003,Cflt的值為500 pF。 Cflt工藝材料應(yīng)具有高Q值,低溫度系數(shù)和不同電壓,頻率和時間下穩(wěn)定的電氣特性的C0G或NPO。

Rflt電阻有兩個功能。第一個功能是將放大器的輸出與高容性負載隔離。第二個功能是創(chuàng)建一階抗鋸齒濾波器。

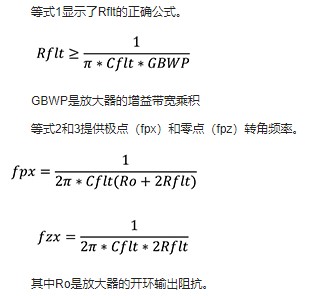

確定Rflt的值作為隔離代理和抗混疊濾波器

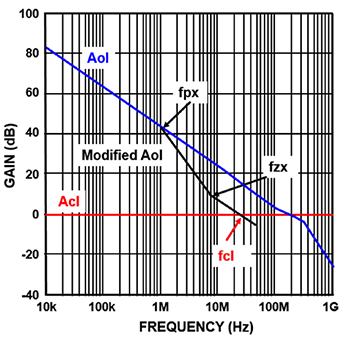

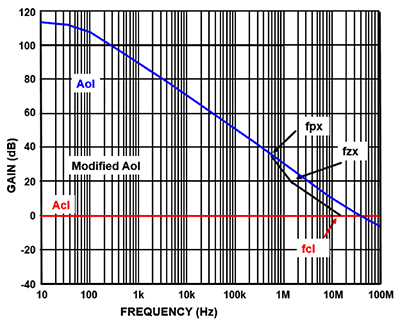

其中一個目標是驅(qū)動器和運算放大器的組合是通過將負載電容與驅(qū)動器放大器的輸出隔離來創(chuàng)建穩(wěn)定的放大器。放大器負載電容和放大器輸出之間的電阻器完成了這項任務(wù)。選擇合適的電阻器的一個限制是確保放大器電路穩(wěn)定。 Rflt/Cflt對為放大器的開環(huán)傳遞函數(shù)增加了一個額外的極點和零點(圖2)。

圖3:ADA4940-1的開環(huán)增益與頻率曲線。 Rflt和Cflt改變放大器的開環(huán)增益曲線。為了穩(wěn)定,開環(huán)增益(Aol)和閉環(huán)增益(Acl)曲線的閉合速率必須為20 dB/decade。 (圖像來源:Digi-Key Electronics)

放大器穩(wěn)定性發(fā)生在開環(huán)增益和閉環(huán)增益曲線相交的地方。如果這兩條曲線的閉合速率為20 dB/decade,則電路將保持穩(wěn)定(再次參見圖2)。如果這兩條曲線的閉合速率為40 dB/decade,則電路將不穩(wěn)定。

使用ADA4940-1和AD4003的第一個設(shè)計的Rflt和Cflt值等于15 W和500 pF。此時的問題是:這個一階抗混疊濾波器的截止頻率是多少?

這個一階抗混疊濾波器的響應(yīng)取決于Rflt的值和CFLT。此濾波器轉(zhuǎn)角頻率的變量為fflt(公式4)。

Rflt和Cflt以20的速率衰減模擬路徑中的噪聲dB/decade高于7.6 MHz。請注意,fflt等于fzx。

放大器帶寬的定義包含在使用GBWP規(guī)范的等式1中。但是,放大器選擇過程還有很多。放大器建立時間和噪聲等特性值列在關(guān)鍵列表中。

放大器選擇

放大器的建立時間與Rflt/Cflt網(wǎng)絡(luò)的建立時間相結(jié)合制作復(fù)合系統(tǒng)的穩(wěn)定時間。

驅(qū)動器運算放大器Rflt和Cflt組合的目標之一是創(chuàng)建一個環(huán)境,使信號穩(wěn)定在小于或等于SAR-ADC的0.5 LSB的電壓。隨著SAR-ADC分辨率的提高,建立容差變得越來越小(表1)。

SAR-ADC位數(shù)0.5 LSB限制時間限制10 0.0488281%8 12 0.0122070%9 14 0.0030518%11 16 0.0007629%12 18 0.0001907%13 20 0.0000477%15 22 0.0000119%17 24 0.0000030%18

表1:隨著SAR-ADC比特數(shù)的增加,采樣信號的精度也會增加。 (圖像來源:Digi-Key Electronics)

在上表中,0.5 LSB限值的計算等于100 * 0.5/2 N ,其中N等于SAR-ADC的位數(shù)。 AD4003BRMZ-ND是一個18位SAR-ADC,因此根據(jù)表格,18位ADC所需的時間常數(shù)為13。

SAR-ADC輸入信號必須在轉(zhuǎn)換器的時間。對于ADA4003轉(zhuǎn)換器,這至少為290 ns。

ADA4940-1,0.1%,2 V步進建立時間為37 ns。因此,我們很有可能在290 ns(ADC的采集時間tAQU)內(nèi)進行采樣。

要考慮的最后一個關(guān)鍵問題是系統(tǒng)噪聲。

系統(tǒng)噪聲

最好使放大器的噪聲貢獻至少比SAR-ADC噪聲低五倍。 SAR-ADC噪聲規(guī)范是SNR或信噪比。 SNR規(guī)格單位為分貝或dB。

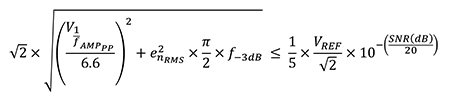

其中V1/f_AMP_PP是以rms為單位的峰峰值閃爍噪聲,en_RMS是寬帶放大器噪聲,f-3dB是3 dB帶寬Rflt/Cflt濾波器的設(shè)計。

設(shè)計#2

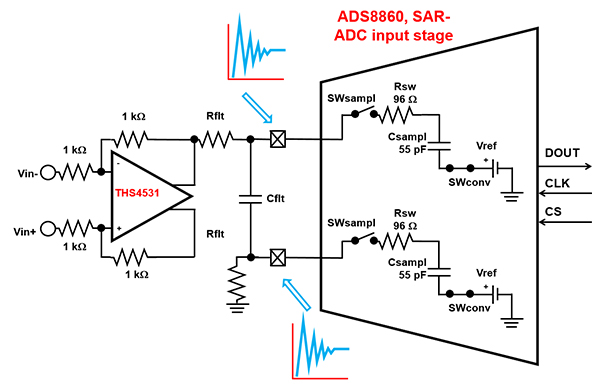

設(shè)計二采用德州儀器的ADS8860IDRCT,16位,1 MSPS,SAR-ADC和THS4531ID,全差分運算放大器。 SAR-ADC輸入結(jié)構(gòu)的基本模型還包括兩個開關(guān)(SWsampl,SWconv),輸入開關(guān)電阻(Rsw)和采樣電容Csampl(圖4)。

圖4:ADS8860具有偽差分輸入級。良好的SAR-ADC輸入模型有助于確定合適的放大器驅(qū)動器和抗混疊濾波器。 (圖片來源:Digi-Key Electronics)

ADS8860開關(guān)與AD4003的操作類似。雖然兩個ADS8860輸入均采集各自的輸入信號,但反相輸入的輸入范圍僅限于幾百毫伏。當采樣開關(guān)(SWsampl)閉合時,兩個輸入都經(jīng)歷相同的高頻電壓/電流尖峰。

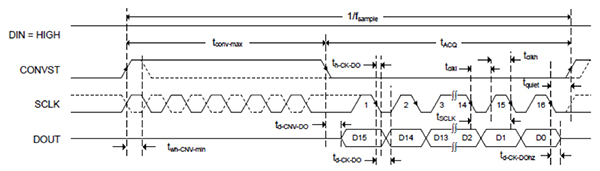

ADS8860的tAQU和吞吐速率(1/fsample),1 MHz采樣,16位SAR-ADC分別為290 ns和1μs(圖5)。

圖5:ADS8860 3線操作。 CONVST用作片選(圖像源。德州儀器)

輸入信號伏特每微秒最小壓擺率(SRmin)等于p * fin * Vout-pp * 10 -6 。例如,如果頻率和輸出峰峰值電壓(Vout-pp)分別為250kHz和2伏,則信號轉(zhuǎn)換速率為1.57伏/微秒。同樣,同樣的經(jīng)驗法則適用:選擇轉(zhuǎn)換速率大于或等于2 * SRmin的運算放大器。 THS4531指定的壓擺率為200伏/μsec。

確定Cflt

對于ADS8860,Cflt必須等于或大于Csampl的十倍,或550 pF(圖1) )。對于這篇文章,Cflt是1 nF。 Cflt過程應(yīng)該再次為C0G或NPO。

確定Rflt作為隔離劑和抗混疊濾波器的值

Rflt/Cflt對增加一個極點和零到放大器的開環(huán)傳遞函數(shù)(圖6)。

圖6:德州儀器THS4531的開環(huán)增益與頻率曲線。 Rflt和Cflt改變放大器的開環(huán)增益曲線。為了穩(wěn)定,開環(huán)增益(Aol)和閉環(huán)增益(Acl)曲線的閉合速率必須為20 dB/decade。 (圖像來源:Digi-Key Electronics)

第一種設(shè)計的Rflt和Cflt值,使用THS4531和ADS8860,分別等于50 W和1 nF(等式1,2和3) )。

這個一階抗混疊濾波器的響應(yīng)取決于Rflt和Cflt的值。該濾波器的轉(zhuǎn)角頻率的變量是fflt(等式4)。 Rflt和Cflt以高于1.13 MHz的20 dB/decade的速率衰減模擬路徑中的噪聲。請注意,fflt等于fzx。

放大器選擇

放大器的建立時間與Rflt/Cflt網(wǎng)絡(luò)的建立時間相結(jié)合,以產(chǎn)生復(fù)合系統(tǒng)建立時間。/p>

驅(qū)動器運算放大器Rflt和Cflt組合的目標之一是創(chuàng)建一個環(huán)境,使信號穩(wěn)定在小于或等于SAR-ADC的0.5 LSB的電壓。隨著SAR-ADC分辨率的提高,建立容差變得越來越小(表1)。 ADS8860是一款16位SAR-ADC。根據(jù)表格,16位ADC所需的時間常數(shù)為12。

SAR-ADC輸入信號必須在轉(zhuǎn)換器的tAQU時間內(nèi)穩(wěn)定下來。對于ADS8860轉(zhuǎn)換器,這至少為290 ns。 THS4531的0.01%,2伏步進建立時間為150 ns。因此,很有可能在290 ns(ADC的采集時間tAQU)內(nèi)進行采樣。

結(jié)論

如上所述,數(shù)據(jù)僅與其準確性一樣有效。對于工業(yè)和醫(yī)療應(yīng)用,精度至關(guān)重要,因此成功的設(shè)計始于數(shù)據(jù)采集。

本文提供設(shè)計方程式,以獲得SAR-ADC器件的正確驅(qū)動放大器和抗混疊濾波器。這些方程式將放大器的帶寬,壓擺率和噪聲與SAR-ADC的轉(zhuǎn)換時間和采集時間相匹配,從而創(chuàng)建一個穩(wěn)定,精確的系統(tǒng)。通過回顧和理解設(shè)計公式,可以使用所示的產(chǎn)品和設(shè)計實例來設(shè)計SAR-ADC驅(qū)動放大器系統(tǒng)。

請注意,模擬和臺架驗證是最后的步驟在這個設(shè)計過程中。

-

濾波器

+關(guān)注

關(guān)注

162文章

8107瀏覽量

181341 -

運算放大器

+關(guān)注

關(guān)注

216文章

5683瀏覽量

176075 -

模數(shù)轉(zhuǎn)換器

+關(guān)注

關(guān)注

26文章

3315瀏覽量

128056

發(fā)布評論請先 登錄

抗混疊濾波器設(shè)計的3條指導(dǎo)原則

請問抗混疊濾波器的使用場合

濾波器基礎(chǔ):抗混疊

關(guān)于設(shè)計抗混疊濾波器容易忽視的三條建議

設(shè)計抗混疊濾波器的三個指導(dǎo)原則是什么

高精度SAR模數(shù)轉(zhuǎn)換器抗混疊濾波的考慮因素

為精密醫(yī)療和工業(yè)模數(shù)轉(zhuǎn)換設(shè)計可靠的抗混疊濾波器

為精密醫(yī)療和工業(yè)模數(shù)轉(zhuǎn)換設(shè)計可靠的抗混疊濾波器

評論