鎖相環是最通用的電路功能之一。它們用于為處理器提供時鐘(相當良好的情況),以及用于在固定和調諧頻率發送器和接收器中建立調諧。

然而,最困難的挑戰之一是在無線鏈路中恢復,清理和重新計時定時信號。與處理器時鐘不同,此處通道的時鐘信號不是顯式或單獨的信號,而是嵌入在已調制的數據流中。即使發送和接收時鐘都是完美的并且也完美同步(從未出現過這種情況),該通道將具有噪聲,衰減,變化的SNR,失真以及許多其他腐蝕因素。

除了在無線信道中使用外,PLL在有線和光纖鏈路中起著類似的作用。在后兩種情況下,與無線相比,接收信號通常較少損壞且更穩定,因此稍微簡化了任務,但數據速率通常要高得多(某些光鏈路的數十Gbps),這加劇了挑戰。因此,PLL必須克服不同的困難,具體取決于通道介質。

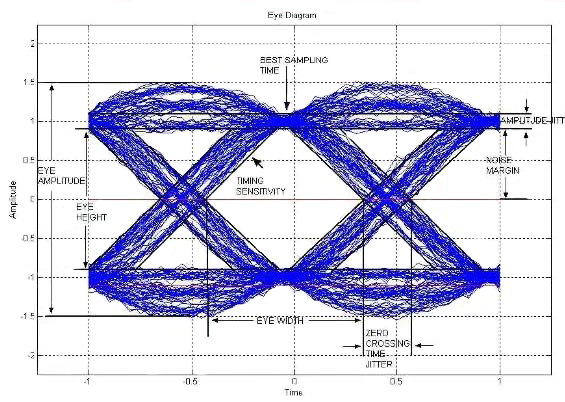

時鐘恢復挑戰的復雜性在與通信通道相關的最有用圖表中清晰顯示,眼圖(圖1) 1 。該圖實時覆蓋了所有接收到的數據流位,從而構建了一個復合數據,顯示接收器的定時抖動,失真和衰減程度。

圖1:使用恢復的系統時鐘覆蓋所有接收數據位的眼圖,揭示了有關抖動,衰減,失真的大量信息和它所代表的“理想”數字信號相比,接收信號的許多其他特性。 (由Yellow Fourier Technologies Private Ltd.提供)

雖然理想的數據位看起來像方波,但任何實際位都具有非垂直斜率和圓角作為其最小缺陷;此外,實際接收信號將具有各種抖動,失真和衰減。由于信道限制,比特在時間上延伸,它們重疊,結果是符號間干擾(ISI),這使得更難以實現低誤碼率(BER)。

因此,接收機盡管存在許多破壞因素,但必須從接收的調制數據流中提取數據時鐘的定時。形式上,此功能稱為“時鐘和數據恢復”或“時鐘和數據重定時”(CDR),但通常用俚語“時鐘清理”來描述。接收器電路使用此恢復的時序來確定最佳時刻到對數據進行抽樣。目標是在接收的比特值上實現較低的誤碼率。

PLL

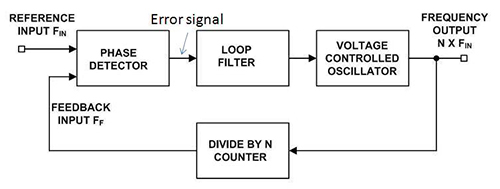

PLL使用閉環負反饋拓撲將接收信號的嵌入式時鐘與標準的本地生成時鐘相匹配(圖2)。 PLL的原理和操作已經在技術文章,書籍和網站中得到了廣泛的介紹,解釋主要是口頭的,直觀的方法,一直到那些提供強大的數學分析的方法 2,3 (PLL對于這種水平的調查來說,它是一個很好的候選者,因為它可以準確地建模)。雖然PLL多年來都是全模擬電路,但現在它們通常采用數字電路實現(例如,模擬VCO被數控振蕩器取代);在更高的頻率下,模擬仍然是唯一可行的選擇。

圖2:基本PLL是一種閉環,負反饋設計,可以比較本地生成的相位/頻率與接收信號的相位/頻率,并通過濾波后的誤差信號調整VCO以跟蹤輸入信號。

在所有PLL應用中,環路濾波器的細節對于證明所需的整體性能。當然,主濾波器參數是帶寬,其次是諸如阻尼,滾降陡度,通帶紋波和帶外衰減等因素。

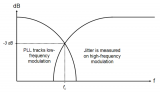

較窄的帶寬將導致恢復的時鐘輸出抖動減少,這是一件好事。然而,這個相同的窄帶寬意味著它將花費更長的時間來初始獲取接收信號并在該信號經歷頻率變化時將其鎖定。在無線鏈路中,這些頻移通常是由于多徑,失真,傳播延遲問題,甚至是多普勒效應(即使在地面速度下也很重要 - 想想雷達速度槍)。

無線鏈接也面臨著更多挑戰。對于有線和光學鏈路,端點和介質通常固定在適當的位置,因此許多腐蝕影響是相對靜止的;對于無線鏈路,一個或兩個端點可能正在移動并且信道本身正在改變,因此接收信號實時地經歷許多變化。因此,環路濾波器必須針對動態環境進行設計,超出噪聲和衰減等標準問題。

顯然,用于高速無線鏈路的PLL及其濾波器的參數最初是針對最可能的信道條件設置的。對于非常困難的情況的設計有時不使用單個固定濾波器,而是使用具有時間常數的更高級的濾波器和可以“動態”動態調整以匹配條件的其他參數。

與目標應用匹配的CDR IC

對于許多無線應用 - 尤其是Wi-Fi節點等大眾市場消費類應用 - CDR PLL嵌入在更大的IC中整個前端功能(盡管接收通道LNA [低噪聲放大器]和發射通道功率放大器[PA]通常是獨立的分立器件)。但是,用于高速鏈路的CDR PLL通常是獨立的,功能有限的設備,以滿足其性能要求

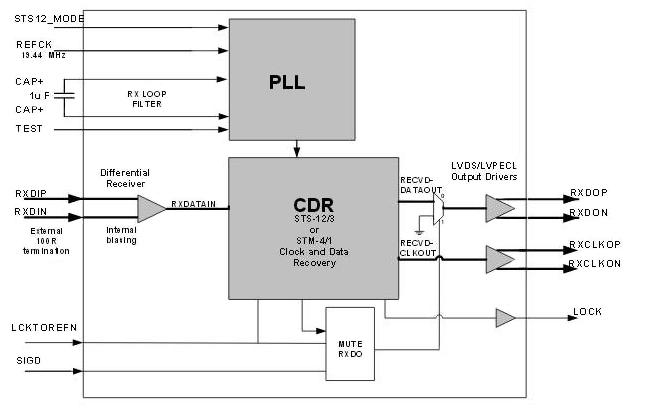

Exar XRT91L33就是這樣一個例子(圖3)。該IC設計用于SONET/SDH 622.08 Mbps STS-12/STM-4或155.52 Mbps STS-3/STM-1應用,并通過將其片上壓控振蕩器與輸入串行非返回同步來實現CDR功能到零(NRZ)數據流。 PLL在啟動時鎖定到本地參考時鐘。一旦實現鎖定,它就會嘗試鎖定傳入的數據流。

圖3:Exar用于SONET/SDH的XRT91L33 622.08 Mbps STS-12/STM-4或155.52 Mbps STS-3/STM-1應用程序提供時鐘數據和恢復,并且在信號丟失或由于任何原因無法實現鎖定的情況下也具有“后退”位置。

認識到可能存在信號丟失的時段,無論何時恢復的時鐘頻率偏離本地參考時鐘頻率超過約±500 ppm,時鐘恢復功能切換到本地參考時鐘,斷定失鎖,并將LOCK輸出引腳拉至低電平狀態。用戶為這款3.3 V,20引腳TSSOP器件提供外部濾波電容,以滿足預期情況。

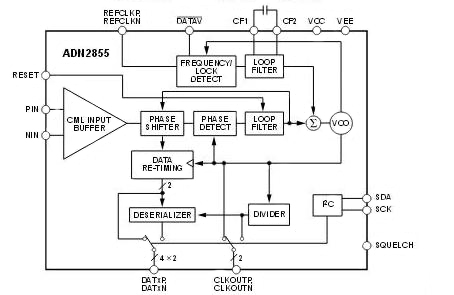

另一個例子是ADN2855,這是ADI公司的突發模式時鐘和數據恢復IC它可以在155.52 Mbps,622.08 Mbps,1244.16 Mbps或1250.00 Mbps數據速率下運行(可通過I 2 C接口選擇)。如圖4所示,它專為GPON/BPON/GEPON光線路終端(OLT)接收器應用而設計。 ADN2855需要一個鎖定到輸入數據頻率的參考時鐘;在操作中,IC的環路相對于該參考時鐘獲得頻率鎖定,將VCO拉向0-ppm頻率誤差。與Exar部分一樣,環路濾波器電容由用戶提供,標稱值為0.47μF。

圖4:ADN2855, ADI公司的突發模式時鐘和數據恢復IC可以運行高達1250.00 Mbps的數據速率;用戶提供的濾波電容的標稱值為0.47μF。

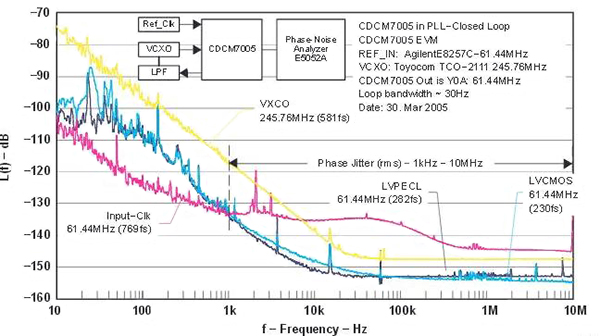

德州儀器公司的CDCM7005針對不同類別的應用,具有耐輻射性(版本CDCM7005-SP),低相位噪聲和低偏移時鐘同步器和抖動清除器,將壓控晶體振蕩器(VCXO)頻率與兩個參考時鐘之一同步; VCXO時鐘工作頻率高達2 GHz。堅固耐用的IC經過50 kRad(Si)TID認證,QML-V符合SMD 5962-07230標準,可在整個軍用溫度范圍(-55°C至125°C Tcase)下運行。

通過選擇外部VC(X)O和環路濾波器組件,可以調整PLL環路帶寬和阻尼系數,以滿足不同的系統要求。在10 kHz和10 MHz之間的頻率下,相位噪聲低于140 dB(圖5)。有兩個PLL鎖定指示:數字鎖定信號或模擬鎖定信號。兩個信號都指示PLL是否根據用戶選擇的鎖定條件達到或失去鎖定。與ADI公司的PLL一樣,許多工作參數都是通過串行總線用戶設置的;這里是SPI總線。

圖5:德州儀器(TI)的CDCM7005-SP是一款耐輻射PLL,可將壓控晶體振蕩器(VCXO)頻率與兩個參考頻率之一同步時鐘,工作頻率高達2 GHz。

-

處理器

+關注

關注

68文章

19819瀏覽量

233685 -

振蕩器

+關注

關注

28文章

3969瀏覽量

140469 -

發送器

+關注

關注

1文章

261瀏覽量

27166

發布評論請先 登錄

利用PLL清除無線鏈路中的時鐘信號

利用PLL清除無線鏈路中的時鐘信號

評論