MCU對應(yīng)用優(yōu)勢的挑戰(zhàn)已經(jīng)開始。具有片上固定功能處理子系統(tǒng)(即片上系統(tǒng)(SoC)FPGA)的現(xiàn)場可編程邏輯器件(FPGA)最近已成為高端處理應(yīng)用的潛在競爭者。這提出了一個問題:隨著應(yīng)用性能要求的不斷提高,SoC FPGA將成為更廣泛的應(yīng)用中的挑戰(zhàn)者,還是MCU會發(fā)展為更好地與SoC FPGA競爭?如果您正在考慮采用新設(shè)計,那么現(xiàn)在最適合您的方法是MCU還是SoC FPGA?

本文將快速回顧SoC FPGA與MCU相比的一些主要優(yōu)缺點。它還將探討最近的一些MCU創(chuàng)新,使其更加靈活,能夠更好地應(yīng)對SoC FPGA提供的一些關(guān)鍵優(yōu)勢。有了這些信息,您將能夠在下一次設(shè)計中更好地在MCU和SoC FPGA之間進行選擇。

SoC FPGA將新的靈活性與熟悉的處理系統(tǒng)相結(jié)合

SoC FPGA結(jié)合兩個世界中更好的。對于初學(xué)者來說,SoC FPGA提供了一個熟悉的處理系統(tǒng)--CPU - 來執(zhí)行熟悉的順序處理算法。實際上,許多SoC FPGA已經(jīng)融合在普適的ARM處理器架構(gòu)上,構(gòu)成了其“固定功能”處理子系統(tǒng)的基礎(chǔ)。這充分利用了ARM兼容工具,知識產(chǎn)權(quán)核心(IP核)和支持技術(shù)的廣泛生態(tài)系統(tǒng),使開發(fā)成為一個非常熟悉的過程。

SoC FPGA還為順序處理提供了靈活的可編程替代方案。可編程結(jié)構(gòu)可以實現(xiàn)您所需的任何硬件功能,以增強處理子系統(tǒng)中的順序處理能力。可編程結(jié)構(gòu)本質(zhì)上是并行的,因為多個硬件模塊可以同時操作,或者在邏輯復(fù)制的情況下并行操作,或者以流水線方式操作,其中算法被分成多個階段以便處理重疊。與順序方法相比,這兩種方法都可以產(chǎn)生巨大的吞吐量增益。

當可以使用并行或流水線技術(shù)在硬件中實現(xiàn)的算法的一部分需要高性能時,SoC FPGA特別有用(或組合)技術(shù)。讓我們看一個示例器件,以便更好地了解它在實際系統(tǒng)中的工作原理。

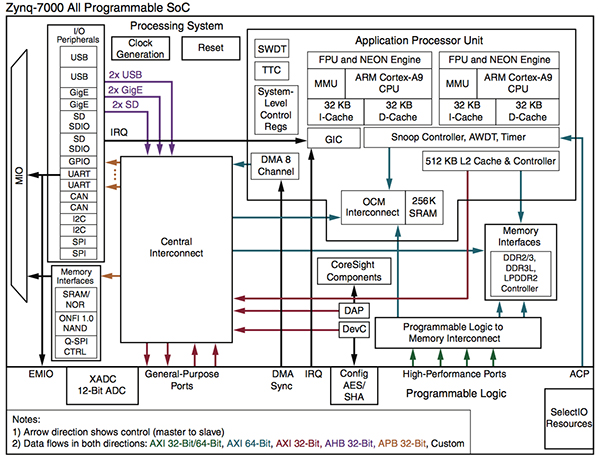

Xilinx Zynq-7000 SoC FPGA框圖如下圖1所示。該圖的上半部分顯示了芯片內(nèi)包含的所有固定功能模塊。這些模塊實現(xiàn)了完整的雙核ARM處理器應(yīng)用處理單元以及大量支持互連總線,外設(shè),存儲器和片外接口。可編程邏輯部分顯示在圖的最底部,可通過各種系統(tǒng)級接口訪問。該組織對SoC FPGA的可編程邏輯方面進行了新的改進,因為即使沒有可編程邏輯,固定功能元件也可以工作。這意味著處理器系統(tǒng)可以“啟動”然后配置可編程邏輯。以前的非SoC方法要求首先配置可編程邏輯,然后處理器才能啟動。通過顛倒這個序列,可編程邏輯成為處理器的資源,并且可以更容易地與硬件開發(fā)并行地開發(fā)代碼。

圖1:Xilinx Zynq SoC FPGA框圖。 (由賽靈思提供)

事實上,代碼開發(fā)人員可以將SoC中的可編程邏輯視為一種硬件資源,用于加速在處理器上實現(xiàn)時速度過慢的代碼段。一個設(shè)計團隊成員可能將他們的活動集中在創(chuàng)建程序員請求的硬件加速上,或者程序員可能自己實現(xiàn)硬件。無論哪種方式,算法都成為可用的多種實現(xiàn)選項的開發(fā)重點。

當有多個面向性能的算法同時進行時,SoC方法似乎效果最好。 SoC FPGA取得巨大成功的一個應(yīng)用領(lǐng)域是復(fù)雜的圖像處理。這些算法通常可以流水線化和/或并行化,使其成為FPGA加速的理想選擇。如果處理器還需要處理片上和片外的高帶寬流量(可能具有高速串行接口和大型片外緩沖存儲器),則從處理器卸載低級任務(wù)的額外硬件支持也可能需要支付大紅利

對SoC FPGA的多核響應(yīng)

還有其他方法可以為圖像處理等應(yīng)用實現(xiàn)并行和流水線實現(xiàn)。 MCU供應(yīng)商采取的一種方法是在芯片上實現(xiàn)多個處理引擎(多核),以允許設(shè)計人員分解復(fù)雜的算法。當每個處理器的體系結(jié)構(gòu)相同時,可以很容易地采用復(fù)雜的算法并將其分解為各自在不同但功能相同的處理器上執(zhí)行的部分。

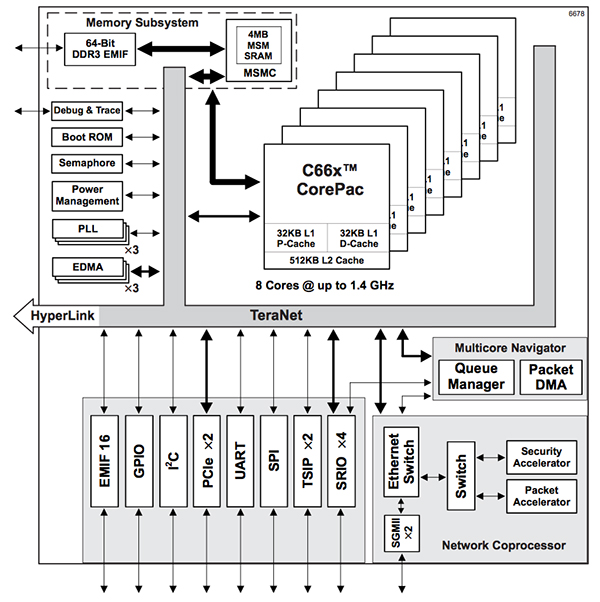

作為示例,德州儀器提供TMS320C66x多核固定和浮點數(shù)字信號處理器(DSP)具有8個DSP處理器以及網(wǎng)絡(luò)協(xié)處理器和多核導(dǎo)航器,可簡化使用硬件隊列的數(shù)據(jù)傳輸(圖2)。 DSP內(nèi)核為各種復(fù)雜算法(如音頻,視頻,分析,工業(yè)自動化和媒體處理)提供極高的處理能力。

圖2:德州儀器(TI)多核DSP框圖。 (德州儀器公司提供)

多核架構(gòu)的代碼開發(fā)與使用SoC FPGA的代碼開發(fā)有些類似,不同之處在于硬件加速是由DSP內(nèi)核而不是可編程結(jié)構(gòu)完成的。當一個核心無法足夠快地實現(xiàn)算法時,只需將另一個核心放在其上即可。繼續(xù)這樣做,直到你用完核心或達到你的性能目標。可能需要進行調(diào)整和優(yōu)化以獲得最后的功耗/性能效率,但是一些更高級的工具可以通過提供有助于優(yōu)化過程的性能和功耗配置文件來提供幫助。

雙核MCU

多核方法不需要僅用于最高性能的應(yīng)用。通常,SoC FPGA可以在性能較低的應(yīng)用中找到,在這些應(yīng)用中需要優(yōu)化功耗和處理能力。由于可編程結(jié)構(gòu)可用于實現(xiàn)部分算法,因此實現(xiàn)所需的總功率可能遠遠低于高端DSP或多核解決方案。

MCU制造商也發(fā)現(xiàn)了這一趨勢,通過將雙核處理器放在單個設(shè)備上進行響應(yīng)。在某些情況下,使用高性能處理器和低性能處理器。這允許高性能處理器實現(xiàn)算法的更復(fù)雜部分和低性能處理器,以處理不太復(fù)雜的管理任務(wù)。較低性能的處理器可以在大多數(shù)時間處于活動狀態(tài),使用的功率低于高性能核心。 (請注意,多核系統(tǒng)可以使用類似的方法,只使用動態(tài)達到目標性能級別所需的核心數(shù)。這實現(xiàn)起來有點復(fù)雜,但如果算法需要,最終會非常有效各種性能水平在短時間內(nèi)變化很大。)

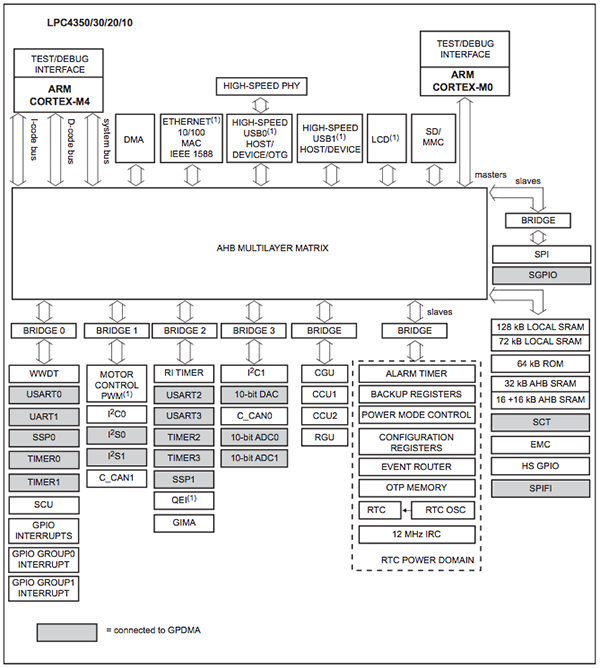

利用高性能和低性能處理器的雙核MCU的一個例子是恩智浦半導(dǎo)體LPC4350 。如圖3所示,它下面有一個ARM Cortex-M4和一個Cortex-M0。 M4用于高性能任務(wù),而M0可用于通用管理功能。實際上,如果不需要M4子部分甚至可以斷電,并且在處理請求需要時通電。這種方法適用于僅需要定期但需要快速響應(yīng)處理數(shù)據(jù)的算法。作為一個例子,安全攝像機上的圖像處理在圖像變化時會非常沉重,但在圖像靜止時則不需要。

圖3:恩智浦雙核MCU框圖。 (恩智浦提供)

即便是低端也是可編程的

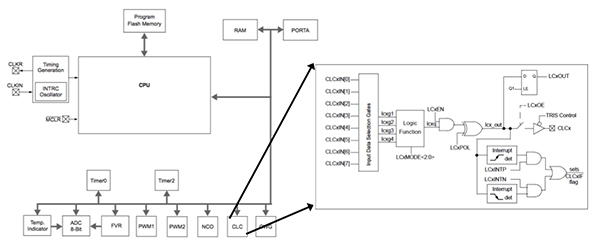

不要以為只有高端和中端MCU才能增加新的靈活性以提高靈活性。即使是低端MCU也在增加可編程功能,可能不是對SoC FPGA的響應(yīng),而是作為一種在可編程邏輯器件已經(jīng)存在數(shù)十年的情況下“片上”拉出少量外部邏輯的方法。 Microchip PIC10F320增加了可編程邏輯,位于可配置邏輯單元(CLC)模塊中。 PIC10F320的框圖以及更詳細的CLC視圖如圖4所示.CLC可以根據(jù)器件輸入,內(nèi)部時鐘,內(nèi)部外設(shè)和寄存器位實現(xiàn)各種簡單的邏輯功能。 CLC甚至可以在低功耗模式下工作,使其成為喚醒事件的便捷來源,以便在不需要處理MCU時節(jié)省最大功率。

圖4:具有可編程邏輯框圖的Microchip MCU。 (由Microchip提供)

CLC在PIC10F320上特別有用,因為它只有幾個引腳。充分利用這些引腳并消除一些外部邏輯可以對電路板空間要求產(chǎn)生很大影響。即使在PAL和CPLD的早期階段,可編程邏輯提供的一大優(yōu)勢。現(xiàn)在,隨著低端MCU將可編程邏輯放在芯片上,我們可能會看到更少的MCU旁邊的低端PLD。這不是一個新的轉(zhuǎn)折!

總之,MCU和SoC FPGA解決了類似的應(yīng)用問題,并開始爭奪應(yīng)用優(yōu)勢。目前,挑戰(zhàn)主要在應(yīng)用領(lǐng)域的最高端,但最近的創(chuàng)新可能會擴大MCU與可編程設(shè)備之間的應(yīng)用重疊。

-

FPGA

+關(guān)注

關(guān)注

1642文章

21920瀏覽量

612080 -

mcu

+關(guān)注

關(guān)注

146文章

17718瀏覽量

358279 -

cpld

+關(guān)注

關(guān)注

32文章

1257瀏覽量

170675

發(fā)布評論請先 登錄

相關(guān)推薦

微芯Microchip PolarFire? SoC FPGA通過AEC-Q100汽車級認證

電機控制中MCU的選擇應(yīng)該如何考慮?(可下載)

三相負載箱與單相負載箱的區(qū)別與優(yōu)勢對比

SOPC、SoC 、FPGA的異同優(yōu)缺點介紹及常見應(yīng)用場景

SoC FPGA與MCU的優(yōu)勢對比,應(yīng)如何選擇

SoC FPGA與MCU的優(yōu)勢對比,應(yīng)如何選擇

評論