立即了解微控制器(MCU)領(lǐng)域的高端產(chǎn)品,您將發(fā)現(xiàn)具有與微處理器領(lǐng)域相似的微架構(gòu)和指令集特性的IC。實際上,德州儀器(TI)和飛思卡爾等公司都提供具有共享傳統(tǒng)的MCU和嵌入式目標微處理器。不過,這兩個細分市場之間存在顯著差異,從公司的芯片設(shè)計和制造戰(zhàn)略到集成功能集以及硬件中根深蒂固的軟件支持。嵌入式設(shè)計團隊必須仔細考慮他們的應(yīng)用,以便在考慮設(shè)備選擇之前,正確選擇采用MCU或微處理器路徑。從高層次看MCU和微處理器技術(shù),看起來這些細分市場相互對立。兩個陣營中都有兼容或重疊的指令集,并且MCU時鐘頻率已升級到接近微處理器段底端的點。

可擴展系列

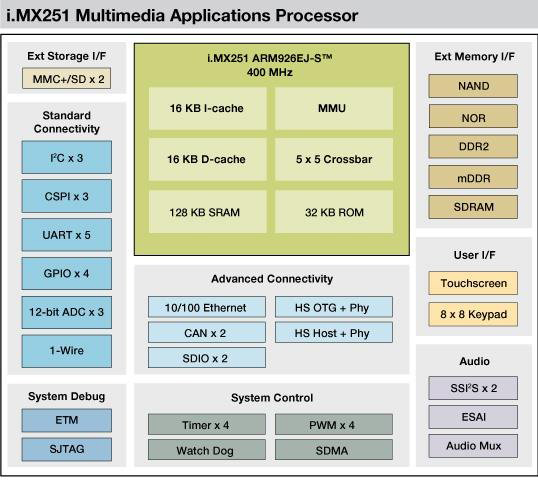

讓我們考慮一些似乎是兼容處理器技術(shù)平滑發(fā)展的例子,這些技術(shù)將MCU產(chǎn)品線推向微處理器領(lǐng)域。飛思卡爾提供基于ARM Cortex-M4內(nèi)核的Kinetis MCU系列,包括K10,K20,K30,K40和K60 MCU等產(chǎn)品。在微處理器方面,飛思卡爾提供i.MX微處理器系列。 i.MX1/2,i.MXL和i.MXS系列基于ARM9內(nèi)核。 i.MX3x系列基于ARM11內(nèi)核,i.MX5x系列基于ARM Cortex-A8內(nèi)核。

顯然,基于飛思卡爾ARM的產(chǎn)品組合中使用的CPU核心存在差異。我們將在整篇文章中討論內(nèi)核中的體系結(jié)構(gòu)差異,但在簡化的比較中,它們都支持相同的基本指令集。 Cortex-M4內(nèi)核針對低功耗和更小的芯片尺寸進行了優(yōu)化。 ARM9,ARM11和ARM Cortex-A8進程基本上代表了性能功能的擴展。我們可以與飛思卡爾基于PowerPC的產(chǎn)品組合進行大致相同的比較,包括MPC6x和MPC7x微處理器系列以及PowerPC MCU系列。

對于TI(圖1),基于ARM的系列和以DSP為中心的處理器都有一個平行的故事。 Stellaris MCU系列基于ARM-Cortex M3內(nèi)核,包括3000,5000,6000,8000和9000系列MCU。 Sitara微處理器系列包括基于ARM9的AM1x處理器和基于Cortex-A8的ARM3x處理器。

圖1:TI Concerto MCU系列基于該公司的C2000系列架構(gòu),結(jié)合了ARM Cortex-M3內(nèi)核和支持浮點的,以DSP為中心的內(nèi)核。

MCU與微處理器性能的關(guān)系

MCU和微處理器領(lǐng)域確實從高層次看起來是連續(xù)的。您幾乎可以考慮兩者之間的邊界,例如,比較16位和32位MCU,您可以在許多應(yīng)用程序中重疊選擇。但這樣做是錯誤的。讓我們深入挖掘,找出原因。

從某些方面來看,MCU和微處理器從性能角度來看是非常接近的。考慮EEMBC(Embedded Microprocessor Benchmark Consortium)發(fā)布的CoreMark基準測試。具體來說,讓我們討論從比較中消除時鐘速度的CoreMark/Mhz分數(shù)。飛思卡爾Kinetis MCU的公布分數(shù)范圍為2.05至2.95。 i.MX5系列的公布分數(shù)范圍為2.28至2.45。

Kinetis和i.MX5的性能接近于Kinetis甚至在每MHz的基礎(chǔ)上占據(jù)上風(fēng)。當(dāng)然我們知道i.MX5速度更快,部分原因是時鐘速度。在i.MX產(chǎn)品組合中,最大時鐘速度從400 MHz擴展到1.2 GHz。最快的Kinetis處理器運行速度為150 MHz,盡管飛思卡爾已經(jīng)宣布了200 MHz設(shè)備的計劃。讓我們根據(jù)圖片中的時鐘速度重新考慮CoreMark得分。運行頻率為800 MHz的i.MX5得分為1964,而150 MHz MCU的最高Kinetis得分為427。

時鐘速度差異

實際上,從時鐘速度開始,由于多種原因,MCU和微處理器性能之間仍然存在顯著差距。最大時鐘速度取決于制造過程和CPU微體系結(jié)構(gòu)。

我們都知道隨著制造商將摩爾定律推向更精細的工藝幾何形狀,時鐘速度會上升。 MCU將始終位于較舊的進程上。 TI的C2000營銷經(jīng)理Sangmin Chon表示,“在MCU中,我們將永遠落后于幾個節(jié)點。” Chon指出,與微處理器相比,MCU通常部署在更具環(huán)境挑戰(zhàn)性的應(yīng)用中,例如高溫應(yīng)用。這一事實導(dǎo)致MCU制造商依賴強大的更保守的工藝節(jié)點。

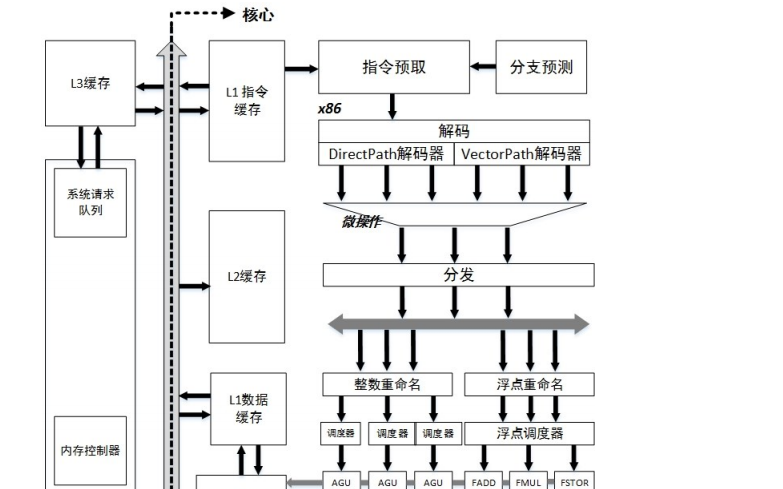

現(xiàn)在讓我們考慮一些微控制器元件,這些元件將控制MCU的時鐘速度。深度流水線是一項重要功能,可以加快微處理器的時鐘速度。一些微處理器使用了20級或更多級。最近的趨勢更多的是10個階段,而MCU通常依賴于3到5個階段。

我們現(xiàn)在看一個差異很小的例子。飛思卡爾最快的PowerPC MCU基于具有4級的e300內(nèi)核。 MPC6x和MPC7x微處理器基于具有7級的e600內(nèi)核。從理論上講,e300內(nèi)核的運行速度為667 MHz,而e600的運行速度為1.8 Ghz。管道不是唯一的門控因素,但它是一個重要因素。

當(dāng)然,MCU設(shè)計人員可以增加流水線深度,但這樣做與許多公認的MCU特性背道而馳。例如,考慮中斷響應(yīng)。中斷要求CPU在上下文切換后重新加載管道,因此存在許多沒有完成指令的周期。相對于微處理器,MCU在時鐘速度方面已經(jīng)處于劣勢,因此管道重載過程會在長管道中產(chǎn)生不可接受的延遲。

長管道也會影響硅足跡,芯片尺寸直接影響成本。微處理器市場更愿意接受更高的價格以獲得更好的性能,而在大多數(shù)基于MCU的系統(tǒng)中,成本仍然是一個巨大的問題。

內(nèi)存注意事項

讓我們繼續(xù)比較MCU中相對于微處理器的內(nèi)存情況以及內(nèi)存實現(xiàn)對應(yīng)用程序的影響。集成內(nèi)存一直是MCU領(lǐng)域的一個決定性原則,可以追溯到最早的產(chǎn)品,如8051.最初由英特爾設(shè)計,它至今仍然很受歡迎,并被許多制造商銷售。

TI的Chon說:“當(dāng)您想到嵌入式MCU空間時,您會想到具有嵌入式存儲器的設(shè)備。”Chon補充說,在大多數(shù)應(yīng)用中,內(nèi)存要求將指導(dǎo)設(shè)計團隊選擇MCU或MPU。大多數(shù)基于MCU的設(shè)計依靠集成的閃存來存儲代碼.TI的頂級ARM MCU,Stellaris 9000系列,集成了512 KB的閃存(圖2)。目前市場上的MCU集成了幾兆字節(jié)的閃存,但很明顯,MCU可以處理的應(yīng)用程序的大小受到限制。

圖2:TIS基于ARM Cortex-M3的Stellaris系列中的9000系列MCU集成了512 KB的閃存用于代碼存儲。

然后,片上閃存故事也有例外。例如,恩智浦半導(dǎo)體正在使用一種名為Quad SPI的接口(有時稱為SPIFI用于SPI閃存接口),其中包含許多MCU。 Quad SPI鏈路使用4條線,可以將閃存的訪問速度提高四倍。恩智浦表示,該接口可以產(chǎn)生40 Mbps的讀取速率。

恩智浦基于ARM Cortex-M4的LPC4300 MCU系列中的首批產(chǎn)品未集成任何閃存。實際上,LPC4330和LPC4350 MCU完全依賴于四SPI連接的存儲器。外部閃存被視為MCU存儲器映射的一部分,MCU可以從外部存儲器啟動。即使恩智浦推出集成閃存的LPC4300 MCU,Quad SPI功能也會派上用場,讓設(shè)計團隊可以選擇應(yīng)用中所需的內(nèi)存量。恩智浦產(chǎn)品營銷經(jīng)理Gordon Cooper表示,靈活性在多媒體和圖形應(yīng)用中尤為重要,因為集成閃存可以處理應(yīng)用程序所需的代碼大小。該接口不提供與微處理器一起使用的高速DRAM接口中的速度類型,但Quad SPI仍然具有MCU中通常不具備的可擴展性。

內(nèi)存管理或保護

大多數(shù)MCU和微處理器之間的另一個主要區(qū)別在于內(nèi)存管理或保護。這里討論的所有微處理器都將存儲器管理單元(MMU)集成為微體系結(jié)構(gòu)的一個特征。相比之下,大多數(shù)MCU集成了通常稱為內(nèi)存保護單元的內(nèi)容。

MMU和內(nèi)存保護單元均可用于對內(nèi)存空間進行分區(qū),并保護關(guān)鍵任務(wù)代碼和數(shù)據(jù)免遭篡改。例如,內(nèi)存分區(qū)可以專用于一個CPU任務(wù)的私人使用。操作系統(tǒng)還可以保留對存儲區(qū)域的訪問。 MMU更進一步,虛擬化內(nèi)存空間,允許操作系統(tǒng)無縫訪問碎片存儲器映射。

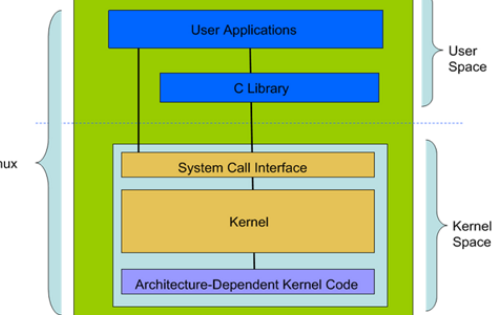

MMU的存在或缺乏是大多數(shù)設(shè)計團隊考慮處理器的另一個關(guān)鍵指導(dǎo)點。如果您的產(chǎn)品將運行Linux等通用操作系統(tǒng),則需要MMU。嵌入式應(yīng)用程序的大多數(shù)實時操作系統(tǒng)與MMU或內(nèi)存保護單元同樣適用。

雖然很少見,但您可以在選定的MCU中找到完整的MMU功能。例如,飛思卡爾PowerPC MCU系列包括一個MMU。 Atmel(圖3)還在其基于ARM9的SAM9產(chǎn)品系列中集成了MMU。

圖3:Atmel的SAM9XE MCU系列基于包含MMU的ARM9內(nèi)核。大多數(shù)MCU僅集成了內(nèi)存保護單元。

在Atmel的案例中,有一個適用于產(chǎn)品的命名法。 Atmel稱SAM9R和SAM9M系列為嵌入式微處理器。它稱兄弟SAM9XE產(chǎn)品為MCU。嵌入式微處理器提供更高的時鐘速度,最高可達400 MHz,并包括DRAM接口。但是,所有基于ARM9的產(chǎn)品都包含MMU,并且所有產(chǎn)品都以MCU方式集成了外設(shè)功能。

周邊集成

已經(jīng)提到了外設(shè)集成,讓我們在這個領(lǐng)域更深入一點。如今,微處理器和MCU都集成了豐富的外設(shè)功能,但組合通常存在差異。在微處理器上,您通常會找到主要的數(shù)字外設(shè)功能。典型示例包括以太網(wǎng)和USB,圖形控制器和音頻控制器。

在MCU空間中,您還可以找到連接外圍設(shè)備和圖形控制器,盡管通常針對較小的低分辨率顯示器。但是,在MCU中,您通常會找到許多模擬外設(shè),例如數(shù)據(jù)轉(zhuǎn)換器和脈沖寬度調(diào)制(PWM)外設(shè)。同樣總有例外。前面提到的Atmel嵌入式微處理器包括A/D轉(zhuǎn)換器和PWM。許多飛思卡爾的i.MX微處理器包括A/D轉(zhuǎn)換器,定時器,模擬音頻功能和PWM,如圖4所示。

圖4:飛思卡爾i.MX微處理器系列的一些成員包括以模擬為中心的外設(shè),如MCU中常見的外設(shè),包括i.MX251所示的A/D轉(zhuǎn)換器和PWM。

客戶驅(qū)動的決策

盡管微處理器和MCU空間之間存在技術(shù)差異,但設(shè)計團隊將面臨必須在高端MCU和低端微處理器之間進行選擇的情況。在這些客戶的推動下,IC制造商正在對重疊空間作出反應(yīng)。 TI的Chon指出,“從微處理器方面來看,我們確實看到線路模糊。”

TI所做的一件事是為其基于ARM9和Cortex-A8的處理器引入StarterWare軟件開發(fā)包。 StarterWare是免費的,在許多情況下無需復(fù)雜的操作系統(tǒng)。此外,該工具還可以快速開發(fā)具有USB和網(wǎng)絡(luò)堆棧等功能的系統(tǒng)。事實上,該軟件更像是公司隨MCU提供的StellarisWare工具,而不是它歷史上為微處理器客戶提供的基于操作系統(tǒng)的工具。

這也是客戶的需求,推動了TI的ARM-plus-DSP產(chǎn)品在MCU和微控制器領(lǐng)域的發(fā)展。從外部看,您可能會認為TI希望在兩個部分提供類似的架構(gòu),從而提供可擴展的性能和功能集。

實際上,客戶出于完全無關(guān)的原因推動了ARM-plus-DSP產(chǎn)品。對于TMS320C6A816x和OMAP系列,客戶需要DSP來處理數(shù)學(xué)密集型的多媒體和通信中心例程,同時還需要能夠托管復(fù)雜操作系統(tǒng)和用戶應(yīng)用程序的處理器。在Concerto MCU的情況下,客戶正在尋找ARM內(nèi)核的便利性,因此很容易實現(xiàn)USB和網(wǎng)絡(luò)堆棧等功能。在MCU的情況下,DSP主要針對工業(yè)類應(yīng)用,如電機和驅(qū)動器的實時控制。

查看應(yīng)用程序需求

在這里總結(jié)我們的討論,消息不是一個簡單的消息。 MCU和微處理器部分正在向重疊方向發(fā)展,有些情況可能會在您的設(shè)計中足夠。您應(yīng)該通過高級別的應(yīng)用程序要求和選擇來啟動決策過程,例如是否需要強大的操作系統(tǒng)導(dǎo)致微處理器,或者系統(tǒng)占用空間是否要求代碼適合MCU的集成內(nèi)存。 IC制造商建議,在許多情況下,設(shè)計團隊知道他們將遵循MCU或微控制器設(shè)計路徑。如果選擇模糊,團隊必須密切評估微處理器外圍集成的增長趨勢,或者MCU中出現(xiàn)的時鐘頻率和外部存儲器支持的不斷增加。正是功能集中當(dāng)前約定的這些例外可能會導(dǎo)致正確的選擇。

-

微控制器

+關(guān)注

關(guān)注

48文章

7840瀏覽量

153295 -

處理器

+關(guān)注

關(guān)注

68文章

19714瀏覽量

232723 -

cpu

+關(guān)注

關(guān)注

68文章

11003瀏覽量

215040

發(fā)布評論請先 登錄

相關(guān)推薦

無線傳感器網(wǎng)絡(luò)的體系結(jié)構(gòu)分析

無線傳感器網(wǎng)絡(luò)體系結(jié)構(gòu)研究

帶你了解Linux內(nèi)核體系結(jié)構(gòu)

linux內(nèi)核體系結(jié)構(gòu)是由哪些部分組成的

了解體系結(jié)構(gòu) - 介紹 Arm 體系結(jié)構(gòu)

Arm的DRTM體系結(jié)構(gòu)規(guī)范

基于體系結(jié)構(gòu)的國防經(jīng)濟管理系統(tǒng)研究

軟件體系結(jié)構(gòu)框架研究

LTE體系結(jié)構(gòu)

基于InsiderThreat的安全防御體系結(jié)構(gòu)研究_王輝

軟件體系結(jié)構(gòu)的分析

arm內(nèi)核全解析_arm內(nèi)核體系結(jié)構(gòu)分類介紹

了解Linux體系結(jié)構(gòu)和內(nèi)核結(jié)構(gòu)

Linux內(nèi)核的處理器體系結(jié)構(gòu)的詳細資料說明

CPU內(nèi)核中的體系結(jié)構(gòu)差異研究

CPU內(nèi)核中的體系結(jié)構(gòu)差異研究

評論