根據定義,高速模數轉換器(ADC)是對模擬信號進行采樣的器件,因此必定有采樣時鐘輸入。某些使用ADC的系統設計師觀測到,從初始施加采樣時鐘的時間算起,啟動要比預期慢。出人意料的是,造成此延遲的原因常常是外部施加的ADC采樣時鐘的啟動極性錯誤。

許多高速ADC的采樣時鐘輸入具有如下特性:

差分

內部偏置到設定的輸入共模電壓(VCM)

針對交流耦合時鐘源而設計

差分ADC時鐘輸入緩沖器常常有一個設計好的切換閾值偏移。如果沒有這種偏移,切換閾值將發生在0 V差分。如果無偏移的時鐘緩沖器被解除驅動且交流耦合,則器件內部會將時鐘輸入(CLK+和CLK?)拉至共模電壓。這種情況下,CLK+上的直流電壓和CLK?上的電壓將相同,意味著差分電壓等于0 V。

在理想世界里,若輸入上無信號,則時鐘緩沖器不會切換。但在現實世界里,電子系統中總是存在一些噪聲。在輸入切換閾值為0 V的假想情況中,輸入上的任何噪聲都會跨過時鐘緩沖器的切換閾值,引發意外切換。

若將足夠大的輸入切換閾值偏移設計到時鐘緩沖器中,則同樣的情況不會引發切換。因此,為交流耦合差分時鐘緩沖器的切換閾值設計一個偏移是有利的,故而時鐘緩沖器常常有一個切換閾值偏移。

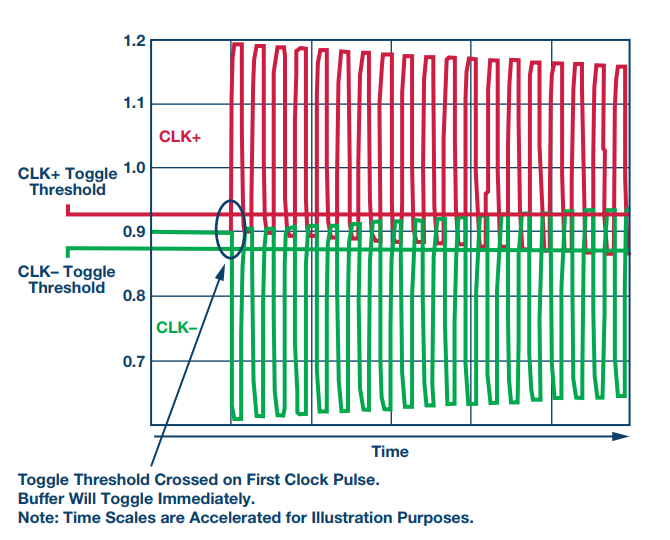

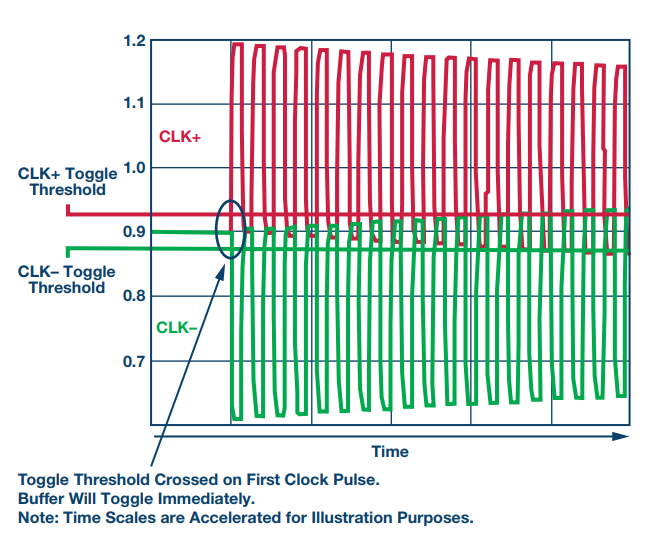

不施加時鐘時,時鐘緩沖器中的內部偏置電路將CLK+和CLK?各自拉至相同的VCM。初始施加時鐘時,CLK+和CLK?將偏離先前確立的VCM,分別向正方向和負方向(或負方向和正方向)擺動。在圖1中,VCM = 0.9 V。

圖1顯示在器件處于非活動狀態(要么初始啟動系統,要么時鐘驅動器在一段時間內處于非活動狀態)之后施加時鐘的情況。這種情況下,CLK+在第一個邊沿向正方向擺動,CLK?向負方向擺動。若在輸入切換閾值上增加一個正偏移,此時鐘信號將在第一個邊沿切換時鐘緩沖器,如圖1所示。時鐘輸入緩沖器將立即產生一個時鐘信號。

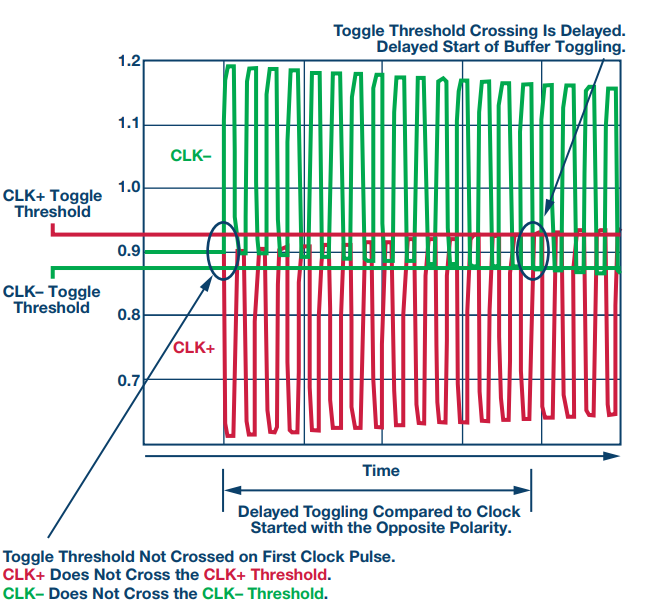

如果時鐘偶然從相反極性啟動,則CLK?在第一個邊沿向正方向擺動,CLK+向負方向擺動。在給輸入切換閾值增加相同正偏移的情況下,此時鐘信號在第一個邊沿及隨后的邊沿都不會切換時鐘緩沖器,直至波形被拉向穩態,隨著時間推移而跨過切換閾值,如圖2所示。

可以看出,初始啟動時鐘的極性對帶有輸入閾值偏移的時鐘緩沖器的切換具有重要影響。在其中一種情況下(本例中CLK+初始上升),當初始施加時鐘時,時鐘緩沖器立即開始切換,完全符合預期。在極性相反的情況下(本例中CLK+初始下降),當初始施加時鐘時,時鐘緩沖器不會立即開始切換。

如果您發現ADC啟動有意外的延遲,請嘗試改變時鐘啟動極性,這可能會使啟動時間恢復正常。

-

adc

+關注

關注

99文章

6709瀏覽量

549227

發布評論請先 登錄

嵌入式Linux啟動時間優化的秘密之四-啟動腳本

如何減少dsp啟動時間?

電機啟動時間一般是多久?怎么縮短啟動時間呢?

電機啟動電流與啟動時間的關系是什么?

電腦啟動時間長的原因及處理方法

Linux系統啟動時間優化方案

Linux系統啟動時間優化方案

基于FPGA的PCIe設備如何才能滿足PCIe設備的啟動時間的要求?

你知道ADC時鐘極性與啟動時間?

你知道ADC時鐘極性與啟動時間?

評論