基于Xilinx ? Zynq SoC和ADI V波段芯片組的完整60 GHz雙向數(shù)據(jù)通信方案為小型蜂窩回程市場(chǎng)提供了性能和靈活性。

世界蜂窩網(wǎng)絡(luò)對(duì)數(shù)據(jù)的需求不斷增長(zhǎng),運(yùn)營(yíng)商正在尋找到2030年將容量增加5000倍的方法。 1 要實(shí)現(xiàn)這一目標(biāo),需要將通道性能提高5倍,20 ×分配頻譜的增加,以及蜂窩站點(diǎn)數(shù)量增加50倍。

許多這些新小區(qū)將被放置在大多數(shù)流量來(lái)源的室內(nèi),而光纖是匯集流量的首選回到網(wǎng)絡(luò)。但是有許多戶外場(chǎng)所無(wú)法使用光纖或連接太昂貴,對(duì)于這些情況,無(wú)線回程是最可行的替代方案。

5 GHz的免許可頻譜可用且不需要線路視線(LOS)路徑。但是,帶寬有限,并且由于流量大和天線模式寬,幾乎可以保證該頻譜的其他用戶的干擾。

60 GHz的通信鏈路正在成為提供這些回程鏈路的主要競(jìng)爭(zhēng)者。成千上萬(wàn)的室外電池將滿足容量需求。該頻譜也是未經(jīng)許可的,但與6 GHz以下的頻率不同,它包含高達(dá)9 GHz的可用帶寬。此外,高頻率允許非常窄且聚焦的天線方向圖,這些天線方向圖有些抗干擾,但需要LOS路徑。

基于FPGA和基于SoC的調(diào)制解調(diào)器越來(lái)越多地用于各種無(wú)線回程解決方案,因?yàn)槭褂盟鼈兊钠脚_(tái)可以模塊化和定制,從而降低OEM的總體擁有成本。對(duì)于這些鏈路的無(wú)線電部分,收發(fā)器已集成到基于硅的IC中,并封裝在低成本的表面貼裝部件中。

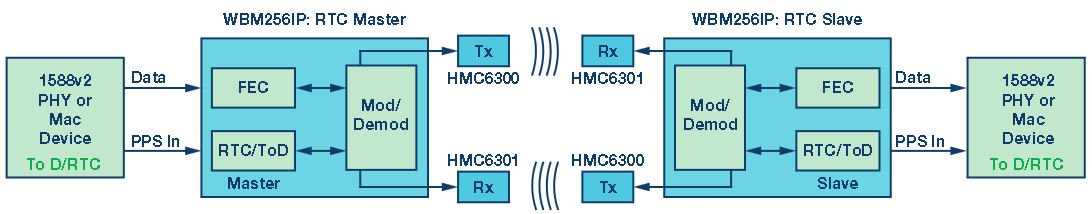

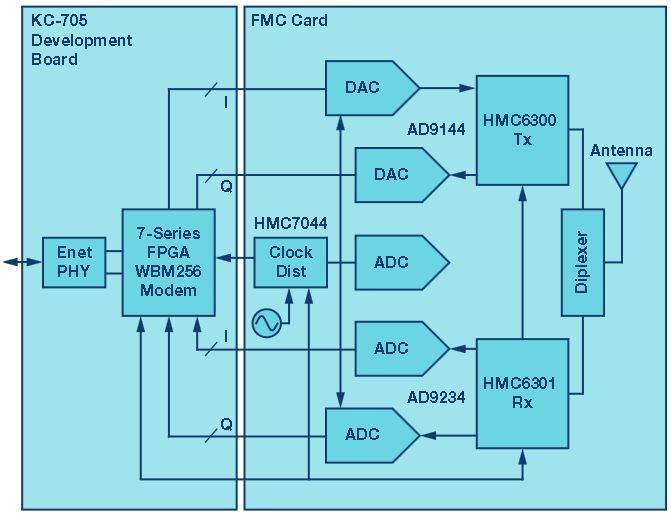

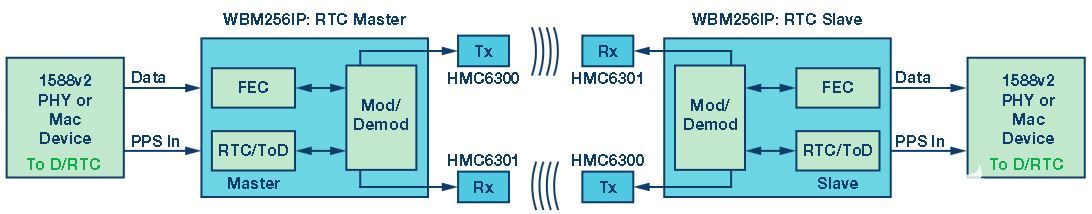

商用部件可用于構(gòu)建完整的60 GHz雙向數(shù)據(jù)通信圖1中的解決方案舉例說明了該鏈路。該設(shè)計(jì)由Xilinx和Hittite Microwave(現(xiàn)為ADI公司的一部分)開發(fā),包括Xilinx調(diào)制解調(diào)器和ADI公司的毫米波無(wú)線電。此鏈接符合小型蜂窩回程市場(chǎng)的性能和靈活性要求。

如圖1所示,創(chuàng)建此鏈路需要兩個(gè)節(jié)點(diǎn)。每個(gè)節(jié)點(diǎn)包含一個(gè)發(fā)送器(帶調(diào)制器)及其相關(guān)的模擬發(fā)送器鏈,以及一個(gè)接收器(帶解調(diào)器)及其相關(guān)的模擬接收器鏈。

調(diào)制解調(diào)器卡與模擬和分立器件集成在一起。它包含數(shù)字實(shí)現(xiàn)的振蕩器,以確保頻率合成的準(zhǔn)確性,所有數(shù)字功能都在FPGA或片上系統(tǒng)(SoC)中執(zhí)行。該單載波調(diào)制解調(diào)器內(nèi)核支持從QPSK到256 QAM的調(diào)制,信道帶寬高達(dá)500 MHz,數(shù)據(jù)速率高達(dá)3.5 Gbps。調(diào)制解調(diào)器還支持頻分雙工(FDD)和時(shí)分雙工(TDD)傳輸方案。強(qiáng)大的調(diào)制解調(diào)器設(shè)計(jì)技術(shù)降低了本地振蕩器的相位噪聲影響。包括強(qiáng)大的低密度奇偶校驗(yàn)(LDPC)編碼,以提高性能和鏈路預(yù)算。

毫米波調(diào)制解調(diào)器

毫米波調(diào)制解調(diào)器使基礎(chǔ)設(shè)施供應(yīng)商能夠開發(fā)靈活,成本優(yōu)化的,可定制的無(wú)線回程網(wǎng)絡(luò)鏈接。它完全自適應(yīng),功耗低,占地面積小,可用于部署室內(nèi)和全室外點(diǎn)對(duì)點(diǎn)鏈路以及點(diǎn)對(duì)多點(diǎn)微波鏈路。該解決方案使運(yùn)營(yíng)商能夠構(gòu)建可擴(kuò)展的現(xiàn)場(chǎng)可升級(jí)系統(tǒng)。

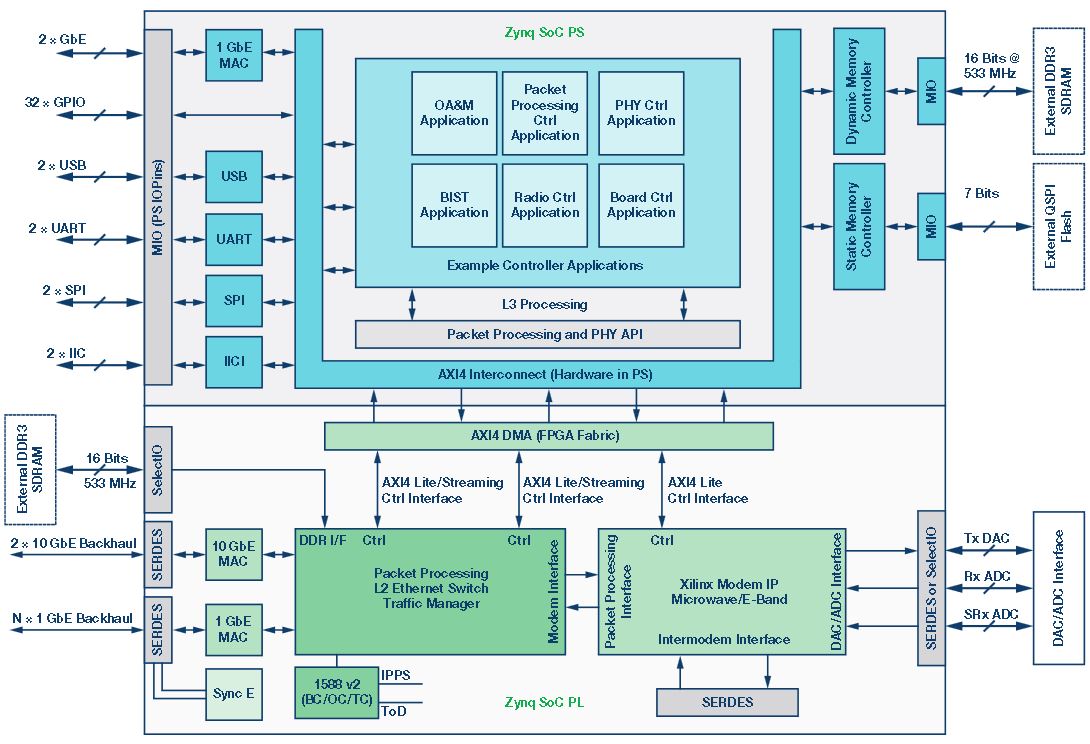

圖2進(jìn)一步詳細(xì)說明了在基于SoC的解決方案中實(shí)現(xiàn)的數(shù)字調(diào)制解調(diào)器。除了可編程邏輯(PL)之外,該平臺(tái)的可擴(kuò)展處理系統(tǒng)(PS)還包含雙ARM ? Cortex ? -A9內(nèi)核,集成內(nèi)存控制器和用于外設(shè)的多標(biāo)準(zhǔn)I / O 。

該SoC平臺(tái)用于執(zhí)行各種數(shù)據(jù)和控制功能并啟用硬件加速。圖2顯示了帶有PHY,控制器,系統(tǒng)接口和數(shù)據(jù)包處理器的集成毫米波調(diào)制解調(diào)器。但是,根據(jù)所需的體系結(jié)構(gòu),您可以插入,更新或刪除不同的模塊。例如,您可以選擇實(shí)施XPIC組合器,以便可以將交叉極化模式的調(diào)制解調(diào)器與另一個(gè)調(diào)制解調(diào)器一起使用。該解決方案在PL中實(shí)現(xiàn),其中SERDES和I / O用于各種數(shù)據(jù)路徑接口,例如調(diào)制解調(diào)器和分組處理器之間的接口,分組處理器和存儲(chǔ)器,或者間接器或DAC / ADC。

< p>調(diào)制解調(diào)器IP的一些其他重要特性包括通過自適應(yīng)編碼和調(diào)制(ACM)實(shí)現(xiàn)自動(dòng)無(wú)中斷和無(wú)差錯(cuò)狀態(tài)切換,以保持鏈路正常運(yùn)行;自適應(yīng)數(shù)字閉環(huán)預(yù)失真(DPD),提高射頻功率放大器的效率和線性度;同步以太網(wǎng)(SyncE)保持時(shí)鐘同步和Reed-Solomon或LDPC前向糾錯(cuò)(FEC)。 FEC的選擇基于設(shè)計(jì)要求。 LDPC FEC是無(wú)線回程應(yīng)用的默認(rèn)選擇,而Reed-Solomon FEC是低延遲應(yīng)用(如前傳)的首選。

LDPC實(shí)現(xiàn)經(jīng)過高度優(yōu)化,利用FPGA并行性進(jìn)行編碼器和解碼器的計(jì)算。結(jié)果是顯著的SNR增益。您可以通過改變LDPC內(nèi)核的迭代次數(shù)來(lái)應(yīng)用不同級(jí)別的并行性,從而優(yōu)化解碼器的大小和功率。您還可以根據(jù)通道帶寬和吞吐量限制對(duì)設(shè)計(jì)進(jìn)行建模。

此調(diào)制解調(diào)器解決方案還帶有用于顯示和調(diào)試的圖形用戶界面(GUI),并且具有高級(jí)功能,如通道帶寬或調(diào)制選擇,以及低級(jí)功能,例如硬件寄存器的設(shè)置。為實(shí)現(xiàn)圖1所示解決方案的3.5 Gbps吞吐量,調(diào)制解調(diào)器IP以440 MHz的時(shí)鐘速率運(yùn)行。它使用五個(gè)千兆位收發(fā)器(GT)作為連接接口,以支持ADC和DAC,以及一些GT用于10 GbE有效載荷或CPRI接口。

毫米波收發(fā)器芯片組

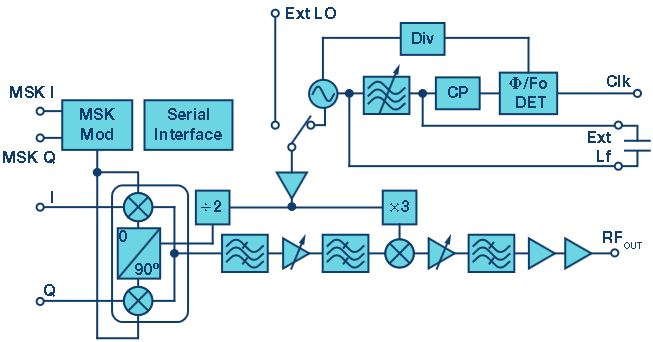

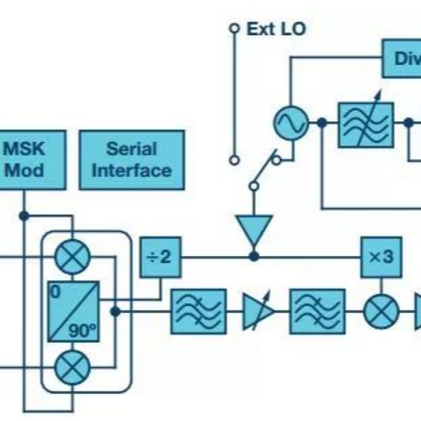

ADI公司針對(duì)小型蜂窩回程應(yīng)用優(yōu)化了該設(shè)計(jì)中使用的第二代硅鍺(SiGe)60 GHz芯片組。發(fā)射器芯片是一個(gè)完整的模擬基帶到毫米波上變頻器。改進(jìn)的頻率合成器以250 MHz的步長(zhǎng)覆蓋57 GHz至66 GHz,具有低相位噪聲,可支持高達(dá)至少64 QAM的調(diào)制。輸出功率已增加至約16 dBm線性功率,而集成功率檢測(cè)器監(jiān)控輸出功率,因此不超過規(guī)定限值。

發(fā)射器芯片提供IF的模擬控制或數(shù)字控制射頻增益。當(dāng)使用更高階調(diào)制時(shí)有時(shí)需要模擬增益控制,因?yàn)殡x散增益變化可能被誤認(rèn)為是幅度調(diào)制,從而導(dǎo)致誤碼。內(nèi)置SPI接口支持?jǐn)?shù)字增益控制。

對(duì)于在窄通道中需要更高階調(diào)制的應(yīng)用,可以將具有更低相位噪聲的外部PLL / VCO注入發(fā)送器,繞過內(nèi)部合成器。

圖3顯示了發(fā)送器芯片的框圖,該芯片支持高達(dá)1.8 GHz的帶寬。 MSK調(diào)制器選項(xiàng)可實(shí)現(xiàn)高達(dá)1.8 Gbps的低成本數(shù)據(jù)傳輸,而無(wú)需昂貴且耗電的DAC。

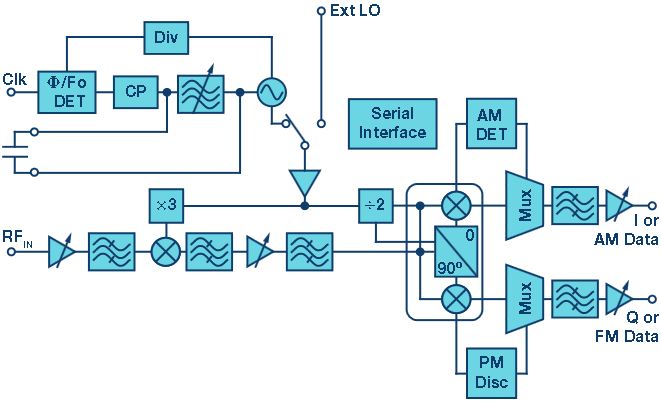

此設(shè)備的補(bǔ)充是一個(gè)接收器芯片,同樣經(jīng)過優(yōu)化以滿足苛刻的要求小型小區(qū)回程應(yīng)用。接收器的輸入P1dB顯著增加到-20 dBm,IIP3顯著增加到-9 dBm,以處理短距離鏈路,其中碟形天線的高增益導(dǎo)致接收器輸入端的高信號(hào)電平。

其他主要功能包括在最大增益設(shè)置下的低6 dB噪聲系數(shù);可調(diào)低通基帶濾波器和高通基帶濾波器;與發(fā)射機(jī)芯片相同的新型合成器,支持57 GHz至66 GHz頻段的64 QAM調(diào)制,以及IF和RF增益的模擬或數(shù)字控制。

接收機(jī)芯片的框圖如圖4所示。注意,接收器還包含AM檢測(cè)器,用于解調(diào)幅度調(diào)制,例如開/關(guān)鍵控(OOK)。此外,F(xiàn)M鑒別器解調(diào)簡(jiǎn)單的FM或MSK調(diào)制。這是用于恢復(fù)QPSK的正交基帶輸出和更復(fù)雜的QAM調(diào)制的I / Q解調(diào)器的補(bǔ)充。

發(fā)射器和接收器均為4 mm×6 mm BGA風(fēng)格,晶圓級(jí)封裝。這些表面貼裝部件可以實(shí)現(xiàn)回程應(yīng)用的低成本無(wú)線電板制造。

圖5顯示了一個(gè)示例毫米波調(diào)制解調(diào)器和無(wú)線電系統(tǒng)的框圖。除了FPGA,調(diào)制解調(diào)器軟件和毫米波芯片組一樣,該設(shè)計(jì)還包含許多其他組件。它們包括雙通道,12位,1 GSPS ADC,四通道16位,高達(dá)2.8 GSPS TxDAC,以及超低抖動(dòng)時(shí)鐘合成器,支持ADC和DAC IC上采用的JESD204B串行數(shù)據(jù)接口。

演示平臺(tái)

圖6中所示的平臺(tái)由Xilinx和ADI公司聯(lián)合創(chuàng)建,用于演示目的。該實(shí)現(xiàn)包括Xilinx開發(fā)板上基于FPGA的調(diào)制解調(diào)器,行業(yè)標(biāo)準(zhǔn)FMC板,包含ADC,DAC,時(shí)鐘芯片和兩個(gè)無(wú)線電模塊評(píng)估板。

演示平臺(tái)包括一臺(tái)用于調(diào)制解調(diào)器控制和可視顯示的筆記本電腦以及一個(gè)可變RF衰減器,用于復(fù)制典型毫米波鏈路的路徑損耗。開發(fā)板上的FPGA執(zhí)行WBM256調(diào)制解調(diào)器固件IP。開發(fā)板上的行業(yè)標(biāo)準(zhǔn)FMC夾層連接器用于連接基帶和毫米波無(wú)線電板。

毫米波模塊卡在基帶板上。這些模塊具有用于60 GHz接口的MMPX連接器以及用于可選使用外部本地振蕩器的SMA連接器。

該平臺(tái)包含演示點(diǎn)對(duì)點(diǎn)回程連接所需的所有硬件和軟件。頻分雙工連接的每個(gè)方向在250 MHz信道中高達(dá)1.1 Gbps。

模塊化和可定制

由于FPGA具有高度模塊化和可定制性,因此FPGA在使用時(shí)可降低成本為無(wú)線回程應(yīng)用構(gòu)建平臺(tái)。在為小型蜂窩回程市場(chǎng)選擇毫米波調(diào)制解調(diào)器解決方案的商用部件時(shí),請(qǐng)選擇高能效的FPGA / SoC和高性能寬帶IP內(nèi)核。在為寬帶通信和交換功能選擇GT時(shí),高速也是需要考慮的因素。尋找可擴(kuò)展以支持多種產(chǎn)品變化的解決方案,從在相同硬件平臺(tái)上以幾百兆比特每秒運(yùn)行到3.5 Gbps的低端小型蜂窩回程產(chǎn)品。

對(duì)于無(wú)線電部分,采用表面貼裝部件封裝的收發(fā)器IC將降低制造成本。市場(chǎng)上的部件將滿足小型蜂窩部署的無(wú)線回程需求的功率,尺寸,靈活性和功能要求。另外還有高性能數(shù)據(jù)轉(zhuǎn)換器和時(shí)鐘管理IC,可用于完成無(wú)線回程鏈路。

-

容量

+關(guān)注

關(guān)注

0文章

117瀏覽量

21458 -

蜂窩技術(shù)

+關(guān)注

關(guān)注

0文章

46瀏覽量

21289

發(fā)布評(píng)論請(qǐng)先 登錄

技術(shù)簡(jiǎn)介:MACOM無(wú)線回程產(chǎn)品組合和解決方案

模擬蜂窩移動(dòng)通信系統(tǒng)的組成及控制

60 GHz回程鏈路的蜂窩容量怎么提升?

小型蜂窩基站面臨的挑戰(zhàn)

TI與Sub10公司推出面向小型蜂窩基站的差異化回程方案

矽映電子借助業(yè)內(nèi)首款單芯片波束導(dǎo)向型60GHZ射頻收發(fā)器進(jìn)軍小蜂窩無(wú)線回傳市場(chǎng)

使用多信道射頻鏈路聚合(LAG)方法提升微波容量

矽映推出單芯片波束導(dǎo)向性60GHz射頻收發(fā)

60 GHz雙向數(shù)據(jù)通信鏈路解決方案,助力蜂窩容量大提升

IWS2013展會(huì):介紹了英飛凌首個(gè)封裝化無(wú)線回程鏈路解決方案

小型蜂窩的無(wú)線回程容量解決方案

60GHz視距回程鏈路隨時(shí)可提高蜂窩容量

60 GHz視線回程鏈路準(zhǔn)備提升蜂窩容量

60 GHz視線回程鏈路準(zhǔn)備提升蜂窩容量

評(píng)論