摘要:針對(duì)E2V公司的高速ADC芯片EV10AQ190,提出了一種高速ADC接口電路設(shè)計(jì)方案。首先簡(jiǎn)要介紹了高速ADC芯片EV10AQ190技術(shù)特點(diǎn),然后重點(diǎn)敘述了影響高速ADC接口電路性能的兩大關(guān)鍵技術(shù):FPGA片同步技術(shù)和多路ADC校正技術(shù),最后給出了硬件調(diào)試及實(shí)驗(yàn)結(jié)果。實(shí)驗(yàn)結(jié)果表明,該高速ADC接口電路采樣率可穩(wěn)定工作在4GHz以上。這種方案已成功應(yīng)用到某寬帶雷達(dá)回波模擬系統(tǒng)的設(shè)計(jì)中。

隨著電子通信行業(yè)的高速發(fā)展,越來越多的應(yīng)用都要求更高的速率和更大的帶寬,高速模數(shù)轉(zhuǎn)換(ADC)芯片的采樣率已經(jīng)從以前的MHz級(jí)發(fā)展到當(dāng)前的GHz級(jí)。伴隨著信號(hào)采樣率的不斷提高,信號(hào)偏斜(SKEW)、抖動(dòng)和噪聲都在吞噬著時(shí)序余量,如何在高速系統(tǒng)中進(jìn)行穩(wěn)定、可靠的采樣和數(shù)據(jù)變換將面臨極大的挑戰(zhàn)。

高速ADC電路設(shè)計(jì)一直是電子通信領(lǐng)域的研究熱點(diǎn)。

文獻(xiàn)[1]給出了一種基于FPGA片同步技術(shù)的高速ADC接口電路設(shè)計(jì)方法。

文獻(xiàn)[5]利用E2V公司ADC芯片EV8AQ160實(shí)現(xiàn)了雙通道2.5Gsample/s信號(hào)的采集。

文獻(xiàn)[6]介紹了利用FPGA通過SPI協(xié)議對(duì)ADC芯片ADC083000進(jìn)行配置的方法,實(shí)現(xiàn)了3Gsample/s數(shù)據(jù)采樣。

文獻(xiàn)[7-8]講述了如何利用FPGA來設(shè)計(jì)多通道高速ADC采樣控制器。

文獻(xiàn)[9-10]分別介紹了高速ADC電路的設(shè)計(jì)方法和PCB設(shè)計(jì)要點(diǎn)。

公司ADC芯片EV10AQ190實(shí)現(xiàn)了一種高速ADC接口電路,信號(hào)采樣率高達(dá)4Gsample/s。EV10AQ190是E2V公司的一款高速ADC芯片,具有10bit分辨率,最高采樣率可達(dá)5GHz。在如此高速的ADC接口設(shè)計(jì)中,時(shí)鐘和數(shù)據(jù)穩(wěn)定的相位關(guān)系、同步性能的好壞將直接影響信號(hào)采集的質(zhì)量,必須采用源同步技術(shù),保證采樣時(shí)鐘和數(shù)據(jù)嚴(yán)格同步、時(shí)序關(guān)系穩(wěn)定。此外,對(duì)于高速ADC芯片EV10AQ190,內(nèi)部集成了多路ADC,通過采用多通道ADC交錯(cuò)采樣拼接技術(shù)來獲得更高采集變換速率。因此,多個(gè)通道ADC輸出幅度、相位、直流偏置是否一致將直接影響采樣拼接后的高速ADC輸出信號(hào)質(zhì)量,高速ADC接口電路設(shè)計(jì)時(shí)必須對(duì)EV10AQ190芯片內(nèi)部4路ADC進(jìn)行幅相一致性校正。

本文提出了一種基于片同步(CHIPSYNC)技術(shù)的高速ADC接口電路設(shè)計(jì)方案,利用XILINX公司Virtex-6系列FPGA完成了高速ADC接口設(shè)計(jì),實(shí)現(xiàn)了采樣時(shí)鐘和數(shù)據(jù)的動(dòng)態(tài)相位調(diào)整,確保了高速ADC的穩(wěn)定、可靠工作。同時(shí),采用了多路校正技

術(shù)對(duì)芯片EV10AQ190內(nèi)部4路ADC的偏置(Offset)、增益(Gain)、相位(Phase)進(jìn)行校正,保證多通道ADC輸出的幅相一致性,確保高速ADC的動(dòng)態(tài)性能指標(biāo)滿足設(shè)計(jì)要求。

1 高速ADC 器件EV10AQ190EV10AQ190是E2V公司的一款低功耗、高性能模數(shù)轉(zhuǎn)換芯片,片內(nèi)集成了4路1.25GHz采樣率、10bit分辨率ADC,輸出為L(zhǎng)VDS標(biāo)準(zhǔn)電平,可以工作在單通道、雙通道、四通道3種模式,最高采樣率可達(dá)5GHz。EV10AQ190內(nèi)部集成了1∶1和1∶2的數(shù)據(jù)多路分離器(DMUX)和LVDS輸出緩沖器,可以降低輸出數(shù)據(jù)率,方便與多種類型的高速FPGA直接相連,實(shí)現(xiàn)高速率的數(shù)據(jù)存儲(chǔ)和處理。為了補(bǔ)償由于器件參數(shù)離散和傳輸路徑差異所造成的采樣數(shù)據(jù)誤差,該ADC具有針對(duì)每路ADC數(shù)據(jù)的增益、偏置、相位的控制和校正。EV10AQ190提供測(cè)試和自檢功能,方便用戶根據(jù)自己的習(xí)慣對(duì)ADC是否正常工作進(jìn)行測(cè)試和對(duì)時(shí)序是否對(duì)齊進(jìn)行調(diào)試。

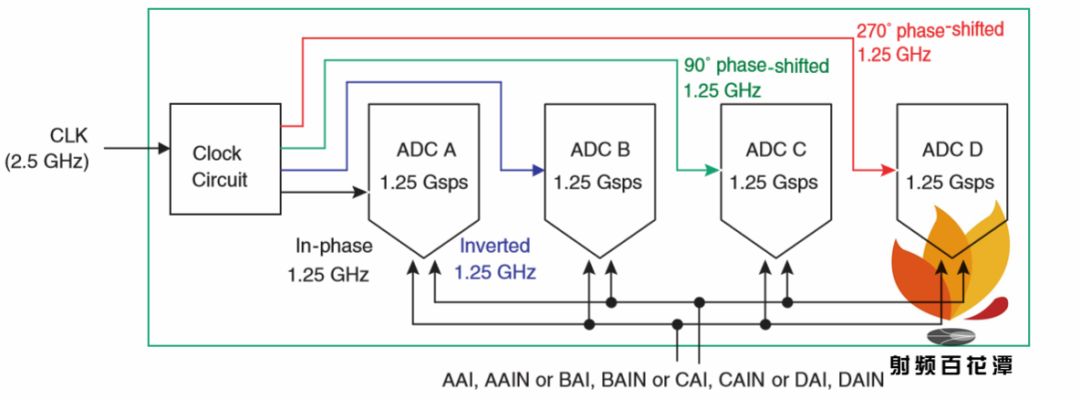

EV10AQ190可以工作在3種模式下,分別是采樣率為1.25GHz的四通道模式,采樣率為2.5GHz的雙通道模式以及采樣率為5GHz的單通道模式。EV10AQ190的所有控制參數(shù),包括通道選擇、旁路模式、編碼格式、輸出多路分離器、積分非線性校正、偏置校正、增益校正、相位校正等,均可通過SPI串行控制端口對(duì)相應(yīng)的控制寄存器進(jìn)行設(shè)置。本文中,EV10AQ190配置工作在單通道模式,如圖1所示。

圖1 單通道模式時(shí)鐘驅(qū)動(dòng)( 模擬信號(hào)由AAI /AAIN 輸入)

外部模擬信號(hào)通過一個(gè)射頻轉(zhuǎn)換器將單端信號(hào)轉(zhuǎn)換成差分信號(hào),可選擇A、B、C、D任一通道輸入,輸入信號(hào)在內(nèi)部同其他3路ADC連通,且4路ADC時(shí)鐘均由同一外部時(shí)鐘驅(qū)動(dòng),即4路ADC共用時(shí)鐘電路。在單通道模式下,外部輸入2.5GHz時(shí)鐘,該時(shí)鐘會(huì)被2分頻為1.25GHz,以驅(qū)動(dòng)內(nèi)部采樣時(shí)鐘。同相的1.25GHz時(shí)鐘驅(qū)動(dòng)A路ADC,同時(shí)反相的1.25GHz時(shí)鐘驅(qū)動(dòng)B路ADC,同相的1.25GHz時(shí)鐘經(jīng)過90°延時(shí)后驅(qū)動(dòng)C路ADC,反相的1.25GHz時(shí)鐘經(jīng)過90°延時(shí)后驅(qū)動(dòng)D路ADC,在此交錯(cuò)拼接模式下將得到最高5GHz的等效采樣率。

2 高速ADC 接口設(shè)計(jì)中的關(guān)鍵技術(shù)2. 1 基于片同步技術(shù)的高速ADC 接口片同步(CHIPSYNC)是XILINX公司命名的一種同步技術(shù),其本質(zhì)是一種源同步技術(shù),目的是為FPGA提供一個(gè)高速的源同步數(shù)據(jù)總線接口。它是XILINX公司在Virtex-4及之后系列FPGA上采用的一種技術(shù),XILINXFPGA內(nèi)部具有若干全局時(shí)鐘緩沖器(BUFG)和區(qū)域時(shí)鐘緩沖器(BUFR),特別適合做源同步接口。FPGA片內(nèi)每個(gè)I/O管腳中集成了一個(gè)64階的可編程調(diào)節(jié)信號(hào)延遲的延時(shí)模塊(IODELAY),可精確控制信號(hào)延時(shí)實(shí)現(xiàn)采樣時(shí)鐘和數(shù)據(jù)相位的動(dòng)態(tài)調(diào)整,從而確定信號(hào)采集的最佳采樣點(diǎn),實(shí)現(xiàn)高速ADC接口的可靠、穩(wěn)定工作。

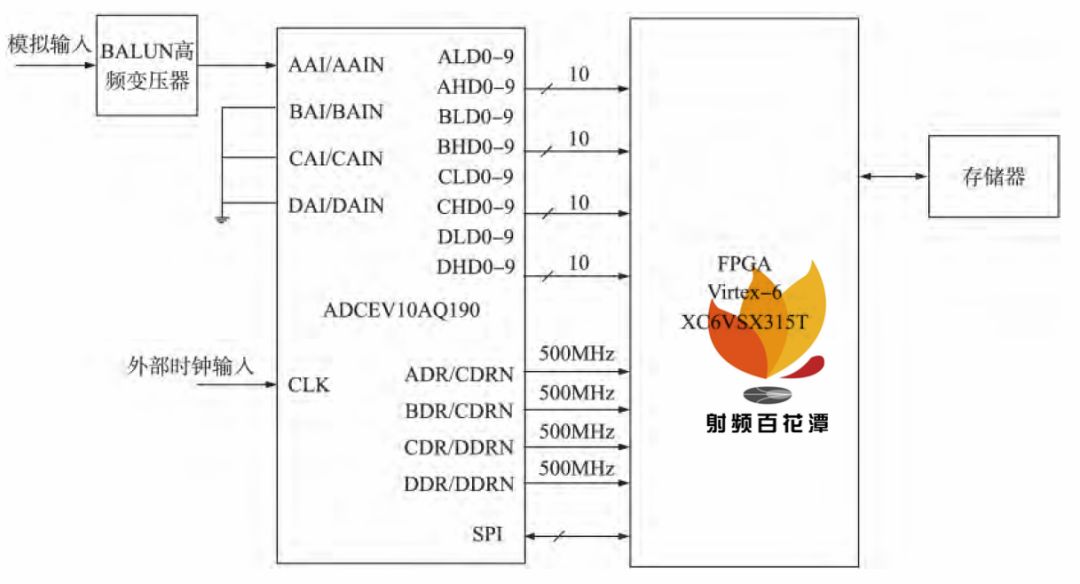

圖2 4. 0GHz 采樣高速ADC 接口電路原理框圖

圖2為基于片同步技術(shù)的4GHz采樣高速ADC接口電路原理框圖,主要包括高速ADC和高性能FPGA接口處理2部分。

模擬輸入信號(hào)經(jīng)過巴倫(BALUN)變壓器完成單端信號(hào)到差分信號(hào)的轉(zhuǎn)換,然后輸入到高速ADC芯片EV10AQ190的模擬輸入端。利用XILINX公司高性能Virtex-6系列FPGA芯片XC6VSX315T中的40對(duì)LVDS管腳接收來自EV10AQ190的4路10bit1000Mbit/s的輸出數(shù)據(jù),并用4個(gè)LVDS專用時(shí)鐘輸入通道接收4路ADC輸出的500MHz同步采樣時(shí)鐘(DDR輸出,采樣時(shí)鐘為數(shù)據(jù)速率的一半)。FPGA接收到的4路1000Mbit/s高速數(shù)據(jù)后,經(jīng)過內(nèi)部1:4串并轉(zhuǎn)換模塊(ISERDES)后,變成16路并行10bit數(shù)據(jù),速度降為250Mbit/s,便于FPGA內(nèi)部處理并和低速的外部存儲(chǔ)器相連。

2. 1. 1 高速ADC

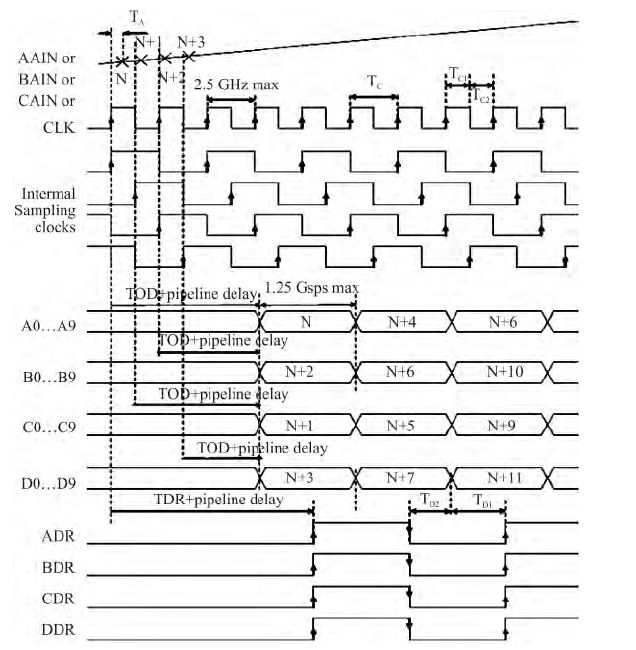

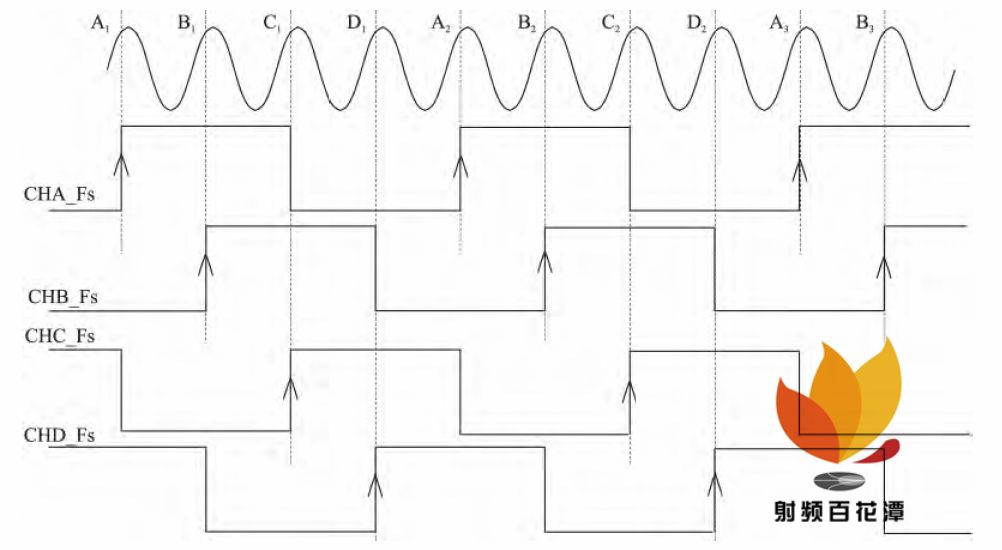

EV10AQ190工作在單通道模式下,模擬信號(hào)從ADC的A通道輸入,且DMUX=1:1輸出模式,此時(shí)ADC工作時(shí)序如圖3所示。

圖3EV10AQ190單通道模式1:1DMUX模式的工作時(shí)序

圖3中,芯片A端口上的模擬輸入將會(huì)在AHD0~AHD9、BHD0~BHD9、CHD0~CHD9和DHD0~DHD9上以交錯(cuò)方式輸出。本文中,信號(hào)采樣率為4GHz,輸入芯片時(shí)鐘頻率為2GHz,內(nèi)部4路ADC采樣時(shí)鐘為輸入時(shí)鐘頻率的一半,即內(nèi)部4路ADC以1GHz進(jìn)行采樣。ADC變換數(shù)據(jù)以DDR方式輸出,輸出1000Mbit/s速率數(shù)據(jù)的同時(shí)輸出500MHz同步采樣時(shí)鐘,輸出數(shù)據(jù)位寬為4×10=40對(duì)LVDS信號(hào)。

2. 1. 2 ADC 與FPGA 數(shù)據(jù)接口本文采用了XILINX公司Virtex-6系列FPGA(XC6VSX315T)來實(shí)現(xiàn)高速ADC接口。ADC芯片EV10AQ190輸出的數(shù)據(jù)和同步時(shí)鐘送到FPGA芯片XC6VSX315T中,Virtex-6系列FPGA具有多個(gè)專用LVDS差分邏輯接收通道,發(fā)送數(shù)據(jù)速率高達(dá)1.25Gbit/s,接收數(shù)據(jù)速率也高達(dá)1Gbit/s,能夠滿足EV10AQ190輸出數(shù)據(jù)和控制邏輯的要求。Virtex-6系列FPGA的每個(gè)I/O管腳都采用了CHIPSYNC技術(shù)[3],在其I/O管腳中嵌入了一個(gè)64階的可編程調(diào)節(jié)信號(hào)延遲的延時(shí)模塊IODELAY,對(duì)于200MHz延時(shí)時(shí)鐘(周期為5ns)輸入,可調(diào)節(jié)的最小延時(shí)為5ns/64=78.15ps。這樣,可以精確地獨(dú)立調(diào)整每根數(shù)據(jù)線的延遲,甚至可以通過設(shè)置一些控制信號(hào)在程序運(yùn)行過程中改變信號(hào)的延遲,使鎖存時(shí)鐘可以精確地對(duì)準(zhǔn)每根數(shù)據(jù)線數(shù)據(jù)有效窗口的中心,保證高速數(shù)據(jù)采集時(shí)整個(gè)數(shù)據(jù)總線的所有數(shù)據(jù)能夠可靠地鎖存。

FPGA內(nèi)部數(shù)據(jù)和時(shí)鐘接收處理框圖如圖4所示,ADC數(shù)據(jù)和ADC時(shí)鐘信號(hào)通過專用差分?jǐn)?shù)據(jù)接口IBUFDS和IBUFGDS進(jìn)入FPGA內(nèi)部,經(jīng)精確延時(shí)模塊IODELAY進(jìn)行相位動(dòng)態(tài)調(diào)整,再經(jīng)過輸入串并變換模塊ISERDES作1:4串并轉(zhuǎn)換,完成高速ADC數(shù)據(jù)的接收。

圖4 FPGA 內(nèi)部數(shù)據(jù)和時(shí)鐘接收框圖

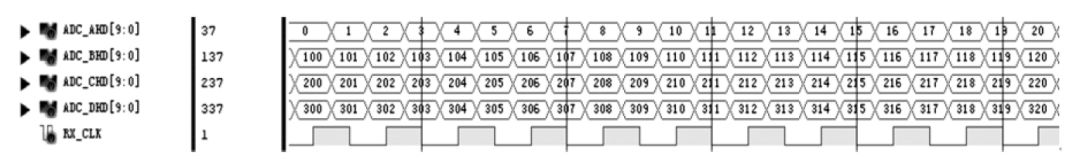

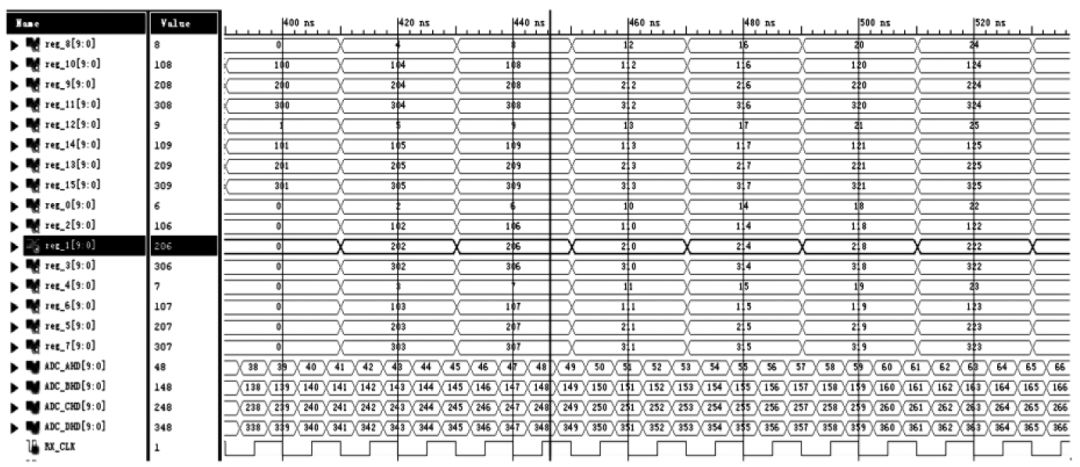

FPGA內(nèi)部數(shù)據(jù)和時(shí)鐘接收功能采用VERILOG語(yǔ)言編程,設(shè)計(jì)中利用XILINX仿真軟件ISim對(duì)該程序進(jìn)行了功能仿真。定義輸入的仿真激勵(lì)信號(hào)為4路10bit數(shù)據(jù)和時(shí)鐘,分別命名為ADC_AHD[9:0]、ADC_BHD[9:0]、ADC_CHD[9:0]、ADC_DHD[9:0]和RX_CLK,用來模擬ADC芯片EV10AQ190輸出的4路DDR方式的采樣數(shù)據(jù)和時(shí)鐘。其中,ADC_AHD為0~99循環(huán)計(jì)數(shù),ADC_BHD為100~199循環(huán)計(jì)數(shù),ADC_CHD為200~299循環(huán)計(jì)數(shù),ADC_DHD為300~399循環(huán)計(jì)數(shù),如圖5所示。

圖5 FPGA 內(nèi)部時(shí)序仿真激勵(lì)信號(hào)

FPGA內(nèi)部時(shí)序仿真結(jié)果如圖6所示。圖6中,reg0~15[9:0]為FPGA輸出的經(jīng)過1:4串并轉(zhuǎn)換(ISERDES)后的16路10bit數(shù)據(jù)。從圖中可以看出,來自ADC芯片的4路高速串行數(shù)據(jù)變?yōu)?6路較低速的并行數(shù)據(jù),信號(hào)速率降為原來的1/4,并且輸出數(shù)據(jù)相對(duì)輸入數(shù)據(jù)具有十多個(gè)時(shí)鐘周期的延時(shí),時(shí)序嚴(yán)格同步,驗(yàn)證FPGA內(nèi)部數(shù)據(jù)和時(shí)鐘接收處理程序的正確性。

圖6 FPGA 內(nèi)部時(shí)序仿真結(jié)果

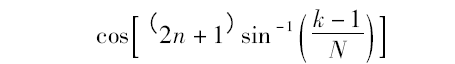

2. 2 QDR 存儲(chǔ)電路設(shè)計(jì)高速ADC 采集變換輸出數(shù)據(jù)經(jīng)過FPGA 進(jìn)行串并轉(zhuǎn)換降速處理、存儲(chǔ)器接口控制后可外接DDR( 雙倍數(shù)據(jù)速率) 或QDR( 四倍數(shù)據(jù)速率) 存儲(chǔ)器中進(jìn)行緩存,本文高速ADC 接口電路用于寬帶雷達(dá)回波模擬系統(tǒng),F(xiàn)PGA 外接存儲(chǔ)器為QDR SRAM 存儲(chǔ)器,用來實(shí)現(xiàn)對(duì)雷達(dá)發(fā)射信號(hào)的存儲(chǔ)轉(zhuǎn)發(fā)。

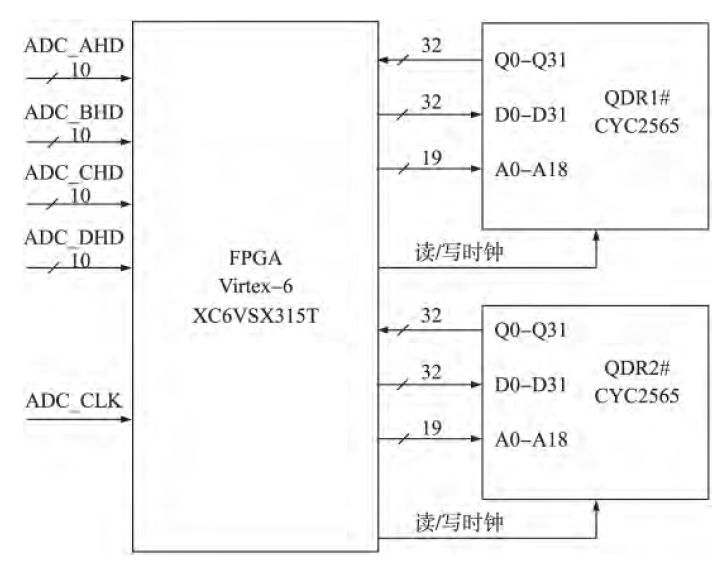

本文使用了CYPRESS公司的2片QDRSRAM存儲(chǔ)器CY7C2565KV18,F(xiàn)PGA和QDR存儲(chǔ)器之間的接口電路如圖7所示。

圖7 QDR 存儲(chǔ)器接口電路原理框圖

ADC芯片EV10AQ190輸出的4路10bit高速數(shù)據(jù)經(jīng)過FPGA進(jìn)行1:4串并變換后變?yōu)?6路10bit數(shù)據(jù),速率降為原來的1/4,便于和低速的QDR存儲(chǔ)器接口。再經(jīng)過FPGA內(nèi)部QDR讀寫控制器(XILINXFPGA內(nèi)部專用的IPCore)后送到2片QDR存儲(chǔ)器CY7C2565KV18中進(jìn)行暫存。

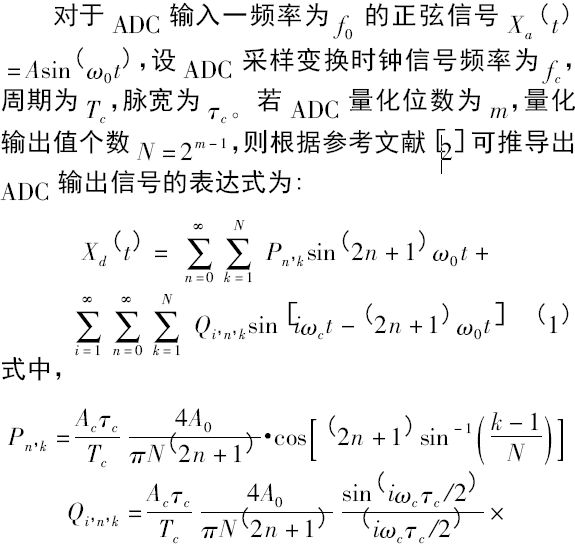

2. 3 多路ADC 校正技術(shù)2. 3. 1 ADC 輸出信號(hào)的雜散電平[2, 11]

從式(1)可以看出,ADC輸出信號(hào)頻率成分包括2部分:有用信號(hào)ω0和ω0的各次諧波分量(式(1)中的第一項(xiàng))以及有用信號(hào)與采樣時(shí)鐘信號(hào)間的各次交調(diào)分量(式(1)中的第2項(xiàng))。有用信號(hào)(ω0)的諧波分量可通過ADC之后的低通濾波器濾除,而有用信號(hào)和采樣時(shí)鐘間的某些交調(diào)分量,如ωc-ω0、ω0-ωc、2ωc-ω0頻率成分,會(huì)落在低通濾波器通帶內(nèi),無法濾除,影響ADC輸出信號(hào)無雜散動(dòng)態(tài)范圍(SFDR)。因此,要提高ADC動(dòng)態(tài)性能,必須盡量減小有用信號(hào)和采樣時(shí)鐘間的交調(diào)分量。

2. 3. 2 EV10AQ190 中多路ADC 校正方法

EV10AQ190芯片內(nèi)部包含4個(gè)1.25GHz采樣率的ADC,通過交錯(cuò)采樣拼接技術(shù)實(shí)現(xiàn)單通道最高5GHz采樣率。因此,要保證單通道模式下ADC輸出信號(hào)質(zhì)量,減小ADC輸出信號(hào)雜散電平,必須確保內(nèi)部4路ADC的幅度相同,相位上嚴(yán)格相差90°,即需要對(duì)EV10AQ190芯片內(nèi)部4路ADC的直流偏置、增益、相位參數(shù)值進(jìn)行校正,可通過內(nèi)部SPI串行控制端口對(duì)相應(yīng)的控制寄存器進(jìn)行設(shè)置來完成。

EV10AQ190芯片工作在單通道模式下,若輸入芯片時(shí)鐘為fc,則內(nèi)部4路ADC采樣率為fc/2,等效采樣率為2fc。輸入信號(hào)頻率為fin。根據(jù)2.3.1分析結(jié)果,影響ADC輸出信號(hào)SFDR性能的是有用信號(hào)和采樣時(shí)鐘間的某些交調(diào)分量,如fc-fin、fc/2-fin和fin-fc/2等均有可能落在低通濾波器通帶內(nèi),必須盡量抑制。通過幅相一致性校正技術(shù)可有效減小這些交調(diào)分量的大小。

EV10AQ190芯片內(nèi)部多路ADC校正應(yīng)注意兩點(diǎn):一是校正順序是先校偏置,再校增益,最后校相位;二是校正時(shí)選擇輸入模擬信號(hào)頻率應(yīng)選ADC最大頻率點(diǎn)。對(duì)于5GHz采樣,每路ADC采樣率為1.25GHz,故可選擇輸入校正信號(hào)頻率點(diǎn)為600.59MHz。

(1)偏置校正(OffsetCalibration)多通道ADC直流偏置不同將會(huì)影響輸出信號(hào)雜散分量中fc/2頻率信號(hào)電平大小,從而影響高速ADC的動(dòng)態(tài)性能。由于ADC的偏置對(duì)增益和相位都有影響,因此首先應(yīng)對(duì)偏置進(jìn)行校正。EV10AQ190輸出為10bit無符號(hào)數(shù),最大輸出值是1023,故直流偏置理論上應(yīng)該為511。偏置的校正方法如下:ADC無信號(hào)輸入的情況下,記錄ADC輸出數(shù)據(jù),計(jì)算4個(gè)通道ADC輸出數(shù)據(jù)的平均值,看平均值是否是511,如果是511說明偏置已經(jīng)校好,如果不是,則通過SPI串口控制EV10AQ190的偏置控制寄存器來調(diào)整ADC偏置,調(diào)整完成,記錄并設(shè)置好4個(gè)通道偏置控制寄存器的值。

( 2) 增益校正( Gain Calibration)多通道ADC增益不同將會(huì)影響輸出信號(hào)雜散分量中fc-fin,fc/2-fin和fin-fc/2頻率信號(hào)電平大小,即影響輸入信號(hào)的鏡像頻率成分,從而影響ADC的動(dòng)態(tài)性能。對(duì)增益的校正需要保證偏置已經(jīng)校正完成。增益的校正方法如下:ADC輸入一個(gè)正弦信號(hào),推薦頻率為600.59MHz,幅度為500mV,記錄下4個(gè)通道的采集數(shù)據(jù)并做FFT變換,比較4個(gè)通道采集數(shù)據(jù)頻譜的幅度是否相同。如果不同,以一個(gè)通道為標(biāo)準(zhǔn),通過控制EV10AQ190的增益控制寄存器調(diào)整其他3個(gè)通道的增益,調(diào)整完成,記錄并設(shè)置好增益控制寄存器的值。增益校正過程要求輸入正弦信號(hào)和采樣時(shí)鐘信號(hào)要嚴(yán)格同源。( 3) 相位校正( Phase Calibration)多通道ADC相位不校準(zhǔn)會(huì)影響輸出信號(hào)雜散分量中fc-fin,fc/2-fin和fin-fc/2頻率信號(hào)電平大小,即影響輸入信號(hào)的鏡像頻率成分,從而影響ADC的動(dòng)態(tài)性能。

相位校正前應(yīng)保證偏置和增益校正已完成。相位校正過程要求EV10AQ190輸入模擬信號(hào)頻率是輸入時(shí)鐘的2倍,是內(nèi)部4通道ADC采樣率的4倍。對(duì)于EV10AQ190工作在單通道5GHz采樣模式下,輸入時(shí)鐘頻率為2.5GHz,內(nèi)部每路ADC采樣率為1.25GHz,則將ADC的輸入模擬信號(hào)頻率設(shè)置為5GHz。如果EV10AQ190內(nèi)部4路ADC相位嚴(yán)格相差90°,由于輸入信號(hào)頻率是內(nèi)部ADC采樣時(shí)鐘頻率的4倍,則4個(gè)通道采集變換輸出信號(hào)幅度相等,4路ADC輸出將在一條直線上,如圖8所示。因此,相位校正時(shí)可以通過設(shè)置EV10AQ190的相位控制寄存器來調(diào)整A、B、C、D4個(gè)通道采樣時(shí)鐘的相位,使得4路輸出信號(hào)值(Ai、Bi、Ci、Di,i=1,2

,3,…)盡量相等。

圖8 ADC 相位校正原理

相位校正方法如下:ADC輸入一正弦信號(hào),頻率是輸入采樣時(shí)鐘的2倍。記錄4個(gè)通道ADC輸出數(shù)據(jù),如果4路ADC輸出數(shù)據(jù)相同,說明相位校正完成。如果不同,則以一個(gè)通道為基準(zhǔn),通過控制EV10AQ190的相位控制寄存器調(diào)整其他3個(gè)通道的相位,使得4個(gè)通道ADC輸出值相同。相位校正過程要求輸入正弦信號(hào)和采樣時(shí)鐘信號(hào)要嚴(yán)格同源。

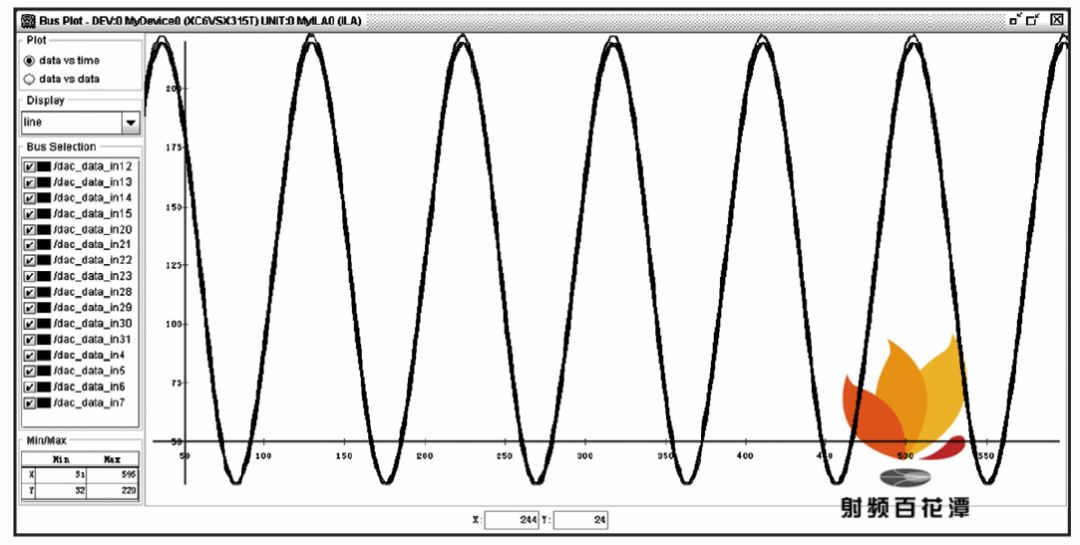

3 實(shí)驗(yàn)與結(jié)果高速ADC接口程序在XILINX公司的ISE軟件中經(jīng)過邏輯綜合、布局布線、目標(biāo)代碼生成等過程,最終用高性能FPGA芯片XC6VSX315T實(shí)現(xiàn),并下載到高速ADC接口電路板上的FPGA進(jìn)行了實(shí)驗(yàn)驗(yàn)證。實(shí)驗(yàn)過程設(shè)計(jì)如下:首先由信號(hào)源產(chǎn)生一點(diǎn)頻信號(hào),頻率為500MHz,輸入采樣時(shí)鐘為2GHz,高速ADC采樣率為4GHz。500MHz點(diǎn)頻信號(hào)經(jīng)過高速ADC芯片后變?yōu)?路并行的數(shù)字信號(hào),數(shù)據(jù)速率為1000Mbit/s,進(jìn)入FPGA芯片。然后在XILINX公司ChipScopeAnalyzer軟件中采集觀測(cè)高速ADC信號(hào)經(jīng)過1:4串并變換后的數(shù)據(jù),得到了16路10bit穩(wěn)定的數(shù)據(jù),并用總線(bus)波形圖方式顯示,如圖9所示:

圖9 FPGA 內(nèi)部采集的ADC 輸出信號(hào)

圖9表明,用頻率為4GHz的采樣時(shí)鐘對(duì)頻率為500MHz的正弦信號(hào)進(jìn)行采樣所得到的高速數(shù)據(jù)經(jīng)過本文設(shè)計(jì)的高速ADC接口電路處理后得到了完美的正弦信號(hào)數(shù)據(jù),從而證明了高速ADC接口電路的正確性和有效性。

另外,為測(cè)試多路校正技術(shù)對(duì)高速ADC接口電路性能影響效果,本文對(duì)校正前和校正后ADC輸出信號(hào)的無雜散動(dòng)態(tài)范圍(SFDR)進(jìn)行了測(cè)試。測(cè)試結(jié)果為:幅相一致性校正前輸出信號(hào)SFDR為35dBc,校正后輸出信號(hào)SFDR能夠達(dá)到42dBc,提高

了約7dBc。可見,多路校正技術(shù)對(duì)于改善高速ADC動(dòng)態(tài)性能是十分明顯的。

4 結(jié)論

本文針對(duì)E2V公司的高速ADC芯片EV10AQ190,介紹了一種高速ADC接口電路設(shè)計(jì)方案。通過采用FPGA片同步技術(shù)和多路ADC校正技術(shù),解決了高速電路中數(shù)據(jù)與時(shí)鐘的時(shí)序同步以及多通道ADC幅相一致性校正問題,確保了高速ADC的動(dòng)態(tài)性能和可靠性。文章最后給出了硬件調(diào)試結(jié)果。

實(shí)驗(yàn)結(jié)果表明,通過校正EV10AQ190芯片內(nèi)部4路ADC的偏置、增益、相位并采用FPGA片同步技術(shù),該高速ADC接口電路采樣率可達(dá)4GHz以上,雜散優(yōu)于42dBc,高速ADC輸出數(shù)據(jù)能夠穩(wěn)定、可靠的鎖存到FPGA內(nèi)部。該接口電路方案已成功應(yīng)用到某寬帶雷達(dá)回波模擬系統(tǒng)高速信號(hào)采集的設(shè)計(jì)中。

-

接口電路

+關(guān)注

關(guān)注

8文章

469瀏覽量

57674 -

adc

+關(guān)注

關(guān)注

99文章

6688瀏覽量

549084 -

模擬系統(tǒng)

+關(guān)注

關(guān)注

0文章

59瀏覽量

13838

原文標(biāo)題:基于E2V的高速ADC接口設(shè)計(jì)

文章出處:【微信號(hào):gh_f97d2589983b,微信公眾號(hào):高速射頻百花潭】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

一種低功耗以太網(wǎng)接口電路的設(shè)計(jì)方案

求一種采用數(shù)字控制的三相移相觸發(fā)電路設(shè)計(jì)方案?

分享一種基于IR2llO芯片的高頻感應(yīng)加熱電源驅(qū)動(dòng)電路設(shè)計(jì)方案

一種新的低功耗CMOS三值電路設(shè)計(jì)

基于FPGA技術(shù)的RS232接口時(shí)序電路設(shè)計(jì)方案

AC24V接口EMC標(biāo)準(zhǔn)電路設(shè)計(jì)方案

AV接口EMC標(biāo)準(zhǔn)電路設(shè)計(jì)方案

CAN總線接口EMC標(biāo)準(zhǔn)電路設(shè)計(jì)方案

高速ADC電源設(shè)計(jì)方案

一種推挽逆變車載開關(guān)電源電路設(shè)計(jì)方案

基于PC機(jī)USB接口充電電路設(shè)計(jì)方案

一種高速ADC接口電路設(shè)計(jì)方案

一種高速ADC接口電路設(shè)計(jì)方案

評(píng)論