DDR4新增了許多功能,這對于我們之前信手拈來的內存PCB設計又帶來了一些新的挑戰,雖然說之前的一些規范可以用,但還是有很多不一樣的地方,如果依然按照之前的設計方法來做,說明你還不了解DDR4,一準入坑。今天咱們就來扒一扒它的新功能和PCB設計上的一些注意事項。

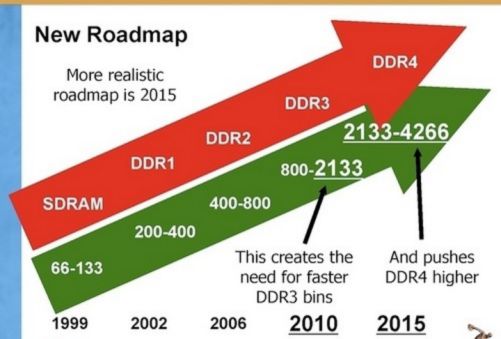

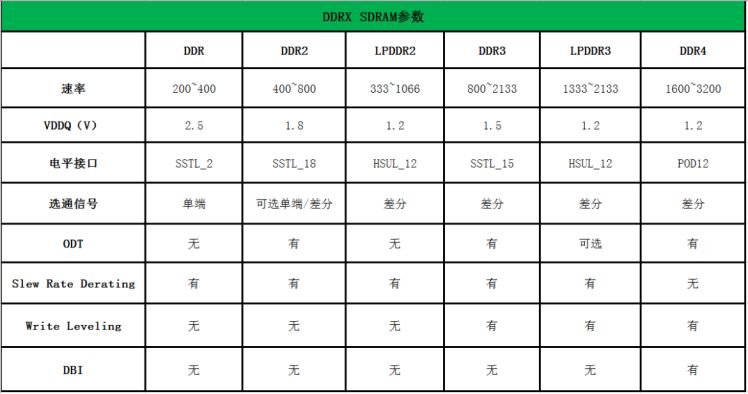

DDRX發展趨勢及參數對比

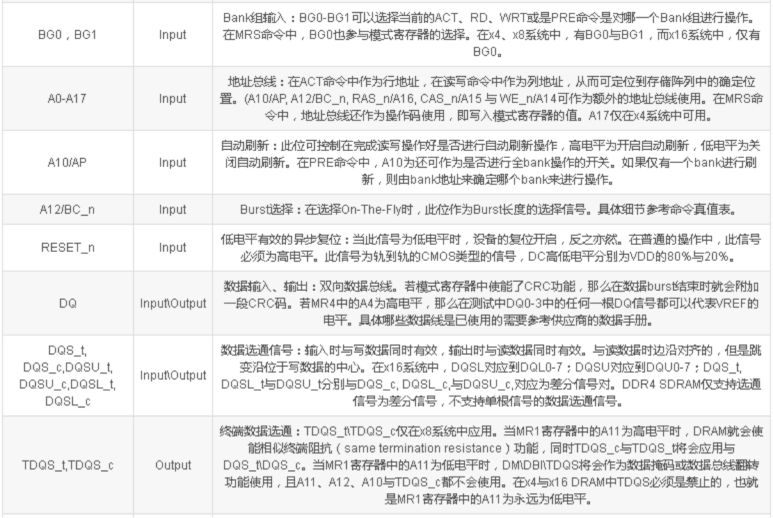

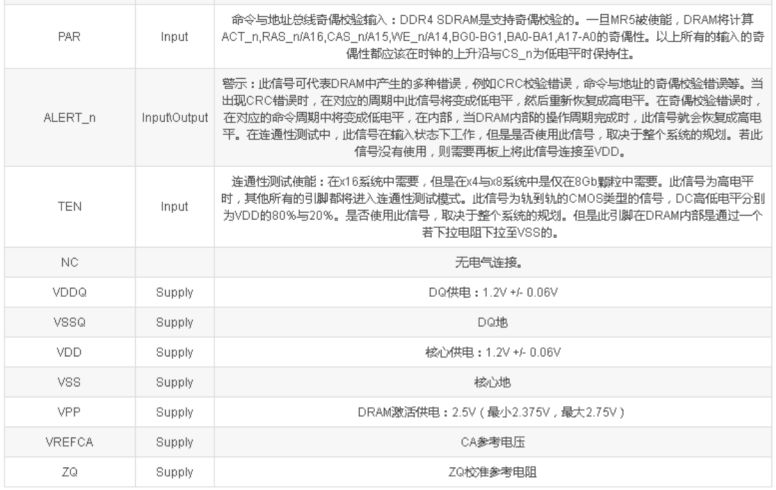

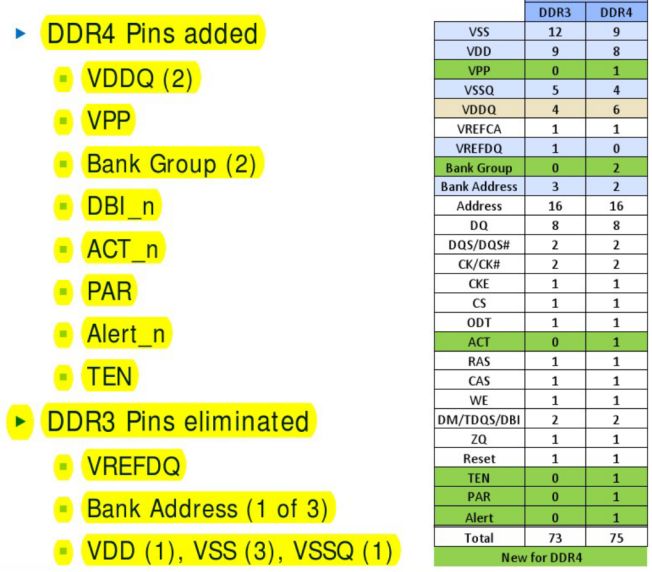

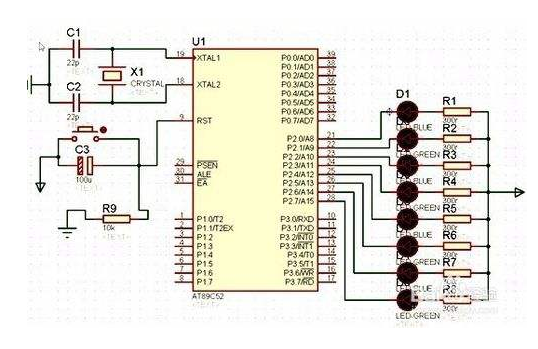

DDR4信號引腳功能

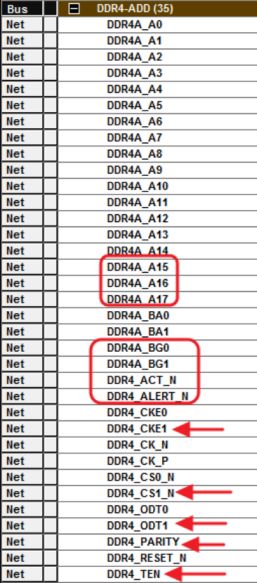

DDR4新增pin

DDR4新增功能

(1)新的JEDEC POD12接口標準(工作電壓1.2V) ;

(2)DBI:可以降低功耗并且提升數據信號完整性;

(3)Bank群組結構:是個8n預取群組結構,它可以使用兩個或者四個Bank組,這允許DDR4內存在每個Bank群組單獨被激活、讀取、寫入或刷新操作,這樣可以帶來更高的內存速度和帶寬;

(5)DQ動態確定Vref ( V_ center ) ,增加了眼圖要求;

(5)新的終止調度:在DDR4中DQbus可以轉移終止到VDDQ,這樣即使VDD電壓降低的情況下也能保證穩定;

(6)新的數據總線CRC技術,可以進行傳輸過程中的錯誤偵測,特別對非ECC內存進行寫入操作時有幫助;

(7)針對命令和地址總線的新的CA奇偶校驗;突發長度和突發停止長度分別為8和4 ;

(8)正常和動態的ODT:改進ODT協議,并且采用新的ParkMode模式可以允許正常終結和動態吸入終結,而不需要去驅動ODTPin

(9)Differential Signaling(差分信號技術)

信號分組

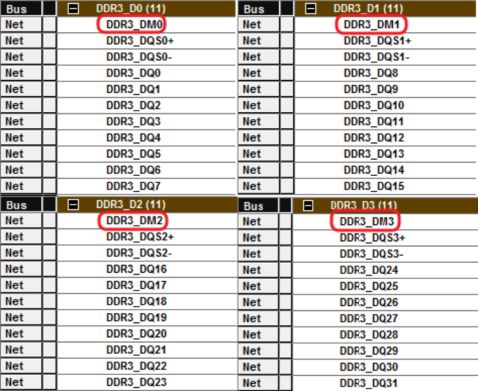

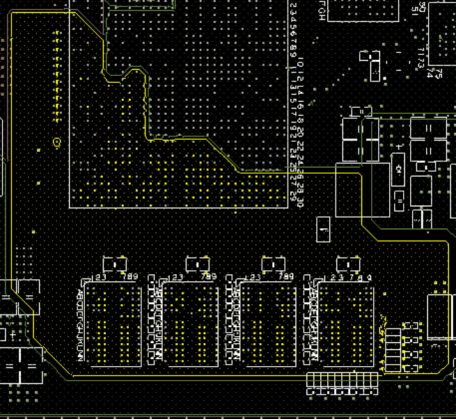

DDR3數據信號的分組

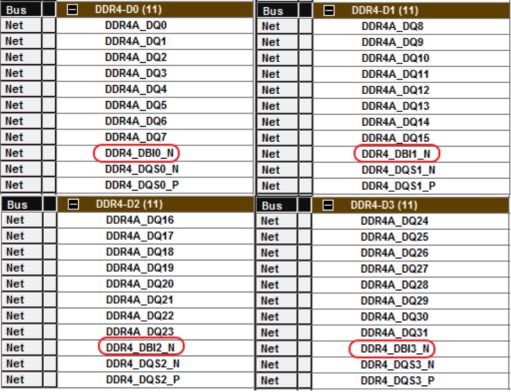

DDR4數據信號的分組

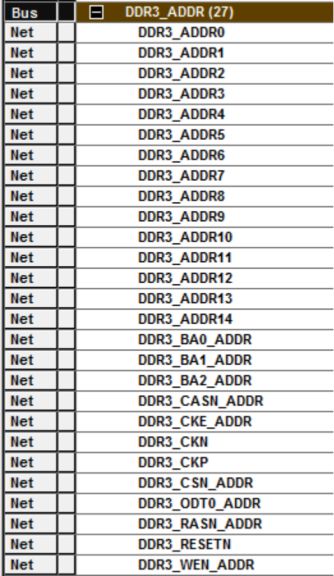

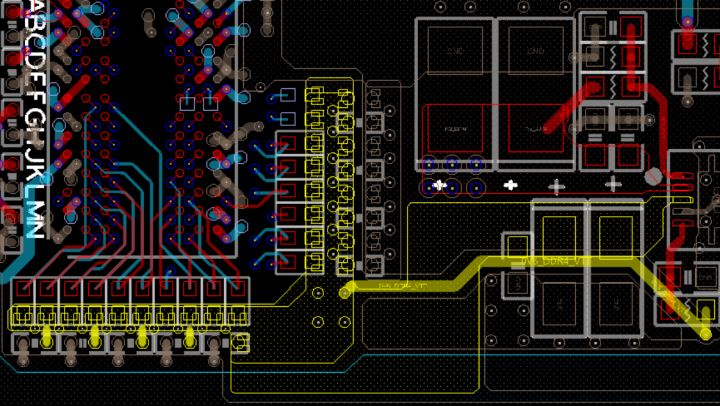

DDR3地址信號的分組

DDR4地址信號的分組

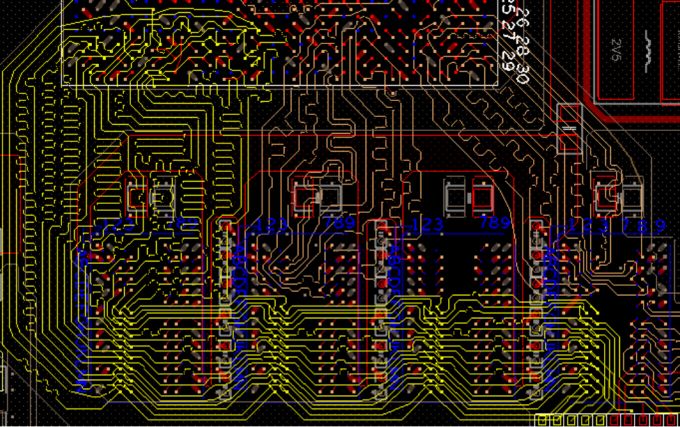

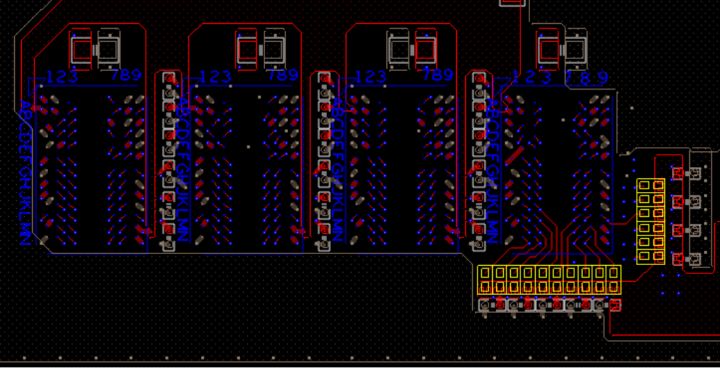

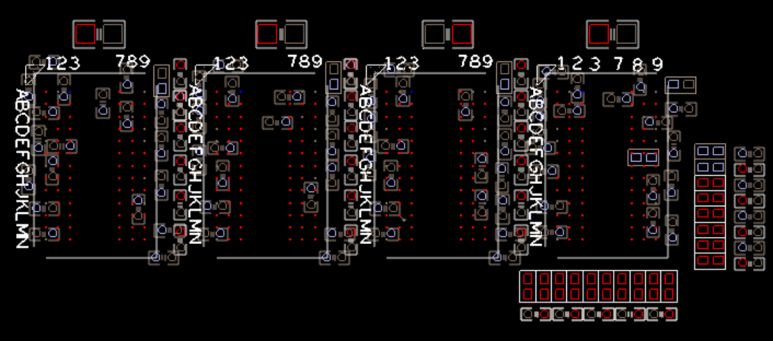

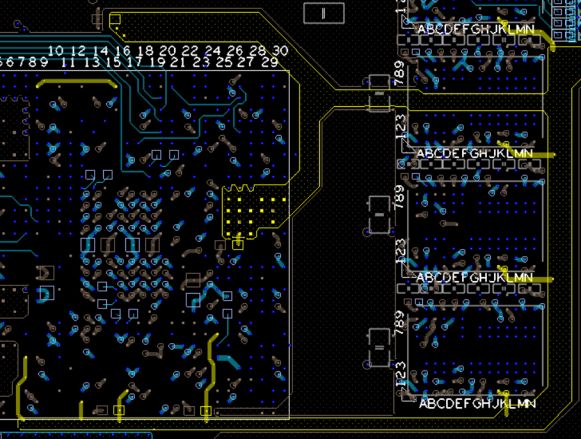

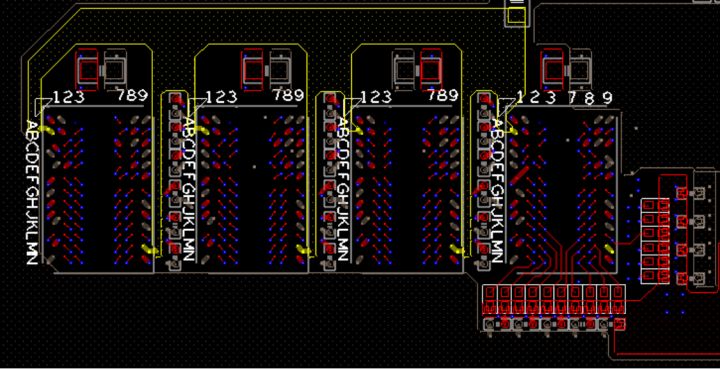

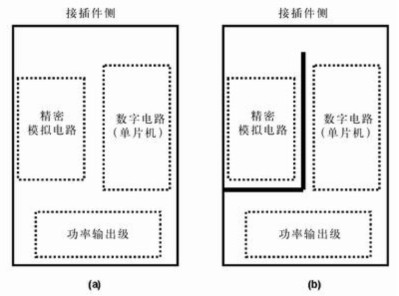

布局要求

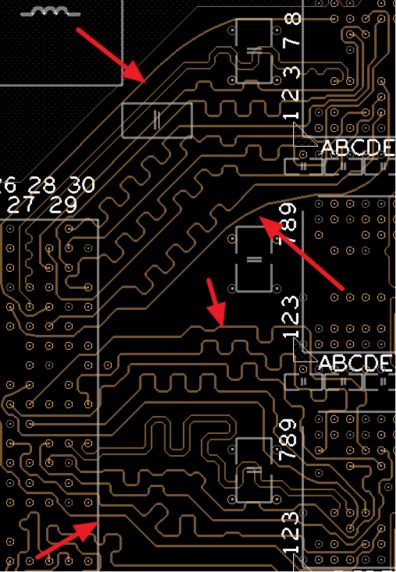

(1)地址線布局布線需使用Fly-by的拓撲結構,不可使用T型,拓撲過孔到管腳的長度盡量短,長度在150mil左右

(2)VTT上拉電阻放置在相應網絡的末端,即靠近最后一個DDR4顆粒的位置放置;注意VTT上拉電阻到DDR4顆粒的走線越短越好,走線長度小于500mil;每個VTT上拉電阻對應放置一個VTT的濾波電容(最多兩個電阻共用一個電容)

(3)CPU端和DDR4顆粒端,每個引腳對應一個濾波電容,濾波電容盡可能靠近引腳放置。線短而粗,回路盡量短;CPU和顆粒周邊均勻擺放一些儲能電容,DDR4顆粒每片至少有一個儲能電容。

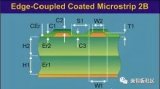

阻抗控制

(1)單端線:50ohm

(2)差分線:100ohm

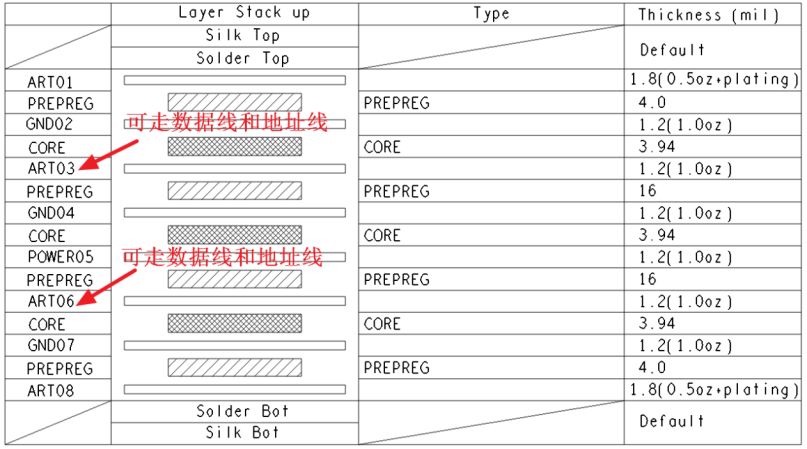

帶狀線和平面

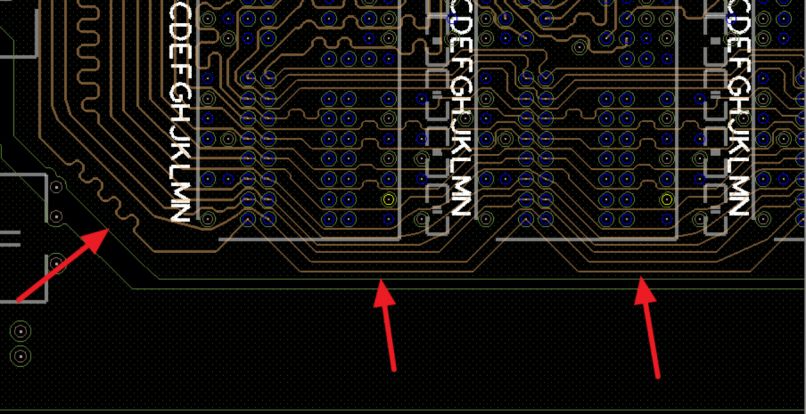

(1)除了從焊盤到過孔之間的短線外,所有的走線都必須走帶狀線,即內層走線

(2)所有的內層走線都要求夾在兩個參考平面之間,即相鄰層不要有信號層,這樣可以避免串擾和跨分割走線,走線到平面的邊緣必須保持4mil以上的間距;

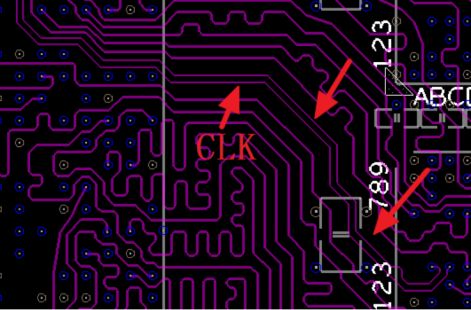

(3)數據線參考平面優先兩邊都是GND,接受一邊地,一邊自身電源,但是到GND平面的距離要比到電源平面的距離要近;對于地址線,控制信號,CLK來說,參考面首選GND和VDD,也可以選GND和GND。

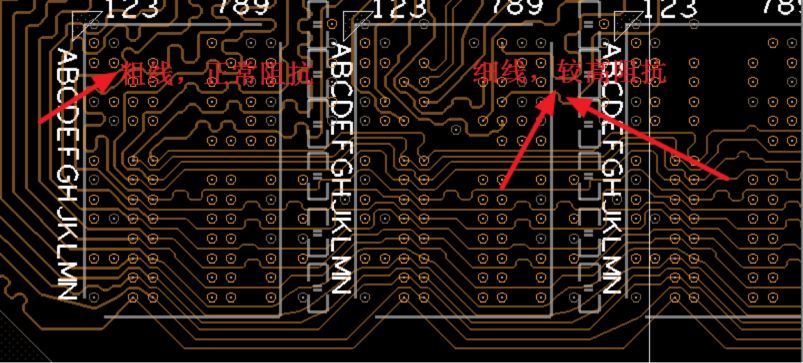

容性負載補償

flyby拓撲要求stub走線很短,當stub走線相對于信號邊沿變化率很短時,stub支線和負載呈容性。負載引入的電容,實際被分攤到了走線上,所以造成走線的單位電容增加,從而降低了走線的有效阻抗。所以在設計中,我們應該將負載部分的走線設計為較高阻抗,最直接有效的方式就是減小支線線寬。經過負載電容的平均后,負載部分的走線才會和主線阻抗保持一致,從而達到阻抗連續,降低反射的效果。

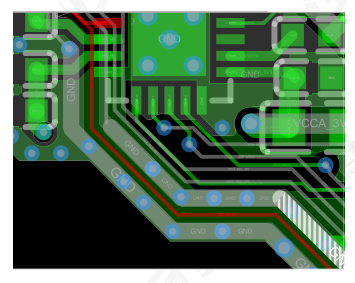

PCB疊層設計

(1)所有的DQ線必須同組同層。

(2)地址線是否同層不做要求。

(3)為了減少過孔產生的Stub,強烈建議在同一層中優先布DQ,DQS,CLK等信號。如果所有的BGA都在top層,data線盡量的靠近bottom層走,而地址,控制線則可以靠近top層走;當BGA在top層時,越靠近bottom層,過孔產生的stub越短,信號質量越好。

走線線寬和線間距

(1)線寬和線間距必須滿足阻抗控制,即單端線50ohm,差分線100ohm。ZQ屬于模擬信號,布線盡可能短,并且阻抗越低越好,所以盡可能的把線走寬一點,建議3倍50ohm阻抗控制的線寬;

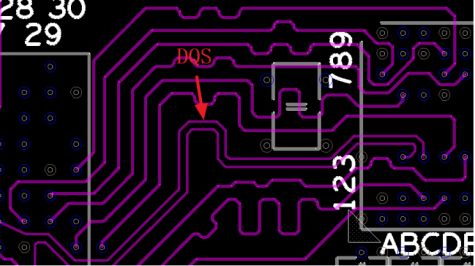

(2)DQ和DBI數據線,組內要求滿足3W間距,與其他組外信號之間保持至少4W;

(3)DQS和CLK距離其他信號間距做到5W以上;

(4)在過孔比較密集的BGA區域,同組內的數據線,地址線的間距可以縮小到2W,但是要求這樣的走線盡可能的短,并且盡可能的走直線;

(5)如果空間允許,所有的信號線走線之間的間距盡可能的保證均勻美觀;

(6)內存信號與其他非內存信號之間應該保證4倍的介質層高的距離。

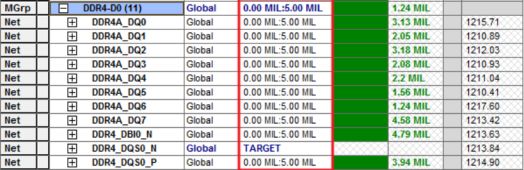

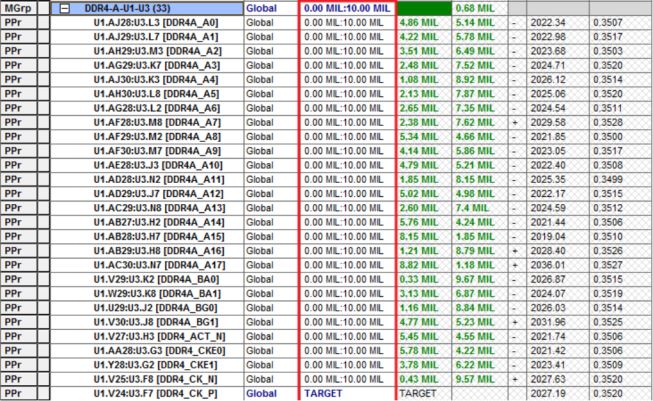

等長要求

(1)數據走線盡量短,不要超過2000mil,分組做等長,組內等長參考DQS誤差范圍控制在+/-5mil;

(2)地址線、控制線、時鐘線作為一組等長,組內等長參考CLK誤差范圍控制在+/-10mil;

(3)DQS、時鐘差分線對內誤差范圍控制在+/-2mil;

(4)RESET和ALERT不需要做等長控制

(5)信號實際長度應當包括零件管腳的長度,盡量取得零件管腳長度,并導入軟件中;

(6)因有些IC內核設計比較特別,按新品設計指導書或說明按參考板做,特別是Intel,AMD的芯片,請特別留意芯片手冊要求;

電源處理

(1)VDD(1.2V)電源是DDR3的核心電源,其引腳分布比較散,且電流相對會比較大,需要在電源平面分配一個區域給VDD(1.2V);VDD的容差要求是5%,詳細在JEDEC里有敘述。通過電源層的平面電容和專用的一定數量的去耦電容,可以做到電源完整性。

(2)VTT(0.6V)電源,它不僅有嚴格的容差性,而且還有很大的瞬間電流;可以通過增加去耦電容來實現它的目標阻抗;由于VTT是集中在上拉電阻處,不是很分散,且對電流有一定的要求,在處理VTT電源時,一般是在元件面同層通過鋪銅直接連接,銅皮要有一定寬度(120mil)。

(3)VREF(0.6V)VREF要求更加嚴格的容差性,但是它承載的電流比較小。它不需要非常寬的走線,且通過一兩個去耦電容就可以達到目標阻抗的要求。因其相對比較獨立,電流也不大,布線處理時建議用與器件同層的銅皮或走線直接連接,無須再電源平面層為其分配電源。注意鋪銅或走線時,要先經過電容再接到芯片的電源引腳,不要從分壓電阻那里直接接到芯片的電源引腳。

(4)VPP(2.5V)內存的激活供電,容差相對寬松,最小2.375V,最大2.75V。電流也不是很大,一般走根粗線或者畫塊小銅皮即可。

DDR4設計的約束條件挺多的,有沒有覺得很難,無從下手?沒關系,看文字一臉懵逼,咱還有視頻教程,你離會畫DDR4的距離只差一個二維碼。

-

pcb

+關注

關注

4354文章

23428瀏覽量

406919 -

濾波電容

+關注

關注

8文章

459瀏覽量

40940 -

DDR4

+關注

關注

12文章

329瀏覽量

41541

原文標題:DDR4設計概述及PCB設計規范

文章出處:【微信號:PCBTech,微信公眾號:EDA設計智匯館】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

扒一扒我看過的那些Linux相關的書籍

濾波電路的PCB設計注意事項

pcb設計注意事項

扒一扒中斷為什么不能調printf?

扒一扒DDR4的新功能和PCB設計上的一些注意事項

扒一扒DDR4的新功能和PCB設計上的一些注意事項

評論