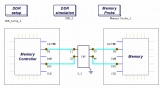

這個(gè) 15 分鐘的在線(xiàn)研討會(huì)探討了 DDR 存儲(chǔ)器接口,并展示了如何使用這個(gè)簡(jiǎn)單易用的向?qū)?lái)幫助您在設(shè)計(jì)流程中管理 DDR 問(wèn)題。

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7653瀏覽量

167407 -

DDR

+關(guān)注

關(guān)注

11文章

732瀏覽量

66825 -

仿真

+關(guān)注

關(guān)注

52文章

4289瀏覽量

135867

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

DDR模塊的PCB設(shè)計(jì)要點(diǎn)

在高速PCB設(shè)計(jì)中,DDR模塊是絕對(duì)繞不過(guò)去的一關(guān)。無(wú)論你用的是DDR、DDR2還是DDR3,只要設(shè)計(jì)不規(guī)范,后果就是——信號(hào)反射、時(shí)序混亂

利用.func命令運(yùn)行仿真的方法

在上篇 LTspice 系列文章中,我們分享了如何利用ISO模型進(jìn)行電源線(xiàn)瞬態(tài)電傳導(dǎo)干擾測(cè)試,本文將介紹使用 .func 命令中的指定常數(shù)以有效運(yùn)行仿真并進(jìn)行參數(shù)分析的方法。更多參數(shù)分

Verilog 電路仿真常見(jiàn)問(wèn)題 Verilog 在芯片設(shè)計(jì)中的應(yīng)用

在現(xiàn)代電子設(shè)計(jì)自動(dòng)化(EDA)領(lǐng)域,Verilog作為一種硬件描述語(yǔ)言,已經(jīng)成為數(shù)字電路設(shè)計(jì)和驗(yàn)證的標(biāo)準(zhǔn)工具。它允許設(shè)計(jì)師以高級(jí)抽象的方式定義電路的行為和結(jié)構(gòu),從而簡(jiǎn)化了從概念到硅片的整個(gè)設(shè)計(jì)流程

淺談DDR6 RAM設(shè)計(jì)挑戰(zhàn)

DDR6 RAM 是 目前DDR 迭代中的最新版本,最大的數(shù)據(jù)速率峰值超過(guò) 12000 MT/s。

DDR5內(nèi)存的工作原理詳解 DDR5和DDR4的主要區(qū)別

的數(shù)據(jù)傳輸速率、更大的容量和更低的功耗。 2. DDR5內(nèi)存工作原理 DDR5內(nèi)存的工作原理基于雙倍數(shù)據(jù)速率技術(shù),即在每個(gè)時(shí)鐘周期內(nèi)傳輸兩次數(shù)據(jù)。DDR5內(nèi)存通過(guò)提高數(shù)據(jù)傳輸速率、增加數(shù)據(jù)預(yù)取和優(yōu)化功耗

使用增強(qiáng)型仿真模塊(EEM)和CCS v6進(jìn)行高級(jí)調(diào)試

電子發(fā)燒友網(wǎng)站提供《使用增強(qiáng)型仿真模塊(EEM)和CCS v6進(jìn)行高級(jí)調(diào)試.pdf》資料免費(fèi)下載

發(fā)表于 10-21 09:53

?0次下載

邏輯組件中的流程塊節(jié)點(diǎn)通常出于什么用途

邏輯組件中的流程塊節(jié)點(diǎn)是流程圖、狀態(tài)圖、序列圖等圖表中的基本元素,它們用于表示業(yè)務(wù)流程、工作流程

wms智能倉(cāng)儲(chǔ)管理系統(tǒng)標(biāo)準(zhǔn)化流程

wms智能倉(cāng)儲(chǔ)管理系統(tǒng)標(biāo)準(zhǔn)化流程的標(biāo)準(zhǔn)化流程通常包括以下幾個(gè)主要步驟: 需求分析:與客戶(hù)充分溝通,了解其倉(cāng)儲(chǔ)管理需求和業(yè)務(wù)流程,確定系統(tǒng)功能

TI電池監(jiān)控器IC的高級(jí)電量監(jiān)測(cè)器固件流程圖

電子發(fā)燒友網(wǎng)站提供《TI電池監(jiān)控器IC的高級(jí)電量監(jiān)測(cè)器固件流程圖.pdf》資料免費(fèi)下載

發(fā)表于 10-12 10:07

?0次下載

DDR Inline ECC在Jacinto7 SoC中的應(yīng)用

電子發(fā)燒友網(wǎng)站提供《DDR Inline ECC在Jacinto7 SoC中的應(yīng)用.pdf》資料免費(fèi)下載

發(fā)表于 09-27 11:04

?0次下載

利用仿真技術(shù)進(jìn)行智能制動(dòng)系統(tǒng)的開(kāi)發(fā)

在當(dāng)前的汽車(chē)行業(yè)中,安全性仍然是首要關(guān)注點(diǎn)之一。自動(dòng)緊急制動(dòng)系統(tǒng)(AEB)作為增強(qiáng)道路安全的核心技術(shù),正逐漸普及。該系統(tǒng)通過(guò)高級(jí)傳感器和算法來(lái)預(yù)測(cè)和應(yīng)對(duì)潛在的撞車(chē)風(fēng)險(xiǎn),極大提升了安全性。在 AEB 系統(tǒng)的開(kāi)發(fā)過(guò)程中,

DDR4尋址原理詳解

)的尋址原理是計(jì)算機(jī)內(nèi)存系統(tǒng)中至關(guān)重要的一個(gè)環(huán)節(jié),它決定了數(shù)據(jù)如何在內(nèi)存中被有效地存儲(chǔ)和訪(fǎng)問(wèn)。DDR4的尋址原理復(fù)雜而高效,以下將詳細(xì)闡述其關(guān)鍵要素和工作流程。

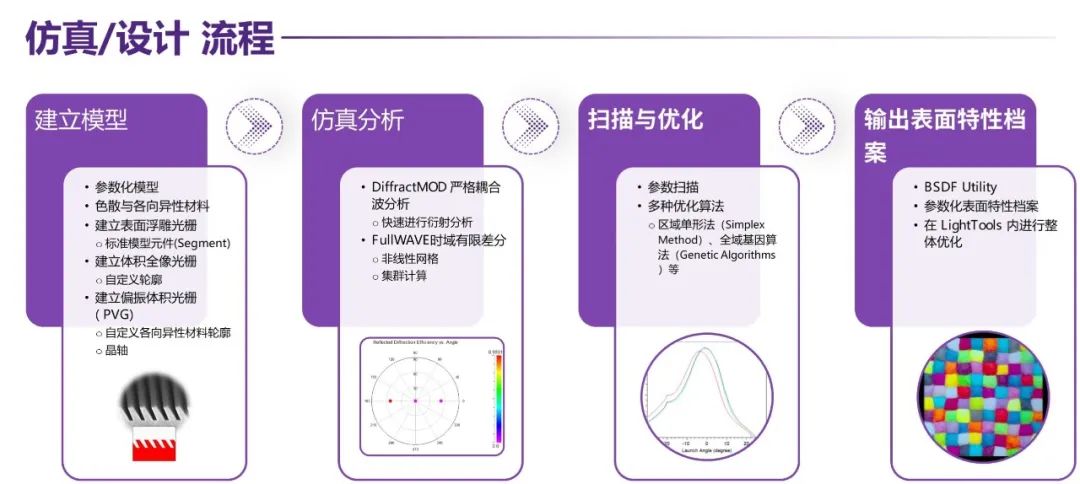

使用新思科技波動(dòng)光學(xué)軟件RSoft進(jìn)行光柵仿真/設(shè)計(jì)的流程

增強(qiáng)現(xiàn)實(shí)(AR)眼鏡使用戶(hù)能夠在現(xiàn)實(shí)世界的環(huán)境中疊加數(shù)字圖像,可廣泛應(yīng)用于教育、醫(yī)療、導(dǎo)航、游戲和娛樂(lè)等領(lǐng)域。為了設(shè)計(jì)更輕巧的AR眼鏡,利用超緊湊的衍射光波導(dǎo)元件成為其中一種具有潛力的方案,其中關(guān)鍵

DDR的工作原理與應(yīng)用

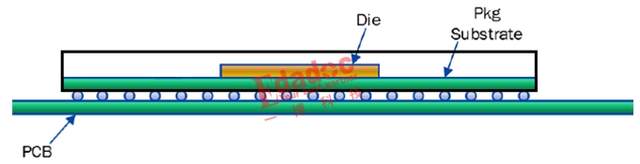

在高速信號(hào)設(shè)計(jì)中,DDR仿真被廣泛應(yīng)用于驗(yàn)證信號(hào)完整性。隨著電子產(chǎn)品向小型化、精密化和高速化發(fā)展,DDR等高速通道的設(shè)計(jì)需要全面考慮從發(fā)送端、傳輸線(xiàn)到接收端的整個(gè)通信鏈路。

利用高級(jí)仿真解決設(shè)計(jì)流程中管理DDR問(wèn)題

利用高級(jí)仿真解決設(shè)計(jì)流程中管理DDR問(wèn)題

評(píng)論