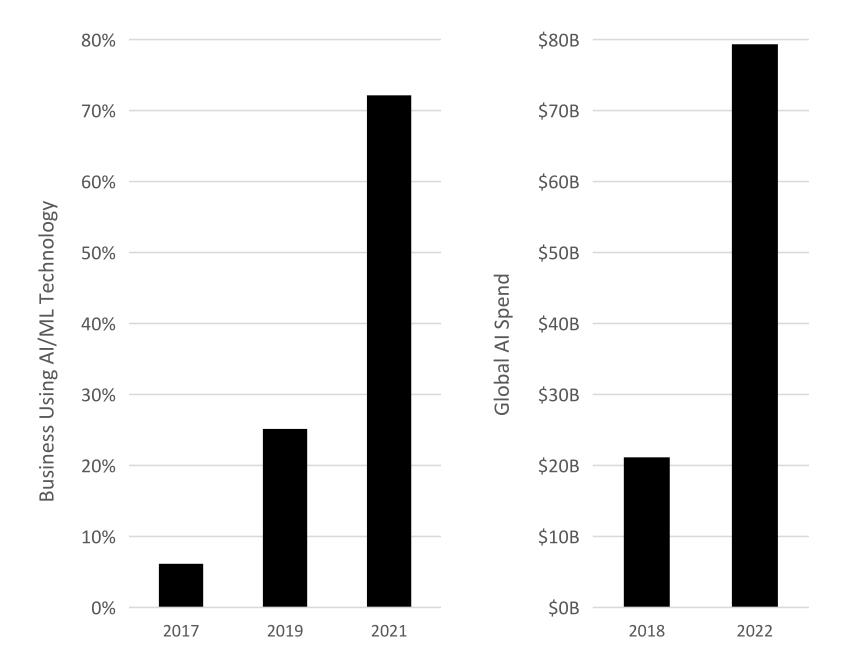

過去幾年,FPGA的CAGR大約一直保持在8-10%左右,隨著該類器件在AI應(yīng)用中的擴(kuò)張,未來5年其CAGR增長(zhǎng)將高達(dá)38.4%!根據(jù)市場(chǎng)調(diào)研公司Semico Research的預(yù)測(cè),人工智能應(yīng)用中FPGA的市場(chǎng)規(guī)模將在未來4年內(nèi)增長(zhǎng)3倍,達(dá)到52億美元。為了保持競(jìng)爭(zhēng)力,目前全球有25%的企業(yè)實(shí)施了人工智能/機(jī)器學(xué)習(xí)(AI/ML),而兩年內(nèi),這一比例將增長(zhǎng)到72%,以更好地獲得核心職能方面的商業(yè)洞察力。

圖:企業(yè)AI/ML部署需求增長(zhǎng)趨勢(shì)

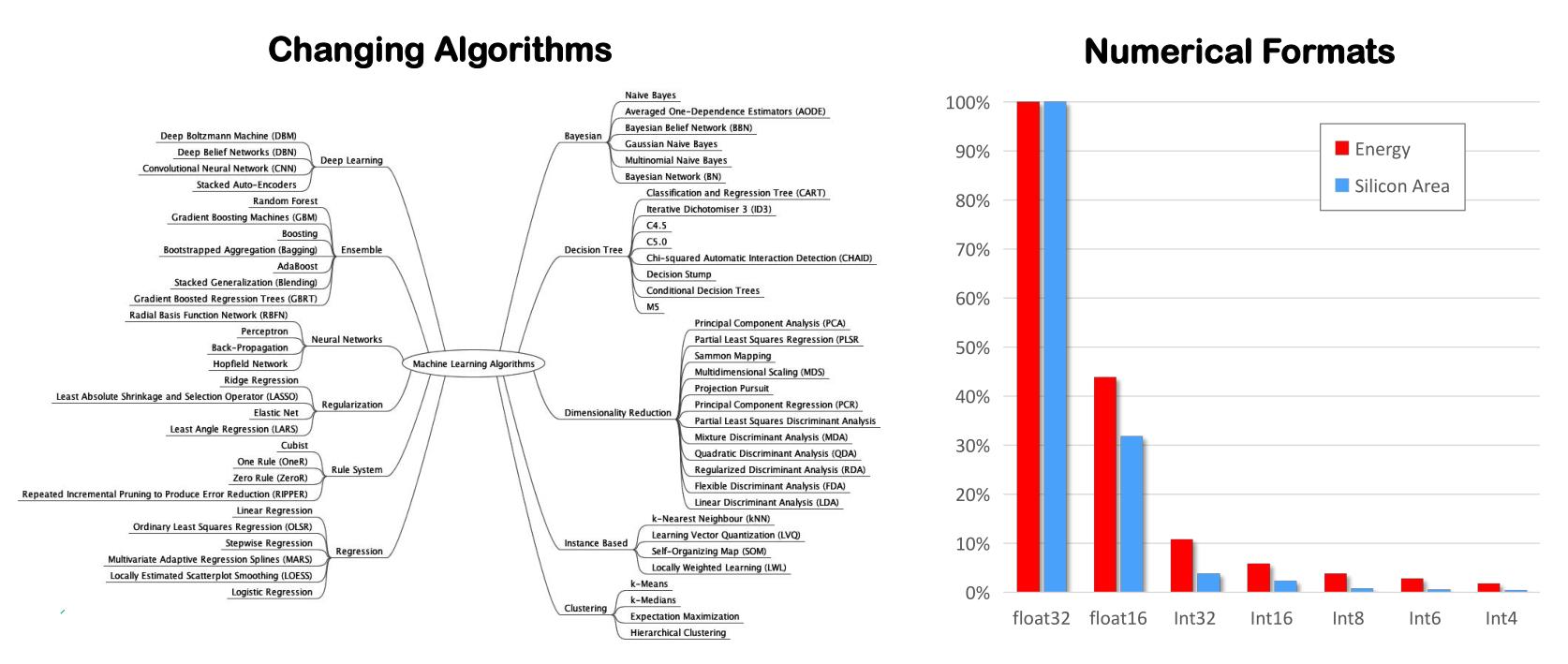

伴隨這一趨勢(shì),AI的算法在不斷演進(jìn),對(duì)數(shù)值精度的選擇要求也更加多元,高效算力、高效豐富的存儲(chǔ)緩存能力以及高效大帶寬的數(shù)據(jù)運(yùn)送能力,是AI/ML硬件解決方案所面臨的主要挑戰(zhàn)。系統(tǒng)開發(fā)者會(huì)利用FPGA架構(gòu)去優(yōu)化功耗、性能和靈活性,并突破處理單元在效率上的瓶頸,包括計(jì)算引擎、內(nèi)存層次結(jié)構(gòu)和數(shù)據(jù)移動(dòng)。

圖:算法和精度要求不同給處理帶來挑戰(zhàn)

就AI的應(yīng)用而言,不同場(chǎng)景應(yīng)用對(duì)FPGA的需求不同。通常云計(jì)算中的應(yīng)用主要是需要FPGA在AI/ML和高帶寬數(shù)據(jù)加速上的能力,而在端側(cè)則需要在高靈活性的同時(shí)還要具有ASIC的性能。雖然,F(xiàn)PGA已經(jīng)大量應(yīng)用于泛AI領(lǐng)域,但它是否很好的滿足這兩個(gè)方面的需求,還是一個(gè)值得探討的話題。

重構(gòu)FPGA架構(gòu)

縱觀FPGA產(chǎn)品的演進(jìn)歷史(包括器件的產(chǎn)生),每一次大的迭代都是一種設(shè)計(jì)方法論的革新,從這個(gè)角度看,Achronix公司最近發(fā)布的Speedster7t針對(duì)上述兩個(gè)應(yīng)用場(chǎng)景上進(jìn)行的優(yōu)化都可以看做方法論上的革新。在開發(fā)Speedster7t的過程中,Achronix的工程團(tuán)隊(duì)完全重新構(gòu)想了整個(gè)FPGA架構(gòu),以平衡片上處理、互連和外部輸入輸出接口,實(shí)現(xiàn)數(shù)據(jù)密集型應(yīng)用吞吐量的最大化,這些應(yīng)用場(chǎng)景可見于那些基于邊緣和基于服務(wù)器的AI/ML應(yīng)用、網(wǎng)絡(luò)處理和存儲(chǔ)。

“Speedster7t是我們歷史上最令人激動(dòng)的發(fā)布,代表了建立在四個(gè)架構(gòu)代系的硬件和軟件開發(fā)基礎(chǔ)上的創(chuàng)新和積淀。”Achronix公司董事長(zhǎng)兼首席執(zhí)行官Robert Blake介紹,“該器件采用TSMC的7nm FinFET工藝制造,專為ML和高帶寬網(wǎng)絡(luò)應(yīng)用進(jìn)行了優(yōu)化。”

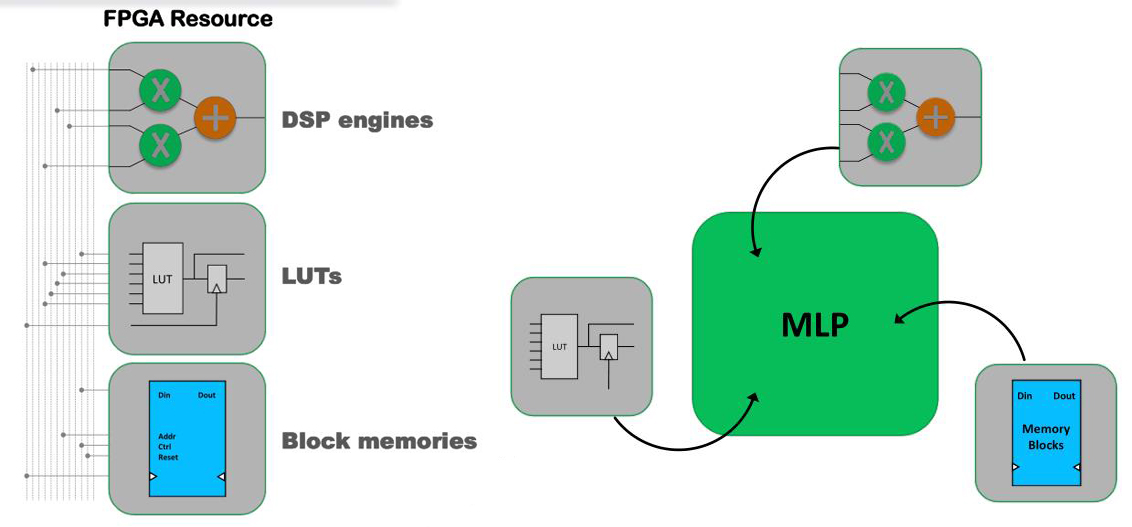

具體而言,相較于目前的FPGA,Speedster7t革新之處在于設(shè)計(jì)了針對(duì)ML的處理器(MLP),以及一個(gè)可橫跨和垂直跨越FPGA邏輯陣列的高帶寬的二維片上網(wǎng)絡(luò)(NOC),二者結(jié)合既保留了FPGA的靈活性,又實(shí)現(xiàn)了ASIC的性能。

不占用FPGA布線的MLP單元

這個(gè)片內(nèi)的MLP是高度可配置的、計(jì)算密集型的單元模塊,可支持4到24位的整點(diǎn)格式和高效的浮點(diǎn)模式,包括對(duì)TensorFlow的16位格式的支持,以及可使每個(gè)MLP的計(jì)算引擎加倍的增壓塊浮點(diǎn)格式的直接支持。該MLP可以通過運(yùn)算和緩存級(jí)鏈實(shí)現(xiàn)更復(fù)雜的算法,而不需要使用FPGA布線資源。

“目前FPGA會(huì)使用DSP來進(jìn)行ML的處理,但其對(duì)數(shù)值精度的支持并不高效,并且需要消耗額外邏輯和存儲(chǔ)資源,其性能也受限于FPGA布線。”Blake說,“DSP常用于無線數(shù)字濾波的處理,而Speedster7t中的MLP則在計(jì)算架構(gòu)、緩存(內(nèi)嵌)、可配置算法以及對(duì)整點(diǎn)和浮點(diǎn)的支持上提供了更好的AI/ML的計(jì)算性能和能效比。”

圖:在FPGA中采用MLP(右)比DSP(左)更適用于AI/ML處理

二維片上網(wǎng)絡(luò)——NOC

NOC是在FPGA路由結(jié)構(gòu)上的另一個(gè)重要革新。這一設(shè)計(jì)主要針對(duì)FPGA的片上處理引擎之間所需的高帶寬通信。Speedster7t片上資源包括8個(gè)GDDR6控制器、72個(gè)業(yè)界SerDes(1到112 Gbps)、帶有前向糾錯(cuò)(FEC)的硬件400G以太網(wǎng)MAC(4x100G或8x50G的配置),以及硬件PCI Express Gen5控制器(每個(gè)控制器有8個(gè)或16個(gè)通道)。

這些高速I/O和存儲(chǔ)器端口的數(shù)萬兆比特?cái)?shù)據(jù)很容易淹沒傳統(tǒng)FPGA面向比特位的可編程互連邏輯陣列的路由容量,而Speedster7t通過NOC把它們連接到所有FPGA的高速數(shù)據(jù)和存儲(chǔ)器接口。NOC和FPGA功能之間通過網(wǎng)絡(luò)接入點(diǎn)NAP連接,每個(gè)水平行和垂直列的交叉點(diǎn)都有NAP(主NAP和從NAP)。NoC中的每行/列都可同時(shí)為每個(gè)方向提供512Gbps的數(shù)據(jù)流量,其鏈路雙向運(yùn)行,最大的設(shè)備帶寬可以達(dá)到20Tbps。

“最重要的是,NOC消除了傳統(tǒng)FPGA使用可編程路由和邏輯查找表資源在整個(gè)FPGA中移動(dòng)數(shù)據(jù)流中出現(xiàn)的擁塞和性能瓶頸。”Blake說,“這種高性能網(wǎng)絡(luò)不僅可以提高Speedster7t FPGA的總帶寬容量,還可以在降低功耗的同時(shí)提高有效LUT容量。”

圖:NOC是在FPGA路由結(jié)構(gòu)上的另一個(gè)重要革新

的確,NOC這一方法解決了GDDR6、400G以太網(wǎng)MAC這些片上資源海量數(shù)據(jù)傳輸?shù)膯栴}。Speedster7t是目前市面唯一支持GDDR6存儲(chǔ)器的FPGA,可以支持4 Tbps的GDDR6累加帶寬,可以很小的成本提供與基于HBM的FPGA等效存儲(chǔ)帶寬。相較于HBM,GDDR6只需要一半的成本就可以滿足高存儲(chǔ)層次和帶寬的需求,并且,HBM是固化的塊,GDDR6則更靈活,用戶可以選擇不同容量和帶寬。

NOC也解決了傳統(tǒng)FPGA的運(yùn)行速度無法滿足任何400G以太網(wǎng)總線寬度要求的問題,400G以太網(wǎng)的總線大小達(dá)1024bit,所需的最高頻率達(dá)到724 MHz,這在傳統(tǒng)FPGA中無法實(shí)現(xiàn),NOC由于消除了傳統(tǒng)設(shè)計(jì)中與FPGA布線相關(guān)的延遲,所以可以最高支持750 MHz的頻率,這滿足了MLP和嵌入式存儲(chǔ)器模、400G以太網(wǎng)MAC及高速SerDes之間的數(shù)據(jù)傳輸。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

FPGA

+關(guān)注

關(guān)注

1644文章

21993瀏覽量

615439 -

NoC

+關(guān)注

關(guān)注

0文章

39瀏覽量

11910

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

【「具身智能機(jī)器人系統(tǒng)」閱讀體驗(yàn)】+數(shù)據(jù)在具身人工智能中的價(jià)值

嵌入式人工智能(EAI)將人工智能集成到機(jī)器人等物理實(shí)體中,使它們能夠感知、學(xué)習(xí)環(huán)境并與之動(dòng)態(tài)交互。這種能力使此類機(jī)器人能夠在人類社會(huì)中有效地提供商品及服務(wù)。

數(shù)據(jù)是一種貨幣化工具

數(shù)據(jù)是互聯(lián)網(wǎng)

發(fā)表于 12-24 00:33

卡諾模型為人工智能領(lǐng)域提供了一種全新的視角

在探索人工智能如何更深層次滿足用戶需求、提升用戶體驗(yàn)的旅程中,卡諾模型(Kano Model)提供了一個(gè)極具價(jià)值的理論框架。這一模型不僅為產(chǎn)

FPGA 在人工智能中的應(yīng)用

隨著人工智能技術(shù)的飛速發(fā)展,FPGA(現(xiàn)場(chǎng)可編程門陣列)在AI領(lǐng)域扮演著越來越重要的角色。FPGA以其獨(dú)特的靈活性、低延遲和高能效等優(yōu)勢(shì),為AI應(yīng)用提供了強(qiáng)大的硬件支持。 1.

集成電路與人工智能結(jié)合

集成電路,為人工智能算法提供了強(qiáng)大的算力支持。 隨著人工智能技術(shù)的不斷發(fā)展,對(duì)存儲(chǔ)和計(jì)算能力的需求日益增長(zhǎng),而集成電路的快速發(fā)展正好滿足了

嵌入式和人工智能究竟是什么關(guān)系?

嵌入式和人工智能究竟是什么關(guān)系?

嵌入式系統(tǒng)是一種特殊的系統(tǒng),它通常被嵌入到其他設(shè)備或機(jī)器中,以實(shí)現(xiàn)特定功能。嵌入式系統(tǒng)具有非常強(qiáng)的適應(yīng)性和靈活性,能夠根據(jù)用戶需求進(jìn)行定制化設(shè)計(jì)。它廣泛應(yīng)用于各種

發(fā)表于 11-14 16:39

FPGA應(yīng)用于人工智能的趨勢(shì)

FPGA(現(xiàn)場(chǎng)可編程門陣列)在人工智能領(lǐng)域的應(yīng)用趨勢(shì)日益顯著,主要?dú)w因于其高速、低功耗、靈活性和并行處理能力等獨(dú)特優(yōu)勢(shì)。以下是對(duì)FPGA應(yīng)用于人工智能趨勢(shì)的分析:

Adobe發(fā)布人工智能視頻創(chuàng)作工具:Firefly Video Model

Adobe公司于10月15日正式揭曉了其最新研發(fā)的人工智能視頻創(chuàng)作工具——Firefly Video Model。這一創(chuàng)新解決方案旨在借助AI技術(shù),賦能視頻內(nèi)容創(chuàng)作者拓寬創(chuàng)意邊界,提升

《AI for Science:人工智能驅(qū)動(dòng)科學(xué)創(chuàng)新》第6章人AI與能源科學(xué)讀后感

驅(qū)動(dòng)科學(xué)創(chuàng)新》的第6章為我提供了寶貴的知識(shí)和見解,讓我對(duì)人工智能在能源科學(xué)中的應(yīng)用有了更深入的認(rèn)識(shí)。通過閱讀這一章,我更加堅(jiān)信人工智能在未來

發(fā)表于 10-14 09:27

AI for Science:人工智能驅(qū)動(dòng)科學(xué)創(chuàng)新》第4章-AI與生命科學(xué)讀后感

閱讀這一章后,我深感人工智能與生命科學(xué)的結(jié)合正引領(lǐng)著一場(chǎng)前所未有的科學(xué)革命,以下是我個(gè)人的讀后感:

1. 技術(shù)革新與生命科學(xué)進(jìn)步

這一章詳細(xì)

發(fā)表于 10-14 09:21

《AI for Science:人工智能驅(qū)動(dòng)科學(xué)創(chuàng)新》第一章人工智能驅(qū)動(dòng)的科學(xué)創(chuàng)新學(xué)習(xí)心得

,還促進(jìn)了新理論、新技術(shù)的誕生。

3. 挑戰(zhàn)與機(jī)遇并存

盡管人工智能為科學(xué)創(chuàng)新帶來了巨大潛力,但第一章也誠(chéng)實(shí)地討論了伴隨而來的挑戰(zhàn)。數(shù)據(jù)隱私、算法偏見、倫理道德等問題不容忽視。如何在利

發(fā)表于 10-14 09:12

risc-v在人工智能圖像處理應(yīng)用前景分析

滿足人工智能圖像處理中對(duì)于高性能、低功耗和特定功能的需求。

低功耗 :

在人工智能圖像處理中,低功耗是一個(gè)重要的考量因素。RISC-V架構(gòu)的設(shè)計(jì)使其在處理任務(wù)時(shí)能夠保持較低的功耗水平

發(fā)表于 09-28 11:00

名單公布!【書籍評(píng)測(cè)活動(dòng)NO.44】AI for Science:人工智能驅(qū)動(dòng)科學(xué)創(chuàng)新

芯片設(shè)計(jì)的自動(dòng)化水平、優(yōu)化半導(dǎo)體制造和封測(cè)的工藝和水平、尋找新一代半導(dǎo)體材料等方面提供幫助。

第6章介紹了人工智能在化石能源科學(xué)研究、可再生能源科學(xué)研究、能源轉(zhuǎn)型三個(gè)方面的落地應(yīng)用。

第7章從環(huán)境監(jiān)測(cè)

發(fā)表于 09-09 13:54

報(bào)名開啟!深圳(國(guó)際)通用人工智能大會(huì)將啟幕,國(guó)內(nèi)外大咖齊聚話AI

呈現(xiàn)、產(chǎn)業(yè)展覽、技術(shù)交流、學(xué)術(shù)論壇于一體的世界級(jí)人工智能合作交流平臺(tái)。本次大會(huì)暨博覽會(huì)由工業(yè)和信息化部政府采購中心、廣東省工商聯(lián)、前海合作區(qū)管理局、深圳市工信局等單位指導(dǎo),深圳市人工智能產(chǎn)業(yè)協(xié)會(huì)主辦

發(fā)表于 08-22 15:00

激光封裝技術(shù)在人工智能發(fā)展中的作用

的性能瓶頸。這些傳統(tǒng)方案增加了功耗和成本,凸顯了創(chuàng)新解決方案的迫切需求。 光I/O和光電共封裝(CPO)解決方案是最有前途的技術(shù)進(jìn)展之一。通

FPGA在人工智能中的應(yīng)用有哪些?

FPGA(現(xiàn)場(chǎng)可編程門陣列)在人工智能領(lǐng)域的應(yīng)用非常廣泛,主要體現(xiàn)在以下幾個(gè)方面:

一、深度學(xué)習(xí)加速

訓(xùn)練和推理過程加速:FPGA可以用來加速深度學(xué)習(xí)的訓(xùn)練和推理過程。由于其高并行性和

發(fā)表于 07-29 17:05

人工智能需求促進(jìn)FPGA市場(chǎng) 這一革新解決了應(yīng)用瓶頸

人工智能需求促進(jìn)FPGA市場(chǎng) 這一革新解決了應(yīng)用瓶頸

評(píng)論