Verilog HDL語(yǔ)言不僅定義了語(yǔ)法,而且對(duì)每個(gè)語(yǔ)法結(jié)構(gòu)都定義了清晰的模擬、仿真語(yǔ)義。因此,用這種語(yǔ)言編寫(xiě)的模型能夠使用Verilog仿真器進(jìn)行驗(yàn)證。語(yǔ)言從C編程語(yǔ)言中繼承了多種操作符和結(jié)構(gòu)。Verilog HDL提供了擴(kuò)展的建模能力,其中許多擴(kuò)展最初很難理解。但是,Verilog HDL語(yǔ)言的核心子集非常易于學(xué)習(xí)和使用,這對(duì)大多數(shù)建模應(yīng)用來(lái)說(shuō)已經(jīng)足夠。當(dāng)然,完整的硬件描述語(yǔ)言足以對(duì)從最復(fù)雜的芯片到完整的電子系統(tǒng)進(jìn)行描述。

-

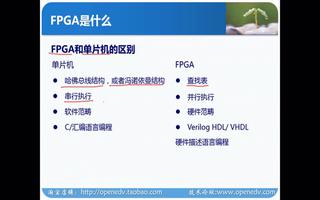

FPGA

+關(guān)注

關(guān)注

1645文章

22033瀏覽量

617742 -

仿真器

+關(guān)注

關(guān)注

14文章

1036瀏覽量

85315 -

Verilog

+關(guān)注

關(guān)注

29文章

1367瀏覽量

112190

發(fā)布評(píng)論請(qǐng)先 登錄

【正點(diǎn)原子FPGA連載】第十二章 動(dòng)態(tài)數(shù)碼管顯示實(shí)驗(yàn)

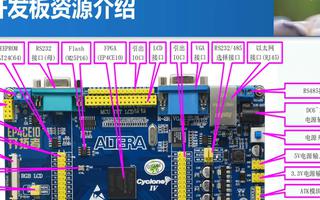

分享正點(diǎn)原子FPGA開(kāi)發(fā)板全套資料

正點(diǎn)原子開(kāi)拓者FPGA開(kāi)發(fā)板資料連載第二十一章 VGA圖片顯示實(shí)驗(yàn)

正點(diǎn)原子開(kāi)拓者FPGA開(kāi)發(fā)板資料連載第二十三章RGBTFT-LCD字符顯示

正點(diǎn)原子開(kāi)拓者FPGA開(kāi)發(fā)板資料連載第四十三章 以太網(wǎng)通信實(shí)驗(yàn)(2)

正點(diǎn)開(kāi)拓者FPGA開(kāi)發(fā)板使用問(wèn)題

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:uC/GUI圖片/數(shù)字顯示實(shí)驗(yàn)

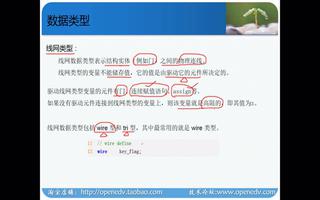

正點(diǎn)原子開(kāi)拓者FPGA視頻:Verilog基礎(chǔ)語(yǔ)法

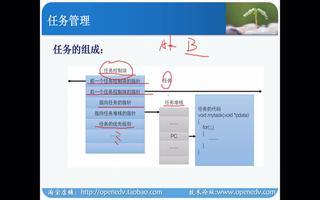

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:uCOS II任務(wù)管理與時(shí)間管理(2)

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:自定義IP核之?dāng)?shù)碼管(2)

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:PIO按鍵控制LED

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:PIO IRQ

正點(diǎn)原子開(kāi)拓者FPGA Qsys視頻:Hello World

正點(diǎn)原子開(kāi)拓者FPGA視頻:Verilog高級(jí)知識(shí)點(diǎn)

正點(diǎn)原子開(kāi)拓者FPGA視頻:Verilog高級(jí)知識(shí)點(diǎn)

評(píng)論