當采用現場可編程門陣列(FPGA)進行設計時,電源排序是需要考慮的一個重要的方面。通常情況下,FPGA 供應商都規定了電源排序要求,因為一個FPGA所需要的電源軌數量會從 3 個到 10 個以上不等。

通過遵循推薦的電源序列,可以避免在啟動期間吸取過大的電流,這反過來又可防止器件受損。對一個系統中的電源進行排序可采用多種方法來完成。本文將詳細說明可根據系統所要求的復雜程度來實現的電源排序解決方案。

本文中所討論的電源排序解決方案為:

1. 把 PGOOD 引腳級聯至使能引腳;

2. 采用一個復位 IC 來實現排序;

3. 模擬上電 / 斷電排序器;

4. 具有 PMBus 接口的數字系統健康狀況監視器。

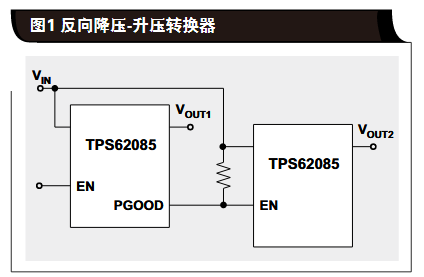

方法一:把PGOOD 引腳級聯至使能引腳

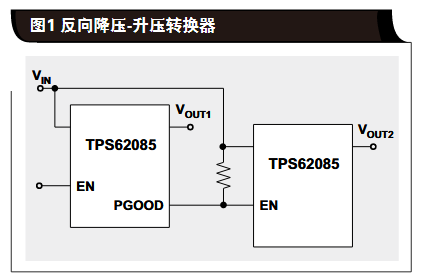

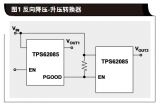

實現排序的一種基本的成本效益型方法是把一個電源的電源良好(PG)引腳級聯至相繼的下一個電源的使能(EN) 引腳。

第二個電源在 PG 門限得到滿足(通常是在電源達到其終值的90% 之時)時開始接通。這種方法的優勢是成本低,但是無法輕松地控制定時。在EN 引腳上增設一個電容器會在電路級之間引入定時延遲。然而,此方法在溫度變化和反復電源循環期間是不可靠的。而且,這種方法并不支持斷電排序。

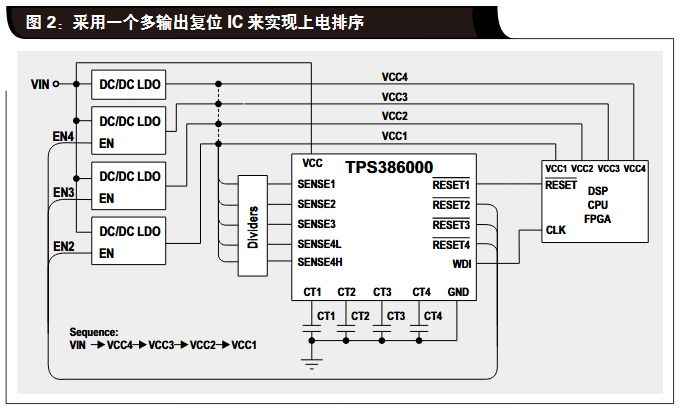

方法二:采用一個復位 IC 來實現排序

另一種可以考慮的用于上電排序的簡單選項是采用一個具有時間延遲的復位 IC。當采用此選項時,復位 IC 以嚴格的門限限值來監視電源軌。一旦電源軌處于其終值的3%(或更小)以內,復位 IC 將進入由解決方案定義的等待周期,然后再執行下一個電源軌的上電操作。該等待周期可以采用 EEPROM 編程到復位 IC 中,也可利用外部電容器來設定。圖 2 示出了一款典型的多通道復位IC。采用復位 IC 來實現上電排序的優點是解決方案處于受監視的狀態。

必須在確認每個電源軌都處在穩壓范圍內之后再釋放下一個電源軌,而且無需在電源轉換器上提供一個PGOOD 引腳。采用復位 IC 的電源排序解決方案的缺點是其并不實施斷電排序。

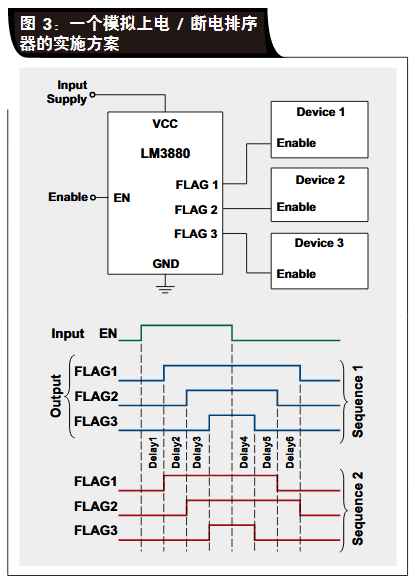

方法三:模擬上電 / 斷電排序器

實施上電排序會比實施斷電排序更加容易。為了實現上電和斷電排序,人們推出了能夠相對于上電序列進行斷電序列的逆轉(序列 1)乃至混合(序列 2)的簡單模擬排序器。

在上電時,所有的標記均保持在低電平,直到 EN 被拉至高電平為止。在 EN 被置為有效之后,每個標記于一個內部定時器計時結束后順序地變至漏極開路狀態(需要上拉電阻器)。斷電序列與上電序列相同,但次序正好相反。

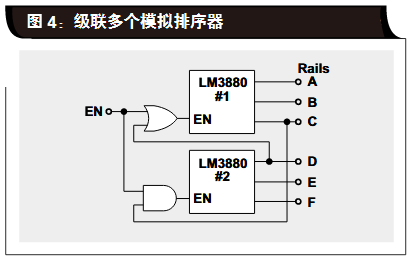

可以把排序器級聯在一起以支持多個電源軌,并在使能信號之間提供固定和可調的延遲時間。在圖 4 中,兩個排序器級聯在一起以實現 6 個有序的電源軌。上電時,AND 門確保第二個排序器在其接收到一個 EN 信號且 C 電源軌被觸發之前不被觸發。

斷電時,AND 門確保第二個排序器承受 EN 下降沿,而不考慮 C 輸出。OR 門確保第一個排序器由 EN 上升沿來觸發。斷電時,OR 門確保第一個排序器不能承受 EN 下降沿,直到 D 電源軌下降為止。這保證了上電和斷電排序,但并未提供一個受監視的序列。

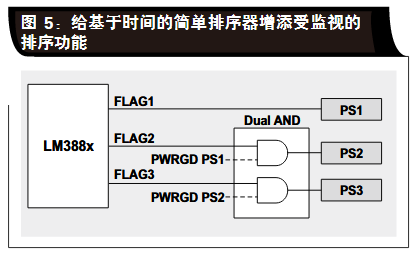

如圖 5 所示,通過簡單地在 FlagX 輸出和 PG 引腳之間增設幾個 AND 門,就能給圖 4 中的電路添加受監視的排序功能。在該例中,PS2 僅在 PS1 超過其終值的90% 的情況下使能。這種方法可提供一種低成本、受監視的排序解決方案。

方法四:具有 PMBus 接口的數字系統健康狀況監視器

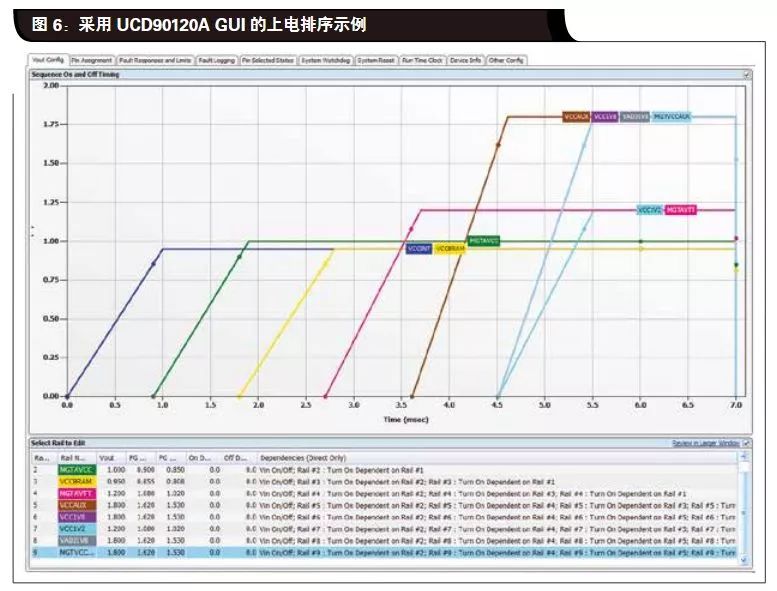

如果系統需要最大的靈活性,那么可兼容 PMBus/I2C 標準的數字系統健康狀況監視器(比如:UCD90120A)是一種不錯的解決方案。通過允許設計人員配置電源斜坡上升 / 下降時間、接通 / 關斷延遲、序列相關性、甚至包括電壓和電流監視,此類解決方案可為任何排序需求提供最大的控制。

數字系統健康狀況監視器配有一個圖形用戶界面(GUI),其可用于設置上電和斷電排序以及其他的系統參數(圖6)。另外,有些數字系統健康狀況監視器還具有非易失性誤差和峰值記錄功能,可在發生欠壓事件的場合中幫助完成系統故障分析。

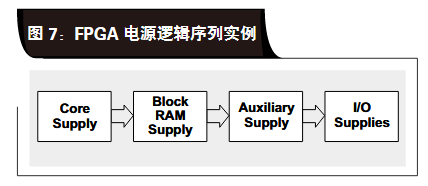

FPGA 排序要求實例諸如 Xilinx 或 Altera 等 FPGA 供應商在其產品手冊中提供了推薦或要求的上電序列,這些產品手冊可以很容易地在線查閱。不同的供應商之間、同一家供應商的不同FPGA 系列之間的排序要求存在差異。

另外,在產品手冊中還羅列了針對電源斜坡上升和關斷的定時要求。推薦的斷電序列通常是上電序列的倒序。圖 7 示出了上電排序的一個實例。

結論

可以運用多種電源排序解決方案來滿足 FPGA 供應商所規定的要求。除了上電和斷電排序之外,系統要求可能還包括電源監視,但是針對 FPGA 的最優電源解決方案將取決于系統的復雜性與規格參數。

-

電源

+關注

關注

185文章

18313瀏覽量

255431 -

FPGA設計

+關注

關注

9文章

428瀏覽量

27210

原文標題:詳解 FPGA 電源排序的四種方案

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

詳解FPGA電源排序的四種方案

技術 | 詳解 FPGA 電源排序的四種方案

技術 | 詳解 FPGA 電源排序的四種方案

評論