去耦電容的有效使用方法

去耦電容有效使用方法的要點大致可以分為兩種。

本文就以下三點中的“要點1”進行介紹,請大家繼續期待今后的文章。

● 要點1:使用多個去耦電容

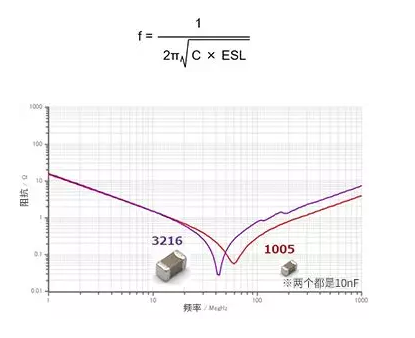

● 要點2:降低電容的ESL(等效串聯電感)

● 其他注意事項

要點1:使用多個去耦電容

去耦電容的有效使用方法之一是用多個(而非1個)電容進行去耦。使用多個電容時,使用相同容值的電容時和交織使用不同容值的電容時,效果是不同的。

使用多個容值相同的電容時

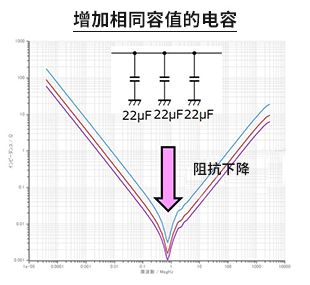

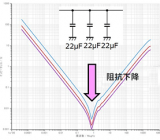

下圖是使用1個22μF的電容時(藍色)、增加1個變為2個時(紅色)、再增加1個變為3個(紫色)時的頻率特性。

如圖所示,當增加容值相同的電容后,阻抗在整個頻率范圍均向低的方向轉變,也就是說阻抗越來越低。

這一點可通過思考并聯連接容值相同的電容時,到諧振點的容性特性、取決于ESR(等效串聯電阻)的諧振點阻抗、諧振點以后的ESL(等效串聯電感)影響的感性特性來理解。

并聯的電容容值是相加的,所以3個電容為66μF,容性區域的阻抗下降。

諧振點的阻抗是3個電容的ESR并聯,因此為,假設這些電容的ESR全部相同,則ESR減少至1/3,阻抗也下降。

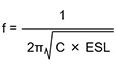

諧振點以后的感性區域的ESL也是并聯,因此為,假設3個電容的ESL全部相同,則ESL減少至1/3,阻抗也下降。

由此可知,通過使用多個相同容值的電容,可在整個頻率范圍降低阻抗,因此可進一步降低噪聲。

使用多個容值不同的電容時

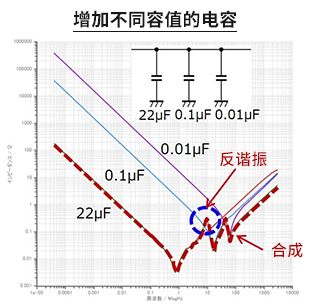

這些曲線是在22μF的電容基礎上并聯增加0.1μF、以及0.01μF的電容后的頻率特性。

通過增加容值更小的電容,可降低高頻段的阻抗。相對于一個22μF電容的頻率特性來說,0.1μF和0.01μF的特性是合成后的特性(紅色虛線)。

這里必須注意的是,有些頻率點產生反諧振,阻抗反而增高,EMI惡化。反諧振發生于容性特性和感性特性的交叉點。

所增加電容的電容量,一般需要根據目標降噪頻率進行選型。

另外,在這里給出的頻率特性波形圖是理想的波形圖,并未考慮PCB板的布局布線等引起的寄生分量。在實際的噪聲對策中,需要考慮寄生分量的影響。下一篇文章將介紹第2個要點。

關鍵要點:

去耦電容的有效使用方法有兩個要點:

①使用多個電容

②降低電容的ESL。

使用多個電容時,容值相同時和不同時的效果不同。

-

阻抗

+關注

關注

17文章

970瀏覽量

47117 -

頻率

+關注

關注

4文章

1559瀏覽量

60123 -

去耦電容

+關注

關注

11文章

319瀏覽量

22856

發布評論請先 登錄

分享去耦電容的有效使用方法和應用

分享去耦電容的有效使用方法和應用

評論