Zynq MPSoC(多處理器片上系統(tǒng))是Xilinx公司推出的第二代SoC系列產(chǎn)品,集成了復(fù)雜的處理系統(tǒng),包括ARM Cortex-A53應(yīng)用程序處理器和ARM Cortex-R5實(shí)時(shí)處理器,以及FPGA可編程邏輯。

來(lái)自蘇格蘭斯特拉斯克萊德大學(xué)(University of Strathclyde)的Louise Crockett團(tuán)隊(duì)基于這一平臺(tái)的軟件和硬件結(jié)構(gòu),撰寫(xiě)了Exploring Zynq MPSoC: With PYNQ and Machine Learning Applications,綜合且全面地介紹了軟件堆棧、多處理器處理系統(tǒng)以及可編程硬件陣列等問(wèn)題。

本書(shū)既是使用Zynq MPSoC的開(kāi)發(fā)人員的實(shí)用指南,同樣也是希望熟悉器件及其相關(guān)設(shè)計(jì)方法的技術(shù)人員的有效參考。

程序員可以學(xué)會(huì)如何使用簡(jiǎn)單的軟件界面和框架來(lái)快速實(shí)現(xiàn)他們的機(jī)器學(xué)習(xí)算法,系統(tǒng)設(shè)計(jì)師可以利用它來(lái)獲取系統(tǒng)的最高性能。

器件的架構(gòu)

與Zynq7000相比,Zynq MPSoC 進(jìn)一步整合了處理器系統(tǒng)中可選擇的處理器數(shù)量和性能,最多可配備四個(gè)ARM Cortex-A53處理器內(nèi)核和兩個(gè)ARM Cortex-R5實(shí)時(shí)處理器內(nèi)核。此外,該架構(gòu)進(jìn)一步拓展了可編程邏輯門(mén)陣列中的DSP切片和分布式存儲(chǔ)器的規(guī)模。在開(kāi)發(fā)當(dāng)今新興的AI應(yīng)用程序時(shí),全新的MPSoC架構(gòu)將實(shí)現(xiàn)繁瑣的算術(shù)計(jì)算和數(shù)據(jù)移動(dòng)的過(guò)程變得十分輕松有趣。

設(shè)計(jì)工具與方法

SoC系統(tǒng)將包括硬件設(shè)計(jì)和軟件設(shè)計(jì)兩個(gè)方面。硬件設(shè)計(jì)會(huì)映射到SoC設(shè)備上的FPGA邏輯資源,而軟件則運(yùn)行在一個(gè)或多個(gè)系統(tǒng)內(nèi)部署的處理器上。在此設(shè)計(jì)流程中,硬件和軟件開(kāi)發(fā)可以在很大程度上獨(dú)立進(jìn)行,然后整合。工程師使用他們選擇的工具生成硬件系統(tǒng)的元素,并使用Xilinx Vivado開(kāi)發(fā)環(huán)境實(shí)現(xiàn)系統(tǒng)集成和實(shí)現(xiàn)目標(biāo)設(shè)備。軟件開(kāi)發(fā)人員可以使用Xilinx軟件開(kāi)發(fā)工具包(SDK)進(jìn)行開(kāi)發(fā)。這是傳統(tǒng)的軟硬件協(xié)同設(shè)計(jì)方法。

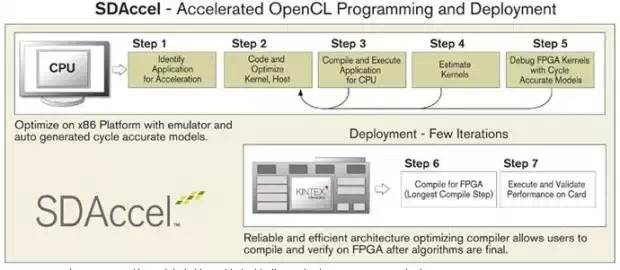

Xilinx的SDx開(kāi)發(fā)環(huán)境則是一種更高級(jí)的開(kāi)發(fā)方式。在Xilinx SDx工具中可以完全使用軟件代碼對(duì)整個(gè)系統(tǒng)進(jìn)行描述,然后對(duì)各種計(jì)算進(jìn)行資源分配(在用戶指導(dǎo)下)。這使得面向軟件的軟硬件協(xié)同設(shè)計(jì)已經(jīng)發(fā)生了相當(dāng)大的轉(zhuǎn)變。本書(shū)的第4章中更詳細(xì)地討論了關(guān)于SDx設(shè)計(jì)方法。

更先進(jìn)的應(yīng)用實(shí)現(xiàn)

本書(shū)還討論了Zynq上許多應(yīng)用程序的實(shí)現(xiàn),包括FINN-R開(kāi)源框架的有效性神經(jīng)網(wǎng)絡(luò)的實(shí)現(xiàn)、基于Python的Zynq設(shè)備框架和機(jī)器學(xué)習(xí)應(yīng)用程序。我們可以預(yù)見(jiàn)到一些基于Zynq的更為優(yōu)秀的產(chǎn)品,包括高級(jí)駕駛員輔助系統(tǒng)(ADAS),計(jì)算機(jī)視覺(jué),“大數(shù)據(jù)”分析等。

-

處理器

+關(guān)注

關(guān)注

68文章

19819瀏覽量

233685 -

賽靈思

+關(guān)注

關(guān)注

33文章

1796瀏覽量

132143 -

應(yīng)用程序

+關(guān)注

關(guān)注

38文章

3322瀏覽量

58770

發(fā)布評(píng)論請(qǐng)先 登錄

:“玩轉(zhuǎn)FPGA 賽靈思(xilinx)FPGA設(shè)計(jì)大賽”獲獎(jiǎng)獎(jiǎng)品展示

FPGA是用altera多還是賽靈思的多呢

如何利用賽靈思28納米工藝加速平臺(tái)開(kāi)發(fā)?

什么是賽靈思豐富目標(biāo)設(shè)計(jì)平臺(tái)?

如何利用ZYNQ MPSoC玩DOOM?

詳解賽靈思All Programmable Smarter Vision解決方案

從賽靈思FPGA設(shè)計(jì)流程看懂FPGA設(shè)計(jì)

賽靈思 Zynq UltraScale+ MPSoC 上的 Xen 管理程序教程

賽靈思與戴姆勒聯(lián)袂開(kāi)發(fā)AI解決方案

賽靈思最新發(fā)布的UltraScale+16nm系列FPGA、3D IC和MPSoC介紹

賽靈思的目標(biāo)和發(fā)展

賽靈思MPSoC開(kāi)發(fā)教程詳解

賽靈思MPSoC開(kāi)發(fā)教程詳解

評(píng)論