目前,在高層次綜合(HLS, High Level Synthesis)領域,Vivado HLS可謂獨樹一幟。它有效地拉近了軟件工程師與FPGA之間的距離,加速了算法開發(fā)的進程,縮短了產品上市時間。對于工程師,尤其是軟件工程師而言是一個福音。在實際工程中,如何利用好這一工具仍值得考究。本文將介紹使用Vivado HLS時的幾個誤區(qū)。

誤讀1:只要是 C/C++ 描述的算法都是可綜合(可轉換成 RTL)的。

HLS的可綜合功能是有限的,并不是所有的C或者C++語句都可轉換成相應的RTL代碼。下面這些情形是不可綜合的。

○ 動態(tài)內存分配

○涉及操作系統(tǒng)層面的操作

○遞歸函數(shù)

○數(shù)組規(guī)模可變

誤讀2:既然Vivado HLS支持C、C++和System C,那么用三者任意一種都行。

盡管 Vivado HLS支持C、C++和System C,但支持力度是不一樣的。在v2017.4版本ug871 第56頁有如下描述。可見,當設計中如果使用到任意精度的數(shù)據(jù)類型時,采用C++ 和System C 是可以使用Vivado HLS的調試環(huán)境的,但是C 描述的算法卻是不可以的。而實際上很多真實的硬件模型都要使用任意進度的數(shù)據(jù)類型,所以要想使用Vivado HLS 的調試功能, 建議最好采用 C++和System C。

誤讀3:只要有源代碼即可,沒有Test bench也行。

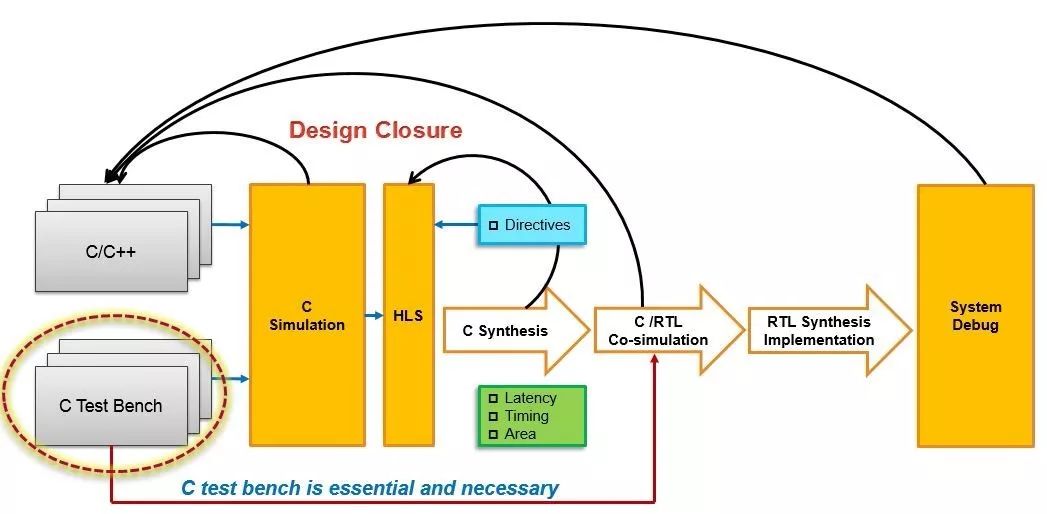

在HLS設計開發(fā)中,C Test bench起著舉足輕重的作用。C層面算法功能的驗證需要用到它;當生成RTL代碼時,C和RTL的協(xié)同仿真也要用到它。如下圖所示。實際上,協(xié)同仿真時,RTL代碼的輸入激勵就是由C Test bench生成的。由此可見,C Test bench是整個設計不可或缺的一部分。

-

C++

+關注

關注

22文章

2119瀏覽量

75289 -

源代碼

+關注

關注

96文章

2953瀏覽量

68359

發(fā)布評論請先 登錄

探索Vivado HLS設計流,Vivado HLS高層次綜合設計

vivado HLS 綜合錯誤

請問如何只下載Vivado HLS 2015.2

來自vivado hls的RTL可以由Design Compiler進行綜合嗎?

Vivado HLS許可證問題如何解決

Vivado HLS設計流的相關資料分享

Hackaday讀者有話說:Vivado HLS使用經(jīng)驗分享

用Vivado-HLS實現(xiàn)低latency 除法器

如何創(chuàng)建Vivado HLS項目

如何使用Tcl命令語言讓Vivado HLS運作

UltraFast Vivado HLS方法指南

將VIVADO HLS設計移植到CATAPULT HLS平臺

關于Vivado HLS錯誤理解

關于Vivado HLS錯誤理解

評論