賽靈思 Zynq-7000 All Programmable SoC 系列代表了嵌入式設(shè)計(jì)的新局面,為嵌入式系統(tǒng)工程設(shè)計(jì)群體帶來前所未有的高性能和靈活性。這些產(chǎn)品在單個(gè)器件上集成了特性豐富的雙核 ARM Cortex-A9 MPCore 處理系統(tǒng)和賽靈思可編程邏輯。3,000 多個(gè)互聯(lián)點(diǎn)將片上處理系統(tǒng) (PS) 與片上可編程邏輯 (PL) 相連,使兩個(gè)片上系統(tǒng)之間的性能達(dá)到了任何雙芯片處理器 FPGA 都無法匹敵的高度。賽靈思在 2011 年發(fā)布這款 Zynq SoC 器件時(shí),便立即得到了很多精通硬件設(shè)計(jì)語言和方法以及嵌入式軟件開發(fā)的嵌入式系統(tǒng)工程師和架構(gòu)師的追捧。如今,首款 Zynq SoC 已被用于無線基礎(chǔ)設(shè)施、智能工廠和智能視頻/視覺等多種嵌入式應(yīng)用領(lǐng)域,并且快速成為高級駕駛員輔助系統(tǒng)約定俗成的標(biāo)準(zhǔn)平臺。

為了讓這款性能卓越的器件能夠被具有很強(qiáng)軟件背景但沒有 HDL 經(jīng)驗(yàn)的嵌入式工程師所用,賽靈思在今年年初推出了基于 Eclipse 的 SDSoC 集成開發(fā)環(huán)境,使軟件工程師能夠?qū)?Zynq SoC 中的可編程邏輯和 ARM 處理系統(tǒng)進(jìn)行編程。

我們仔細(xì)了解一下 Zynq SoC [1] 的特性以及軟件工程師如何利用 SDSoC 環(huán)境來創(chuàng)建用任何其他“處理器+FPGA”系統(tǒng)均無法實(shí)現(xiàn)的系統(tǒng)設(shè)計(jì)。為進(jìn)行研究,我們將使用包含一個(gè) Zynq Z-7020-1 器件的賽靈思 ZC702 評估板 [2] 作為硬件平臺。

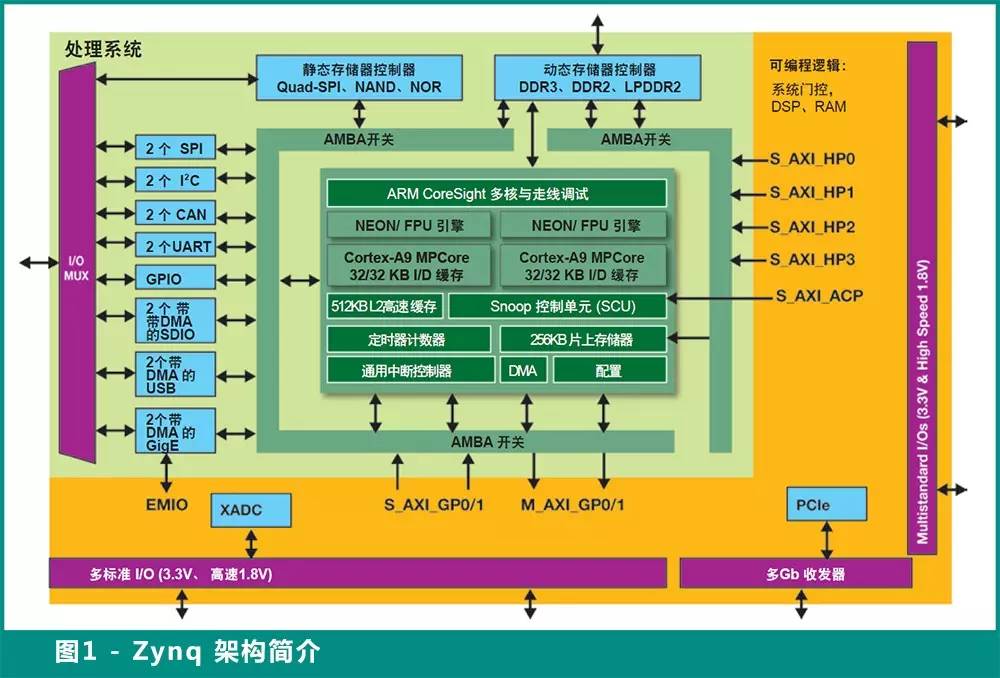

如圖 1 所示,Zynq SoC 包含兩大功能模塊:PS(包含應(yīng)用處理器單元、存儲器接口、外設(shè)和互聯(lián))和 PL(傳統(tǒng)的 FPGA 架構(gòu))。

PS 和 PL 通過與 ARM AMBA AXI4 接口兼容的互聯(lián)鏈路緊密耦合在一起。四個(gè)高性能 (HP) AXI4 接口端口將 PL 連接到 PS 中的異步 FIFO 接口 (AFI) 模塊,從而在 PL和 PS 存儲器系統(tǒng)(DDR 和片上存儲器)之間提供一條高吞吐量的數(shù)據(jù)路徑。AXI4 加速器一致性端口 (ACP) 允許直接從 PL 主設(shè)備對 L1 和 L2 高速緩存進(jìn)行低時(shí)延的一致性訪問。通用 (GP) 端口包含可從 PS 和 PL 訪問的低性能通用端口。

在傳統(tǒng)的以硬件設(shè)計(jì)為核心的流程中,通過使用賽靈思的 Vivado Design Suite 在 Zynq SoC 上設(shè)計(jì)嵌入式系統(tǒng)大致需要四個(gè)步驟:

系統(tǒng)架構(gòu)師確定硬件-軟件分區(qū)方案。計(jì)算密集型算法最適合硬件。特性分析結(jié)果是鑒別性能瓶頸以及在數(shù)據(jù)移動成本與加速優(yōu)勢之間進(jìn)行權(quán)衡研究的基礎(chǔ)。

硬件工程師處理被分到硬件中的功能,并將它們轉(zhuǎn)換或設(shè)計(jì)成 IP 核,例如,用 Vivado 取代 VHDL 或 Verilog ;用 Vivado 高層次綜合 (HLS) 實(shí)現(xiàn) C/C++ 高層次綜合[3],或者用 Vivado System Generator for DSP 實(shí)現(xiàn)模型化設(shè)計(jì) [4]。

然后,工程師使用 Vivado IP Integrator [5]創(chuàng)建整個(gè)嵌入式系統(tǒng)的模塊化設(shè)計(jì)。整個(gè)系統(tǒng)的開發(fā)需要用到不同的數(shù)據(jù)移動工具(AXI-DMA、AXI Memory Master、AXI-FIFO 等),以及連接 PL IP 與 PS 的AXI 接口(GP、HP 和 ACP)。一旦 IP Integrator 中所有設(shè)計(jì)規(guī)則檢查都通過,就可將項(xiàng)目導(dǎo)出至賽靈思軟件開發(fā)套件 (SDK) [6]。

軟件工程師使用賽靈思 SDK 開發(fā)針對 PS 中 ARM處理器的驅(qū)動程序和應(yīng)用。

最近幾年,賽靈思對 Vivado Design Suite 的簡便易用性實(shí)現(xiàn)了顯著提高,該套件能夠讓工程師縮短 IP 開發(fā)時(shí)間以及 IP 模塊連接步驟(上述步驟 2 以及步驟 3 的部分內(nèi)容)。就 IP 開發(fā)而言,采用這些最新設(shè)計(jì)技術(shù)(例如在 Vivado HLS 工具中實(shí)現(xiàn) C/C++ 高層次綜合;用 Vivado System Generator for DSP 實(shí)現(xiàn)模型化設(shè)計(jì))可以顯著縮短開發(fā)和驗(yàn)證時(shí)間,同時(shí)讓設(shè)計(jì)團(tuán)隊(duì)能夠使用高層次抽象探索更大的架構(gòu)范圍。對于使用 VHDL 或 Verilog 需要數(shù)周才能完成的設(shè)計(jì),利用新型工具只需數(shù)天就能完成。

SDSoC 環(huán)境會自動安排所有必要的賽靈思工具,以生成針對 Zynq SoC 的完整軟硬件系統(tǒng),而且所需的用戶介入程度很小。

賽靈思通過 Vivado IP Integrator 可進(jìn)一步強(qiáng)化流程。Vivado Design Suite 的這個(gè)功能使設(shè)計(jì)人員只需要在圖形用戶界面 (GUI) 中連接 IP 模塊,就可以設(shè)計(jì)復(fù)雜的硬件系統(tǒng)(嵌入式或非嵌入式),從而實(shí)現(xiàn)快速的硬件系統(tǒng)集成。

新的 Vivado Design Suite 功能可幫助設(shè)計(jì)與開發(fā)團(tuán)隊(duì)簡化 Zynq SoC 的使用。但對于以硬件為中心的優(yōu)化流程而言,要縮短探索不同數(shù)據(jù)移動工具和 PS-PL接口(步驟 3 的一部分)以及寫入和調(diào)試驅(qū)動程序與應(yīng)用(步驟 4)所需的開發(fā)時(shí)間,辦法并不多。如果整個(gè)系統(tǒng)不能滿足吞吐量、時(shí)延或占位面積等方面的設(shè)計(jì)要求,那么設(shè)計(jì)團(tuán)隊(duì)不得不修改步驟 3 中的系統(tǒng)連接,以重構(gòu)硬件架構(gòu)。這些修改會不可避免地導(dǎo)致步驟 4 中的軟件應(yīng)用發(fā)生變化。有些情況下,加速不足或者硬件利用率過高會迫使開發(fā)團(tuán)隊(duì)重新考慮最初的軟硬件分區(qū)。多個(gè)硬件和軟件團(tuán)隊(duì)將不得不再次反復(fù)設(shè)計(jì)系統(tǒng),以探索可能滿足最終要求的其他架構(gòu)。

這些實(shí)例表明手動進(jìn)行系統(tǒng)優(yōu)化對上市時(shí)間的影響。系統(tǒng)優(yōu)化對于緊密集成的系統(tǒng)(例如 Zynq SoC)很關(guān)鍵,因?yàn)槠款i經(jīng)常發(fā)生在 PS 與 PL 之間的系統(tǒng)連接上。

SDSoC 環(huán)境能大大簡化 Zynq SoC 開發(fā)過程,可將步驟 2、3、4 實(shí)現(xiàn)高度自動化,以縮短總開發(fā)時(shí)間。該開發(fā)環(huán)境會生成必要的硬件和軟件組件,用以同步硬件和軟件并保存源程序語義,同時(shí)支持任務(wù)級并行處理和流水線化的通信與計(jì)算,從而實(shí)現(xiàn)高性能。SDSoC 環(huán)境會自動安排所有必要的賽靈思工具(Vivado、IP Integrator、HLS 和 SDK),以生成針對Zynq SoC 的完整軟硬件系統(tǒng),而且所需的用戶介入程度很小。

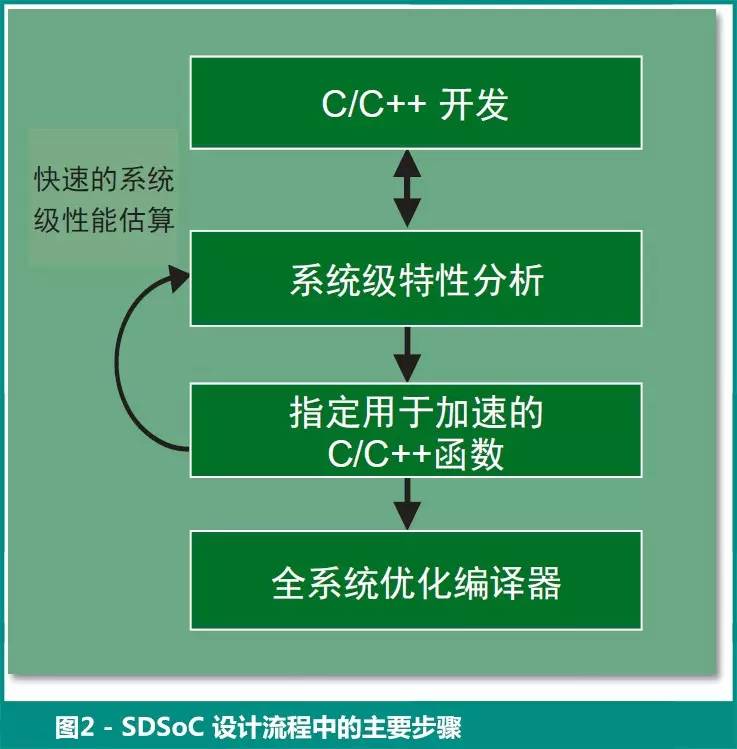

假設(shè)我們已有一個(gè)針對 PS 的完全用 C/C++ 描述的應(yīng)用,而且已經(jīng)決定將哪些功能分配到 PL 以實(shí)現(xiàn)加速,那么 SDSoC 開發(fā)流程大致按照如下所示(圖2):

SDSoC 環(huán)境使用快速估算流程(通過調(diào)用內(nèi)含的Vivado HLS)構(gòu)建應(yīng)用項(xiàng)目。這樣在數(shù)分鐘內(nèi)就能大致估算出性能和資源情況。

如果我們認(rèn)為有必要,我們會用適當(dāng)?shù)闹噶顑?yōu)化 C/C++ 應(yīng)用和硬件功能,并重新運(yùn)行估算直到實(shí)現(xiàn)所需的性能和占位面積。

然后,SDSoC 環(huán)境構(gòu)建整個(gè)系統(tǒng)。該過程會生成完整的 Vivado Design Suite 項(xiàng)目和比特流,以及一個(gè)針對 Linux、FreeRTOS 或裸機(jī)的可引導(dǎo)的運(yùn)行時(shí)間軟件映像。

用 SDSOC 環(huán)境進(jìn)行硬件 VS 軟件的性能估算

線性代數(shù)幾乎在任何工程領(lǐng)域中都是基礎(chǔ)而強(qiáng)大的工具,能夠計(jì)算求解具有多維變量的方程組。例如,工程師可將線性控制理論系統(tǒng)描述為“狀態(tài)”和“狀態(tài)變換”矩陣。圖像的數(shù)字信號處理是線性代數(shù)的另一個(gè)典型應(yīng)用。尤其是,通過 Cholesky 分解進(jìn)行矩陣求逆被認(rèn)為是求解方程組或矩陣求逆的最有效的方法之一。現(xiàn)在讓我們仔細(xì)看一看 32 位浮點(diǎn)實(shí)際數(shù)據(jù) 64 x 64 矩陣的 Cholesky 分解,并作為 Zynq SoC 上軟硬件分區(qū)的應(yīng)用實(shí)例。

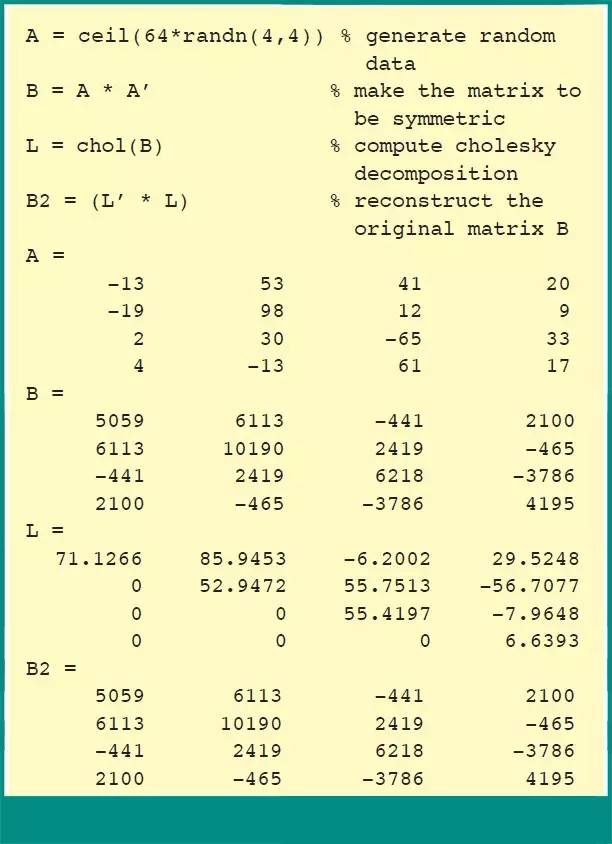

Cholesky 分解將正定矩陣變換為具有嚴(yán)格正對角線的下三角和上三角矩陣的乘積。矩陣 B 在三角矩陣 L 中分解,即 B = L’ * L,其中 L’ 是 L 的轉(zhuǎn)置矩陣,如下面的 4 x 4 矩陣 MATLAB 代碼所示:

選擇加速器很簡單,只需在 SDSoC 環(huán)境的圖形用戶界面 (GUI) 中用鼠標(biāo)點(diǎn)擊特定功能即可。

讓我們看看如何估算應(yīng)用設(shè)計(jì)的性能和資源利用率,而且無需經(jīng)過整個(gè)構(gòu)建周期。

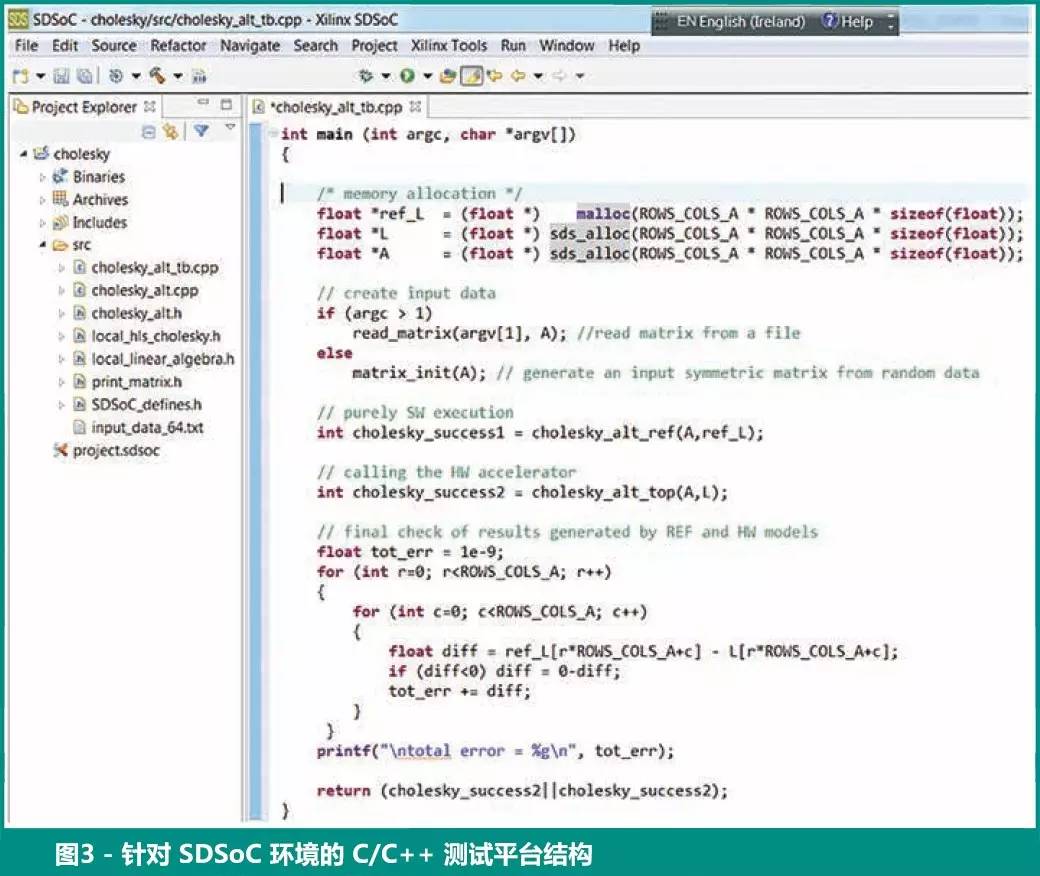

圖 3 給出了適合 SDSoC 環(huán)境的測試平臺結(jié)構(gòu)。主程序?yàn)樗锌站仃嚪峙鋭討B(tài)存儲器并填入數(shù)據(jù)(從文件中讀入或者隨機(jī)生成)。然后,主程序調(diào)用參考軟件函數(shù)和硬件備選函數(shù)。最后,主程序檢查兩個(gè)函數(shù)計(jì)算出的數(shù)值結(jié)果以測試有效正確性。

注意,這里針對每個(gè)輸入/輸出數(shù)組使用了一個(gè)名為sds_alloc 的專用存儲分配器,以讓 SDSoC 環(huán)境自動在硬件加速器的每個(gè) I/O 端口之間插入一個(gè) Simple DMA IP;相比之下,malloc 則實(shí)例化一個(gè) Scatter-Gather DMA,用以處理分布在物理地址空間中多個(gè)非連續(xù)頁面上的數(shù)組。Simple DMA 從占位面積和性能開銷上將要比 Scatter-Gather DMA 廉價(jià),但需要 sds_alloc 獲得物理上的連續(xù)存儲空間。

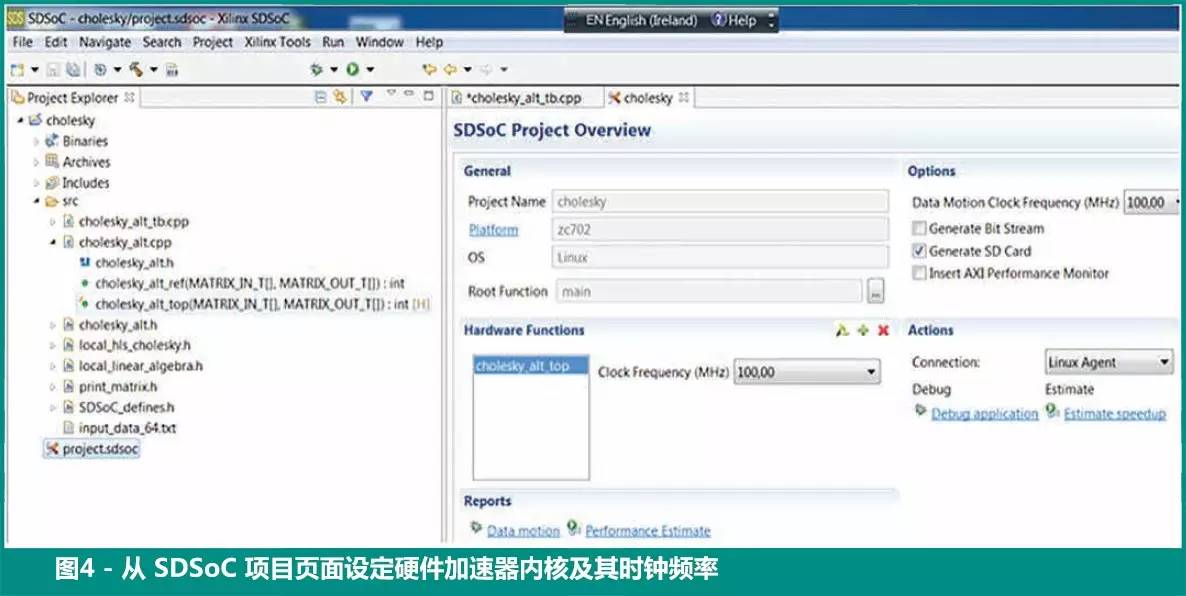

選擇加速器很簡單,只需在 SDSoC 環(huán)境的圖形用戶界面 (GUI) 中用鼠標(biāo)點(diǎn)擊特定功能即可。如圖 4 所示,例程 cholesky_alt_top 標(biāo)記為 “H”,以表明它將被送到硬件加速器。我們還可以為加速器和數(shù)據(jù)移動內(nèi)核選擇時(shí)鐘頻率(如圖 4 的 SDSoC 項(xiàng)目頁面中所示為 100 MHz)。

現(xiàn)在,我們可以啟動“估算加速”過程。在經(jīng)過幾分鐘的編譯后,我們就可以在 Vivado 項(xiàng)目中生成所有內(nèi)核和數(shù)據(jù)移動網(wǎng)絡(luò)。SDSoC 環(huán)境還生成一個(gè) SD 卡映像,其中包含 Linux 引導(dǎo)映像,里面有 FPGA 比特流以及純軟件版本的二進(jìn)制應(yīng)用程序。我們從這個(gè) SD卡引導(dǎo),并在 ZC702 目標(biāo)平臺上運(yùn)行應(yīng)用。

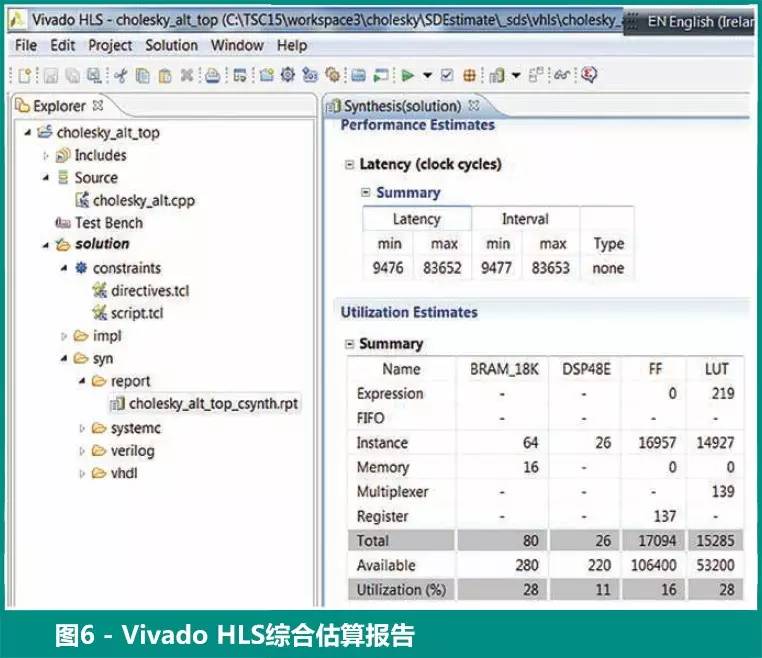

Linux 在開發(fā)板上啟動之后,我們可執(zhí)行純軟件應(yīng)用,然后,SDSoC 環(huán)境生成圖 5 中的性能估算報(bào)告。如果在硬件中而非軟件中執(zhí)行,我們可看到 cholesky_alt_top 函數(shù)的 FPGA 資源利用率 (26 DSP、80 BRAM、 15,285 LUT、17,094 FF) 和性能加速 (1.75)。

在主應(yīng)用程序方面,我們還可以看到總體加速比較低 (1.23),原因在于其他軟件開銷,例如 malloc 和數(shù)據(jù)傳輸。我們的整個(gè)應(yīng)用比較小,主要在于展示 SDSoC 流程和設(shè)計(jì)方法;我們需要在 PL 中加速更多例程,但這超出了本文的范疇。

使用 SDSoC 環(huán)境,只要幾分鐘就能生成該信息,且無需綜合和布局布線這樣的 FPGA 編譯過程;這些過程根據(jù)硬件系統(tǒng)的復(fù)雜程度可能需要數(shù)小時(shí)才能完成。這樣的估算通常足以用來分析硬件-軟件分區(qū)的系統(tǒng)級性能,并讓用戶能夠迅速進(jìn)行設(shè)計(jì)迭代以創(chuàng)建出最佳系統(tǒng)。

了解性能估算結(jié)果

當(dāng) SDSoC 開發(fā)環(huán)境針對估算加速進(jìn)程編譯應(yīng)用代碼時(shí),會生成一個(gè)中間目錄 (圖 5 中的_sds),用來放置所有中間項(xiàng)目(Vivado HLS、Vivado IP Integrator 等)。它會特別在源代碼中插入對自由運(yùn)行的 ARM 性能計(jì)數(shù)器函數(shù) sds_clock_counter() 的調(diào)用,以測量程序函數(shù)中關(guān)鍵部分的執(zhí)行時(shí)間。這也就是為什么目標(biāo)板需要在估算加速進(jìn)程中與SDSoC 環(huán)境的 GUI 連接。圖 5 中報(bào)告的所有數(shù)字都在運(yùn)行執(zhí)行過程中用這些計(jì)數(shù)器測量得到。唯一的例外是硬件加速函數(shù),該函數(shù)直到整個(gè) FPGA 構(gòu)建(包括布局布線)完成后才存在。不過,Vivado HLS 會在有效 Vivado HLS 的綜合步驟過程中在估算資源利用率的同時(shí)計(jì)算硬件加速函數(shù)的估算周期數(shù)。

假設(shè)備選硬件加速器函數(shù)以 FHW MHz 時(shí)鐘頻率運(yùn)行,并需要 CKHW 個(gè)時(shí)鐘周期完成整個(gè)計(jì)算(這是時(shí)延概念),并且假設(shè)在 ARM CPU 執(zhí)行時(shí),函數(shù)在 FARM MHz 時(shí)鐘頻率下占用 CKARM 個(gè)周期,那么,如果計(jì)算時(shí)間相同,硬件加速器就能實(shí)現(xiàn)與 ARM CPU 相同的性能,即 CKHW / FHW= CKARM / FARM。從這個(gè)公式中我們得到 CKARM = CKHW*FARM / FHW。這代表加速器能為處理器分擔(dān)的最大時(shí)鐘周期數(shù)量,以展示將函數(shù)遷移到硬件而獲得的加速效果。

圖 6 中報(bào)告了 Vivado HLS 綜合估算結(jié)果。注意,硬件加速器時(shí)延為 CKHW = 83,652 個(gè)周期,時(shí)鐘頻率 FHW = 100-MHz。在 ZC702板 中,F(xiàn)ARM = 666 MHz,而且 CKARM = CKHW*FARM / FHW = 83,653*666/100 = 557,128,獲得的硬件加速效果與圖 5 中 SDSoC 環(huán)境報(bào)告的 565,554 個(gè)周期達(dá)到了很好的匹配。這就是為什么 SDSoC 環(huán)境能估算加速器所需的時(shí)鐘周期數(shù)量而又不需要進(jìn)行實(shí)際的布局布線。

用 SDSOC 環(huán)境構(gòu)建硬件-軟件系統(tǒng)

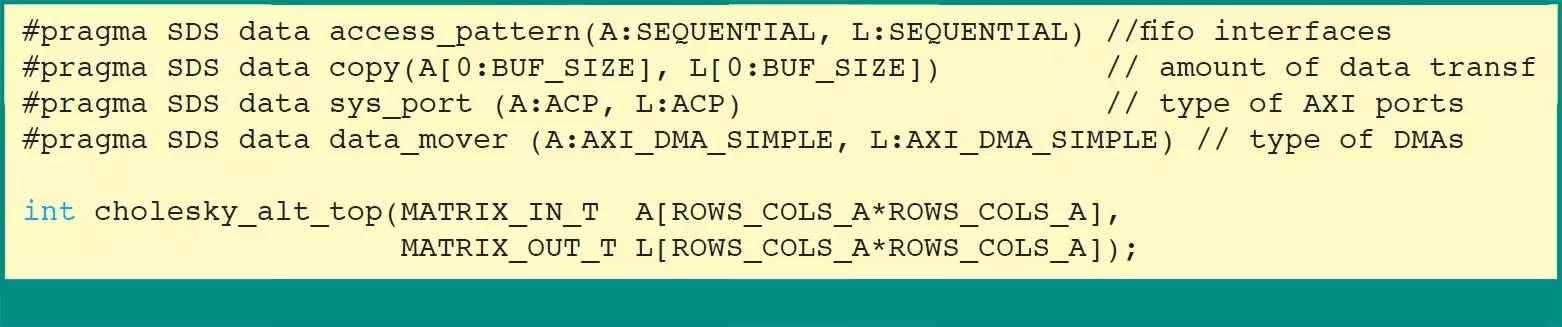

在確定硬件加速有效果之后,我們可以用 SDSoC 環(huán)境實(shí)現(xiàn)整個(gè)硬件和軟件系統(tǒng)。我們需要做的是添加正確的指令(以 Pragma 命令的形式)來分別指定 FIFO 接口(由于 I/O 陣列的連續(xù)掃描);在運(yùn)行時(shí)針對任何加速器調(diào)用而需傳送的數(shù)據(jù)量;連接 PL 中的 IP 核與 PS 的 AXI 端口類型;以及數(shù)據(jù)移動工具的類型。下面的 C/C++ 代碼表明了這些指令的使用。注意,實(shí)際情況下最后的指令不需要,原因是 SDSoC 環(huán)境會因 sds_alloc 的使用而實(shí)例化一個(gè) Simple DMA;我們在這里提到它只是為了說清楚。

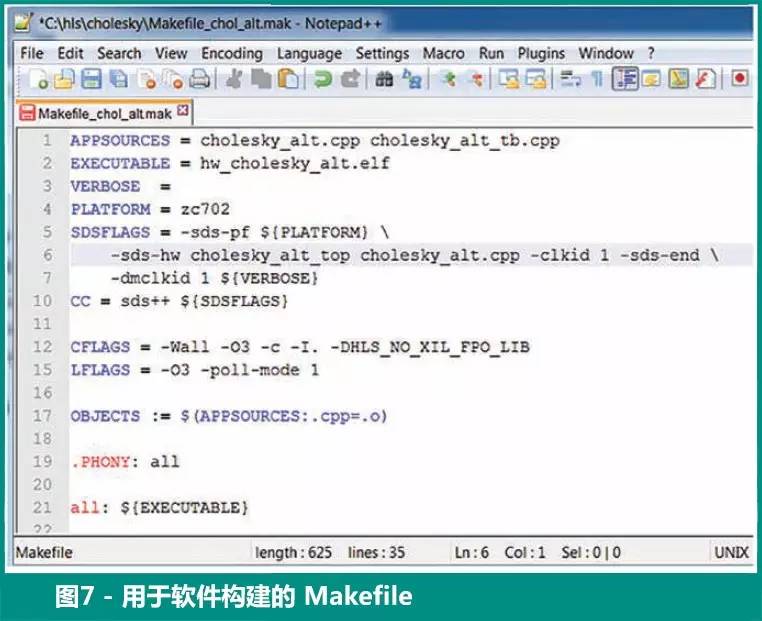

我們可以在 SDSoC 環(huán)境的 GUI 中直接在 Release 配置中構(gòu)建項(xiàng)目,或者,也可使用圖 7 中的 Makefile 并從 SDSoC 工具命令語言 (Tcl) 解釋器中啟動。不管是Vivado Design Suite 中的什么工具,設(shè)計(jì)人員都可以采用 GUI 或 Tcl 腳本。為了提高加速效果,我們將硬件加速器的時(shí)鐘頻率增加至 FHW =142 MHz(通過-clkid 1 makefile 標(biāo)志設(shè)置)。

FPGA 編譯完成后不到半個(gè)小時(shí),我們就得到對ZC702 板進(jìn)行編程的比特流以及在 Linux OS 上執(zhí)行的可執(zhí)行連接文件 (ELF) 格式文件。然后,我們在ZC702 板上測量性能:純軟件時(shí)是 995,592 個(gè)周期,有硬件加速時(shí)是 402,529 個(gè)周期。因此,cholesky_alt_top 函數(shù)的有效性能提升 2.47。

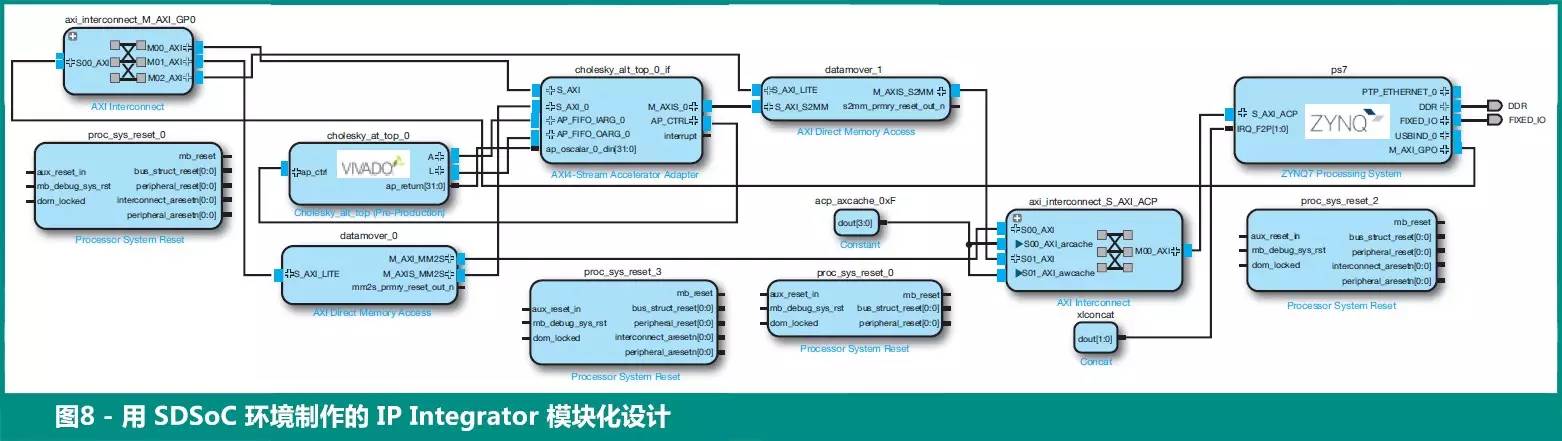

圖 8 給出了整個(gè)嵌入式系統(tǒng)的方框圖;SDSoC 環(huán)境將 Vivado IP Integrator 方框圖以 HTML 文件報(bào)告的形式給出,以使其易于閱讀(圖 9)。該報(bào)告清楚顯示,硬件加速器通過簡單 AXI4-DMA 連接 ACP 端口,而通用端口用來通過 AXI4-Lite 接口設(shè)置加速器。

在嵌入式系統(tǒng)啟動并運(yùn)行時(shí),我們需要花多長時(shí)間為 ZC702 板生成 SD 卡?我們需要一個(gè)工作日來編寫適合 Vivado HLS 和 SDSoC 環(huán)境的 C++ 測試平臺,然后,用一個(gè)小時(shí)進(jìn)行實(shí)驗(yàn)以從 Linear Algebra HLS Library 中獲得好的結(jié)果,再用一個(gè)小時(shí)的時(shí)間通過SDSoC 環(huán)境創(chuàng)建嵌入式系統(tǒng)(FPGA 編譯過程)。這個(gè)過程共需要 10 個(gè)小時(shí)。我們估算手動完成所有這些工作(步驟 3 用 Vivado IP Integrator,步驟 4 用賽靈思SDK)至少需要兩周的辛苦工作,這還不算高效使用這些工具所需的時(shí)間。

FPGA 編譯完成后不到半個(gè)小時(shí),我們就得到對 ZC702 板進(jìn)行編程的比特流以及在 Linux OS 上執(zhí)行的 ELF 格式文件。

SDSoC 開發(fā)環(huán)境使更多嵌入式系統(tǒng)和軟件開發(fā)人員能夠憑借熟悉的嵌入式 C/C++ 開發(fā)經(jīng)驗(yàn)針對 Zynq SoC 開展工作。包括業(yè)界首款 C/C++ 全系統(tǒng)優(yōu)化編譯器的 SDSoC 環(huán)境提供系統(tǒng)級特性分析、可編程邏輯中的自動軟件加速、自動系統(tǒng)連接生成和庫,以加快開發(fā)速度。

-

嵌入式系統(tǒng)

+關(guān)注

關(guān)注

41文章

3630瀏覽量

129792 -

加速器

+關(guān)注

關(guān)注

2文章

809瀏覽量

38115 -

賽靈思

+關(guān)注

關(guān)注

32文章

1794瀏覽量

131549

發(fā)布評論請先 登錄

相關(guān)推薦

AMD 面向嵌入式系統(tǒng)推出高能效 EPYC 嵌入式 8004 系列

【「嵌入式Hypervisor:架構(gòu)、原理與應(yīng)用」閱讀體驗(yàn)】+全文學(xué)習(xí)心得

研華嵌入式工控機(jī) ARK 系列:結(jié)構(gòu)緊湊,低功耗、高擴(kuò)展

專家力薦|《嵌入式系統(tǒng)原理與開發(fā)——基于RISC-V和Linux系統(tǒng)》新書發(fā)售

嵌入式熱門領(lǐng)域有哪些?

OPSL 優(yōu)勢1:波長靈活性

Altera SOPC 嵌入式系統(tǒng)設(shè)計(jì)(一)

思瑞浦發(fā)布高性能運(yùn)算放大器TPA267x系列

8芯M16公頭如何提升靈活性

簡談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

簡談Xilinx Zynq-7000嵌入式系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

嵌入式可編程片上系統(tǒng)是什么

英特爾銳炫A系列顯卡為客戶提供了強(qiáng)大的性能和靈活性

賽靈思系列為嵌入式系統(tǒng)工程設(shè)計(jì)群體帶來高性能和靈活性

賽靈思系列為嵌入式系統(tǒng)工程設(shè)計(jì)群體帶來高性能和靈活性

評論