All Programmable 技術(shù)和器件的全球領(lǐng)先企業(yè)賽靈思公司(Xilinx, Inc. (NASDAQ:XLNX))開始投片業(yè)界首款全可編程(All Programmable)多處理器SoC(MPSoC),采用臺積公司(TSMC)16nm FF+工藝,并瞄準ADAS、無人駕駛汽車、工業(yè)物聯(lián)網(wǎng)(I-IoT)和5G無線系統(tǒng)等嵌入式視覺系統(tǒng)開發(fā)。All Programmable Zynq UltraScale+MPSoC將系統(tǒng)級性能功耗比提升了5倍、支持任意連接,并提供新一代系統(tǒng)所需要的安全性和保密性。

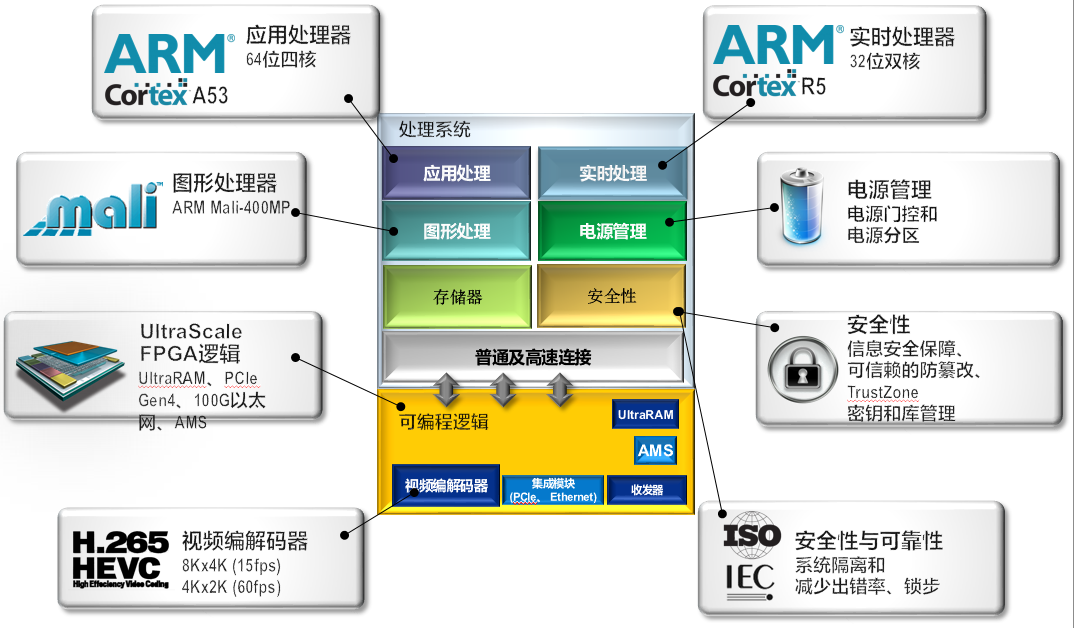

作為全球首款異構(gòu)多處理SoC,該新型器件集成了7個用戶可編程處理器,其中包括一個四核64位ARM Cortex-A53應(yīng)用處理器、一個雙核32位ARM Cortex-R5實時處理器和一個ARM Mali-400圖形處理器。Zynq UltraScale+ MPSoC系列還包括諸多集成式外設(shè),并具備安全和保密功能,以及高級電源管理功能。結(jié)合最近推出的SDSoC開發(fā)環(huán)境,該最新系列器件既能支持軟件定義的系統(tǒng),還可支持硬件優(yōu)化的系統(tǒng)。

圖:Zynq UltraScale+ MPSoC系統(tǒng)特性

“面向新一代智能互聯(lián)應(yīng)用,Zynq UltraScale+ MPSoC提供了完美的軟件智能、硬件優(yōu)化、安全性與保密性、任意連接等功能組合。Zynq UltraScale+ MPSoC經(jīng)過量身定制,致力于滿足ADAS、無人駕駛汽車、工業(yè)物聯(lián)網(wǎng)和5G無線系統(tǒng)等新一代嵌入式視覺系統(tǒng)開發(fā)的獨特需求,并可運用于眾多其他應(yīng)用。”

——Victor Peng,賽靈思公司執(zhí)行副總裁兼可編程產(chǎn)品部總經(jīng)理

實現(xiàn)ADAS、工業(yè)物聯(lián)網(wǎng)和5G系統(tǒng)等嵌入式視覺系統(tǒng)

Zynq UltraScale+ MPSoC專為包括工業(yè)機器視覺、監(jiān)控和汽車ADAS系統(tǒng)等在內(nèi)的新一代嵌入式視覺系統(tǒng)量身定制。針對ADAS應(yīng)用,Zynq MPSoC將高度并行化的硬件圖像處理和分析加速功能與基于軟件的算法配置和控制功能緊密結(jié)合在一起。通過UltraRAM增加視頻緩沖所需的擴充內(nèi)存,吞吐量實現(xiàn)了最大化,同時時延得以縮短;這都是ADAS的重要屬性。

最后,為實現(xiàn)實時的安全關(guān)鍵對策決策并初始化執(zhí)行機構(gòu)命令,可讓有雙內(nèi)核Cortex-R5引擎的Zynq MPSoC ARM工作在鎖步模式下,同時在可編程架構(gòu)中加入交叉監(jiān)測和診斷保護投票功能。Zynq MPSoC早在設(shè)計過程中就考慮到了汽車行業(yè)ISO-26262功能安全標準要求,同時提供了一個可擴展的高度可定制的可編程平臺,讓客戶的設(shè)計能夠在快速變化的ADAS應(yīng)用領(lǐng)域中滿足未來需求。

對工業(yè)物聯(lián)網(wǎng)來說,Zynq UltraScale+ MPSoC系列是集成數(shù)據(jù)采集的理想選擇,執(zhí)行實時診斷,并支持智能互聯(lián)控制系統(tǒng)的本地決策。MPSoC處理子系統(tǒng)、UltraScale可編程邏輯架構(gòu)以及新型UltraRAM片上存儲器技術(shù)完美組合在一起,創(chuàng)建出了一個理想的平臺,不僅可處理大量的分析數(shù)據(jù),還能管理實時機器對機器(M2M)通信。此外,憑借專用的安全處理單元和經(jīng)配置可用于鎖步的雙核Cortex-R5引擎,Zynq MPSoC還可滿足SIL3等級的功能性安全與保密性要求。

Zynq UltraScale+ MPSoC器件可滿足新一代5G系統(tǒng)不斷提高的無線電和基帶處理要求,比如支持新型“大規(guī)模MIMO”與自適應(yīng)波束成形架構(gòu)、CloudRAN L1基帶加速及相關(guān)去程應(yīng)用,而且能夠在顯著降低功耗的同時靈活支持多種標準和多種頻帶。具備四核ARM Cortex-A53處理子系統(tǒng)的Zynq UltraScale+ MPSoC充分利用集成式高精度電源管理系統(tǒng),可實現(xiàn)低功耗最佳軟/硬件組合設(shè)計方案,從而輕松處理數(shù)字預(yù)失真、波束成形控制功能以及系統(tǒng)管理任務(wù)。

Zynq UltraScale+ MPSoC開發(fā)環(huán)境

賽靈思還為UltraScale+產(chǎn)品組合配套提供了極為全面的早期試用工具集,其中包括:

能夠?qū)崿F(xiàn)完整軟件定義開發(fā)的SDSoC開發(fā)環(huán)境

最新版Vivado設(shè)計套件能幫助硬件設(shè)計人員快速打造最佳Zynq MPSoC平臺

賽靈思還提供源碼,以支持Linux、FreeRTOS、OpenAMP、Yocto、QEMU以及XEN等開源社區(qū)

配套提供了賽靈思的軟件開發(fā)套件(SDK)、PetaLinux工具、運行時間驅(qū)動程序以及各種庫,有助于簡化應(yīng)用的開發(fā)。

關(guān)于賽靈思

賽靈思是All Programmable器件、SoC和3D IC的全球領(lǐng)先供應(yīng)商,其行業(yè)領(lǐng)先的產(chǎn)品與新一代設(shè)計環(huán)境以及IP核完美地整合在一起,可滿足客戶對可編程邏輯乃至可編程系統(tǒng)集成的廣泛需求。

-

處理器

+關(guān)注

關(guān)注

68文章

19831瀏覽量

233877 -

開發(fā)環(huán)境

+關(guān)注

關(guān)注

1文章

239瀏覽量

17059 -

四核處理器

+關(guān)注

關(guān)注

1文章

78瀏覽量

17887

發(fā)布評論請先 登錄

貿(mào)澤開售Xilinx Zynq UltraScale+雙核與四核多處理器SoC

異構(gòu)多處理器系統(tǒng)Cache一致性解決方案

多處理器分組實時調(diào)度算法

基于NiosII的SOPC多處理器系統(tǒng)設(shè)計方法

Xilinx宣布投片業(yè)界首款All Programmable多處理器SoC 采用TSMC 16nm FF+工藝并瞄準嵌入式視覺、ADAS、I

All programmable SoC的技術(shù)和應(yīng)用

什么是同步多處理器

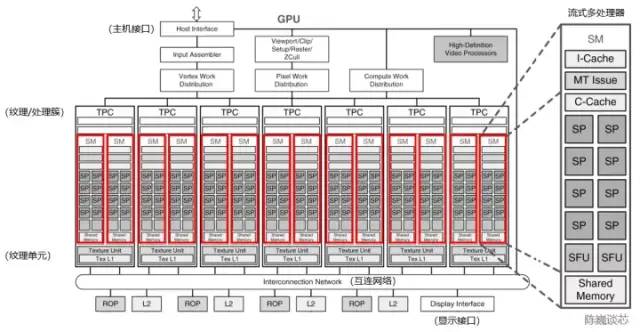

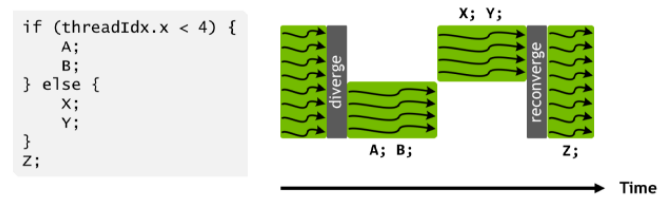

GPGPU流式多處理器架構(gòu)剖析(上)

GPGPU流式多處理器架構(gòu)剖析(下)

為Xilinx? Zynq?UltraScale?系列多處理器中的VCCINT_VCU軌供電

Xilinx投片All Programmable多處理器SoC

Xilinx投片All Programmable多處理器SoC

評論