FPGA實現(xiàn)一個三回合打地鼠游戲機

ASIC 課程設(shè)計,用 FPGA 實現(xiàn)一個三回合打地鼠游戲機。

(b站處女作竟然是課程設(shè)計 emm....

如何通過FPGA實現(xiàn)深度卷積網(wǎng)絡(luò)(3)

卷積神經(jīng)網(wǎng)絡(luò)具有表征學(xué)習(xí)(representation learning)能力,能夠按其階層結(jié)構(gòu)對輸....

BadApple_FPGA的安裝步驟

部分步驟:安裝Ubuntu虛擬機,編譯Uboot、設(shè)備樹、內(nèi)核,構(gòu)建根文件系統(tǒng),移植u-boot與l....

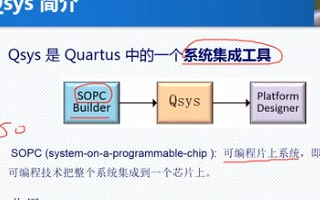

Nios II處理器的體系結(jié)構(gòu)及Avalon總線接口規(guī)范

軟核演練篇包含了哪些內(nèi)容:該篇以什么是軟核、什么是Qsys、如何構(gòu)建一個Qsys系統(tǒng)為切入點,在該基....

FPGA之狀態(tài)機練習(xí):設(shè)計思路(4)

狀態(tài)機由狀態(tài)寄存器和組合邏輯電路構(gòu)成,能夠根據(jù)控制信號按照預(yù)先設(shè)定的狀態(tài)進行狀態(tài)轉(zhuǎn)移,是協(xié)調(diào)相關(guān)信號....