Zynq上的非對稱多核處理器

Zynq SoC 還擁有大量共享資源,常見示例包括 I/O 外設、片上存儲器、中斷控制器分配器、L2....

SystemVerilog包的簡介與使用

最初的Verilog語言沒有一個可用于多個模塊的定義。每個模塊都必須有任務、函數、常量和其他共享定義....

Vitis HLS的基礎知識科普

VitisHLS是一種高層次綜合工具,支持將C、C++和OpenCL函數硬連線到器件邏輯互連結構和R....

介紹幾個關于ISP算法架構的項目

用python實現的ISP架構,整體項目架構不如OpenISP,但是有幾個算法是OpenISP沒有的....

匠人精神是怎么用在FPGA存儲器

FPGA之所以有這樣的能力,是由它本身的結構決定的。比如FPGA有著很強的硬件并行性,能像GPU那樣....

SystemVerilog為工程師定義新的數據類型提供了一種機制

為了使源代碼更易于閱讀和維護,typedef名稱應該使用一種命名約定,使名稱明顯代表用戶自定義類型。....

通過無線wifi下載調試fpga的一種方法

上邊是整個框圖,主要的數據流是Vivado通過PC上的WIFI鏈接到WIFI路由器上,然后對同一個局....

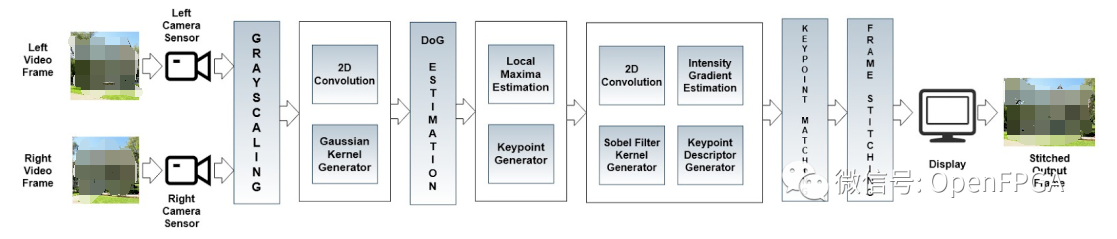

幾個視頻/圖像處理的項目分享

F-I-L是一個FPGA平臺的開源的圖像處理庫,已經擁有了許多常用操作,并在不斷更新中。這些操作被以....

使用Xilinx Vivado創建自己板卡文件

board.xml - 定義關于板的所有信息。它包括基本信息(例如電路板名稱、描述、供應商)、有關板....

介紹幾個脈沖神經網絡的開源項目

ODIN 是一種在線學習數字脈沖神經處理器,在 2019 年發表在IEEE Transactions....

網絡和變量的未壓縮數組

數組的維度定義了數組可以存儲的元素總數。未壓縮的數組可以用任意數量的維度聲明,每個維度存儲指定數量的....

DMA控制器介紹及示例演示詳解

我們上一節談到使用 DMA(直接內存訪問)的好處已經變得顯而易見。到了這一步,我們留下了人類長期以來....

Verilog/FPGA開源項目卷積神經網絡

CNN 是多層感知器的正則化版本。多層感知器通常表示全連接網絡,即一層中的每個神經元都連接到下一層中....

離散端口的語法和使用指南

SystemVerilog提供用于聲明端口列表和端口聲明的編碼樣式:組合樣式、傳統樣式和具有組合類型....

ZYNQ:使用PL將任務從PS加載到PL端

ARM 的 AXI 是一種面向突發的協議,旨在提供高帶寬同時提供低延遲。每個 AXI 端口都包含獨立....

數字硬件建模SystemVerilog-網絡

每個SystemVerilog網絡類型都有特定的語義規則,這些規則會影響多個驅動程序的解析方式。雖然....

RTL級的基本要素和設計步驟

頂層設計:RTL設計推薦使用自頂而下的設計方法,因為這種設計方法與模塊規劃的順序一致,而且更有利于進....

SystemVerilog常用可綜合IP模塊庫

了解決這個復雜的問題,設計了這個庫,它可以幫助您簡化設計流程。使用一些簡單的 API 可以輕松地在測....

了解Zynq SoC的私有看門狗定時器

每個A9處理器都有私有的32位定時器和32位看門狗定時器。兩個處理器共享一個64位定時器。這些定時器....

從算法到RTL實現的問題

我們首先要根據實際需求,針對某方面的信號處理問題,做一個鏈路級或模塊級快速仿真驗證設計。最常見的比如....

什么是張量處理單元(TPU)

該項目的目的是創建一個與谷歌的張量處理單元具有相似架構的機器學習協處理器。該實現的資源可定制,可以以....

“軟核”硬做-ODrive(FPGA版本)

核心CPU是XX32FXXX,在工業控制領域其實FPGA占比也很大,所以能不能用FPGA做一個ODr....

System Verilog-文本值

文本整數值是一個整數,沒有小數點。(IEEE 1800 SystemVerilog標準使用術語“整數....

Perl語言在代碼自動生成中的應用實例

Verilog 有什么奇技淫巧?我想最重要的是理解其硬件特性。Verilog HDL語言僅是對已知硬....

Zynq SoC 設備上的多種用途

這篇博文特別關注 Zynq SoC 的多用途 IO (MIO, Multipurpose IO) 模....

SystemVerilog對硬件功能如何進行建模

本文定義了通常用于描述使用SystemVerilog對硬件功能進行建模的詳細級別的術語。