基于FPGA IP核的線性調(diào)頻信號(hào)脈沖壓縮(3)

利用ModelSim仿真軟件首先對(duì)程序代碼進(jìn)行時(shí)序功能仿真,完成邏輯的綜合與實(shí)現(xiàn)之后再進(jìn)行布局布線后仿真,此時(shí)的仿真已基本接近真實(shí)情況。綜合后的仿真情況如圖7所示,仿真結(jié)果表明軟件運(yùn)行正常,可實(shí)現(xiàn)線性調(diào)頻信號(hào)的脈沖壓縮。

2.4 測(cè)試數(shù)據(jù)分析

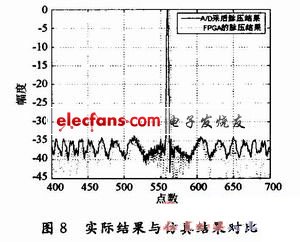

完成程序編制及仿真之后,把軟件加載至FPGA中進(jìn)行全面測(cè)試。通過(guò)Chipscope軟件可以采集到A/D之后的I/Q線性調(diào)頻基帶信號(hào)數(shù)據(jù)以及經(jīng)過(guò)FPGA處理后的脈壓數(shù)據(jù),把A/D后采集到的數(shù)據(jù)放在Matlab中進(jìn)行理想的脈沖壓縮,與實(shí)際FPGA的脈壓結(jié)果進(jìn)行對(duì)比。從圖8中可以看出,兩種處理的結(jié)果是一致的,主副瓣比大約都在35 dB左右,主瓣寬度也基本相同。如圖8所示。

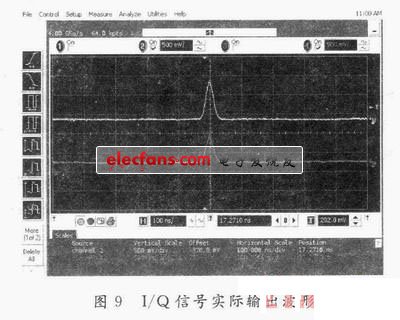

脈沖壓縮系統(tǒng)軟、硬件調(diào)試完畢之后,通過(guò)板上的D/A輸出可以直接監(jiān)測(cè)脈沖壓縮后的I/Q信號(hào)波形,如圖9所示。

3 結(jié)語(yǔ)

本文主要介紹了一種利用FPGA IP核設(shè)計(jì)線性調(diào)頻信號(hào)脈沖壓縮的方法,通過(guò)各種仿真與實(shí)際測(cè)試表明脈沖壓縮結(jié)果正確。這種基于IP核的模塊化設(shè)計(jì)方法非常靈活,參數(shù)的設(shè)置和修改方便,大大縮減了設(shè)計(jì)的開(kāi)發(fā)周期。需要注意的是,雖然IP核的內(nèi)部結(jié)構(gòu)和實(shí)現(xiàn)功能已經(jīng)固定,但設(shè)計(jì)時(shí)也要結(jié)合算法原理和IP核的自身特點(diǎn)綜合考慮,對(duì)參數(shù)進(jìn)行合理設(shè)置,以便獲得硬件資源和運(yùn)算速度的最優(yōu)化。

- 第 1 頁(yè):基于FPGA IP核的線性調(diào)頻信號(hào)脈沖壓縮(1)

- 第 2 頁(yè):系統(tǒng)硬件平臺(tái)#

- 第 3 頁(yè):工程軟件仿真#

本文導(dǎo)航

非常好我支持^.^

(0) 0%

不好我反對(duì)

(0) 0%

相關(guān)閱讀:

- [FPGA/ASIC技術(shù)] 圖像的二維提升小波變換的FPGA實(shí)現(xiàn) 2011-06-29

- [單片機(jī)] CAN總線控制器IP核代碼分析 2011-06-28

- [FPGA/ASIC技術(shù)] 基于FPGA的LCoS驅(qū)動(dòng)和圖像處理系統(tǒng)設(shè)計(jì) 2011-06-28

- [新品快訊] CAST推出新的視頻和圖像處理壓縮IP核 2011-06-28

- [FPGA/ASIC技術(shù)] IIS接口的FPGA實(shí)現(xiàn) 2011-06-24

- [電子常識(shí)] ARM、DSP、FPGA的區(qū)別 2011-06-23

- [新品快訊] 萊迪思和Flexibilis推出FPGA以太網(wǎng)交換IP核 2011-06-16

- [接口/總線/驅(qū)動(dòng)] 基于Wishbone總線的UART IP核設(shè)計(jì) 2011-06-10

( 發(fā)表人:葉子 )