您的位置:電子發(fā)燒友網(wǎng) > 電子技術(shù)應(yīng)用 > 嵌入式技術(shù) > FPGA/ASIC技術(shù) >

PLD設(shè)計(jì)速成(2)-采用原理圖設(shè)計(jì)三人表決器

2012年05月18日 15:46 來源:本站整理 作者:秩名 我要評(píng)論(0)

我們根據(jù)三人表決器的直值表,可以通過卡諾圖化簡可以得到:

L2=SW1SW2 SW1SW3 SW2SW3

L1=_L2

那么我們可以在MAX plusII中用原理圖實(shí)現(xiàn)上面的三人表決器

下面僅把和VHDL不同的詳細(xì)寫下,相同或基本相同的就一帶而過:

(1)打開MAX plusII

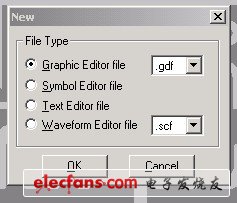

(2)新建一個(gè)圖形文件:File菜單>new

新建文件時(shí)選擇Graphic Editor file

點(diǎn)OK

(3)輸入設(shè)計(jì)文件

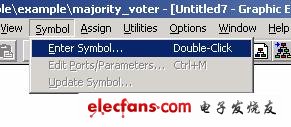

我們現(xiàn)在在圖形文件中輸入電路,我們這個(gè)電路需要AND2、OR3、NOT三個(gè)邏輯門電路和輸入輸出端,你可以

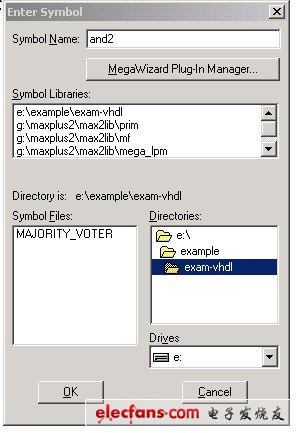

Symbol ->Enter Symbol(或者雙擊空白處)

彈出窗口:

在Symbol Name中輸入and2,點(diǎn)OK

同樣可以加入or3、input、output、not

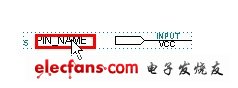

對(duì)input、output,鼠標(biāo)左鍵雙擊PIN_NAME,那么PIN_NAME被選中,并且變黑,然后輸入你要改的名字,如SW1

把元件拖動(dòng)到合適位置,將光標(biāo)放到元件的引線出,可以發(fā)現(xiàn)光標(biāo)變?yōu)槭中牵藭r(shí)摁住左鍵就可以進(jìn)行連線。

本文導(dǎo)航

- 第 1 頁:PLD設(shè)計(jì)速成(2)-采用原理圖設(shè)計(jì)三人表決器(1)

- 第 2 頁:最后的電路