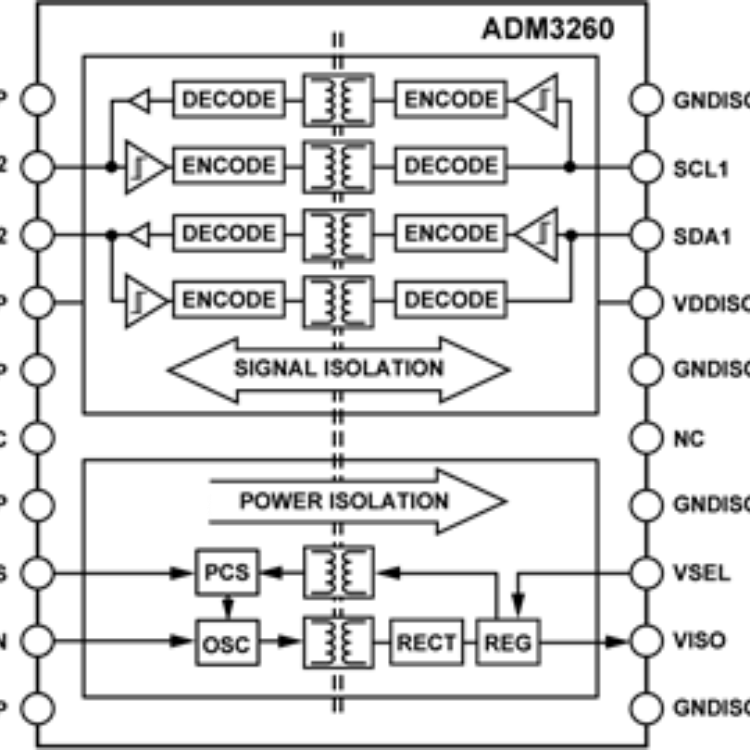

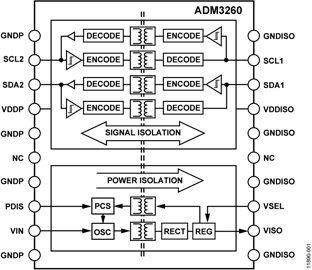

ADM3260基于iCoupler?和isoPower?芯片級變壓器技術,是一款支持熱插拔的數字和電源隔離器,集成兩路無閂鎖、雙向通信通道,提供完整的隔離式 I2C接口和集成式隔離DC-DC轉換器,支持最高150 mW隔離式電源轉換。

iCoupler是一種芯片級變壓器技術,其功能、性能、尺寸和功耗均優于光耦器件。擁有雙向I2C通道則無需將I2C信號分成單獨的發送信號與接收信號,供獨立光耦合器使用。

該片上隔離式 DC-DC轉換器基于ADI公司的isoPower?技術,可提供 3.15 V 至 5.25 V 隔離調節電壓,最大輸出功率 150 mW。

借助ADM3260,iCoupler 和 isoPower 通道以及 I2C 收發器可以與半導體電路集成,在小型封裝中實現完全隔離的 I2C 接口和電源轉換器。ADM3260 提供 20 引腳 SSOP 封裝,并具有 -40 ℃ 至 +105 ℃ 的工作溫度范圍。

- I2C、SMBus或PMBus接口隔離

- 多級I2C接口

- 中央交換

- 電信與數據通信設備

- -48 V分布式電源系統

- -48 V電源模塊

- 網絡

- isoPower的隔離式DC/DC轉換器

- 3.15 V或5.25 V調節輸出

- 輸出功率:最高150 mW

- 高共模瞬變抗擾度: >25 kV/<

- iCoupler的I2C數字隔離器

- 雙向I2C通信

- 3.0 V至5.5 V電源/邏輯電平

- 開漏接口

- 適合熱插拔應用

- 30 mA吸電流能力

- 1000 kHz工作頻率

- 20引腳SSOP封裝,爬電距離為5.3 mm

- 工作溫度最高可達: 105℃

ADUM3473

ADUM3474

ADUM6000

ADUM6200

ADUM6201

ADUM6202

LTM2881-3

LTM2881-5

ADUM6400

ADUM6401

ADUM6402

ADUM6403

ADUM6404

LTM2882-3

LTM2882-5

ADUM5000

ADUM5200

ADUM5201

ADUM5202

ADUM5400

ADUM5401

ADUM5402

ADUM5403

ADUM5404

ADUM5240

ADUM5241

ADUM5242