資料介紹

描述

這是一個由 5 部分組成的博客:

第 2 部分:在 Spartan 6 FPGA 上使用 Xilinx ISE 的組合邏輯

第 3 部分:在 Cyclone-IV FPGA 上使用 Quartus Prime 的順序邏輯

第 4 部分:在 Artix-7 FPGA 上使用 Vivado 的組合邏輯與順序邏輯

第 5 部分:最終項目 - DE0 Nano 開發板上的 Pong 游戲

目標:

比較和分析使用在 Artix-7 FPGA 上實現的組合邏輯和順序邏輯的移位器的性能

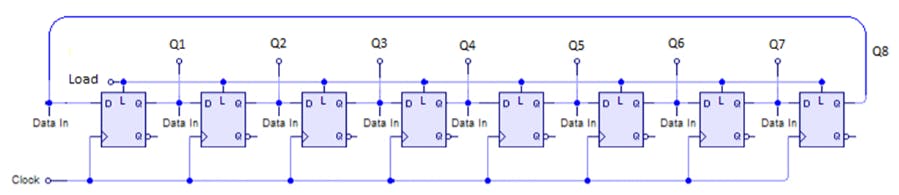

順序邏輯:移位寄存器

我們都知道什么是移位寄存器,以及為什么要使用它們——對寄存器中的位進行移位嗎?

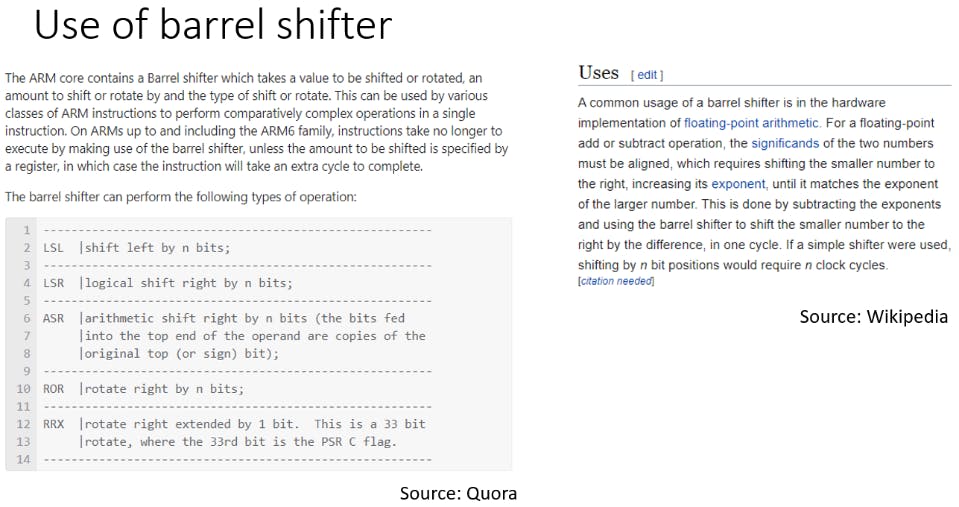

但是 CPU 或微控制器內部的應用程序非常廣泛,并且在算術和邏輯單元中發揮著至關重要的作用,尤其是在如今的 ARM 處理器中。

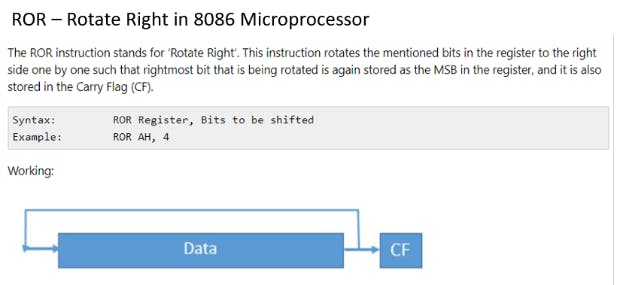

下面給出的設計專門用于右移。但為什么?此操作在老式8086微處理器中用于實現 ROR 指令。

8 位移位寄存器設計:

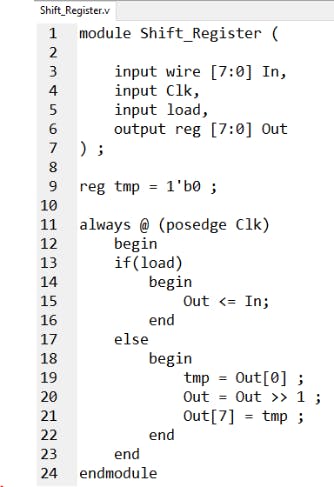

Verilog 實現:

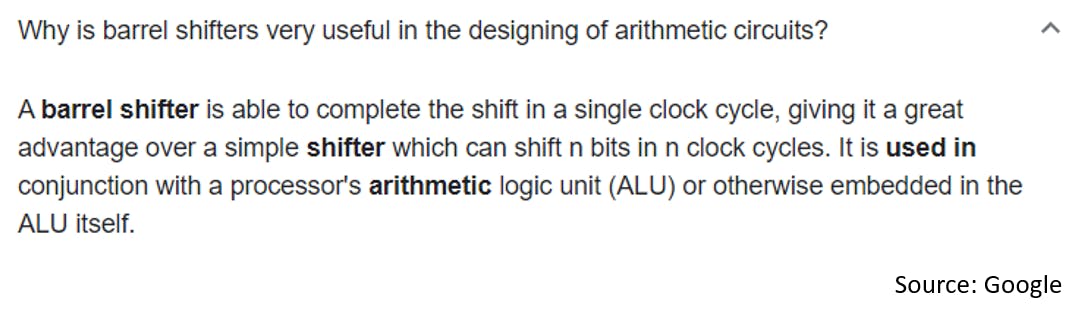

有沒有其他方法可以移動位?

- 是的,桶形移位器。

組合邏輯:桶形移位器

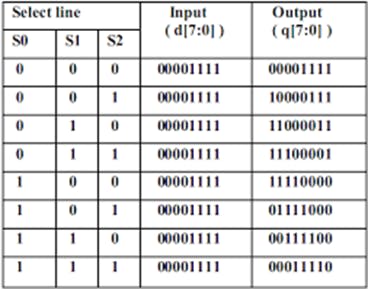

真值表:

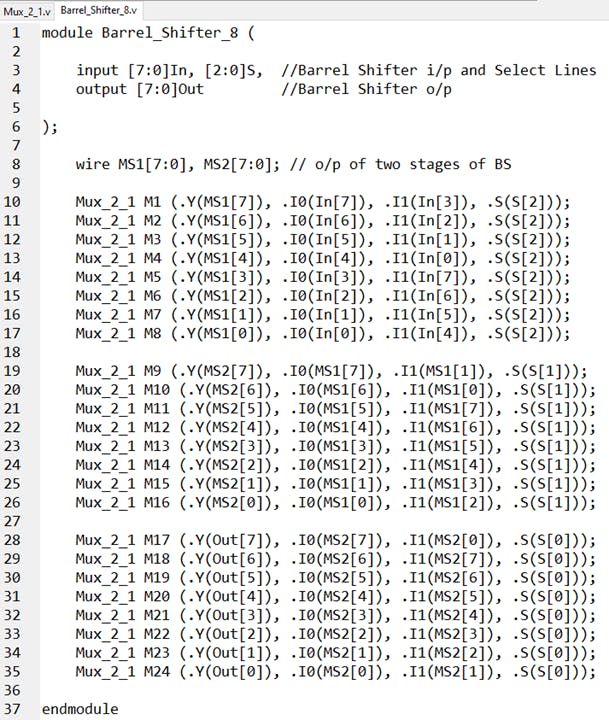

在這篇博客中,我將討論使用多路復用器的 8 位桶形移位器的設計和實現。

我要遵循的建模是 Verilog HDL 中的結構設計。

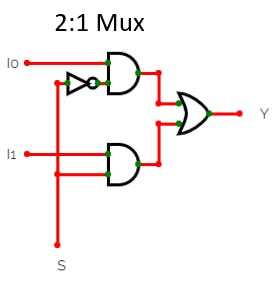

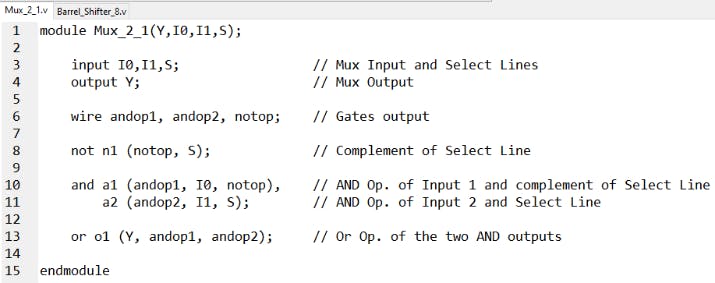

首先,讓我們設計一個 2:1 Mux

結構模型中 2:1 Mux 的 Verilog 代碼非常簡單,我們有 2 個與門、1 個非門和 1 個或門。

除了常規的輸入和輸出外,還為門輸出聲明了三根線,并根據結構進行連接。

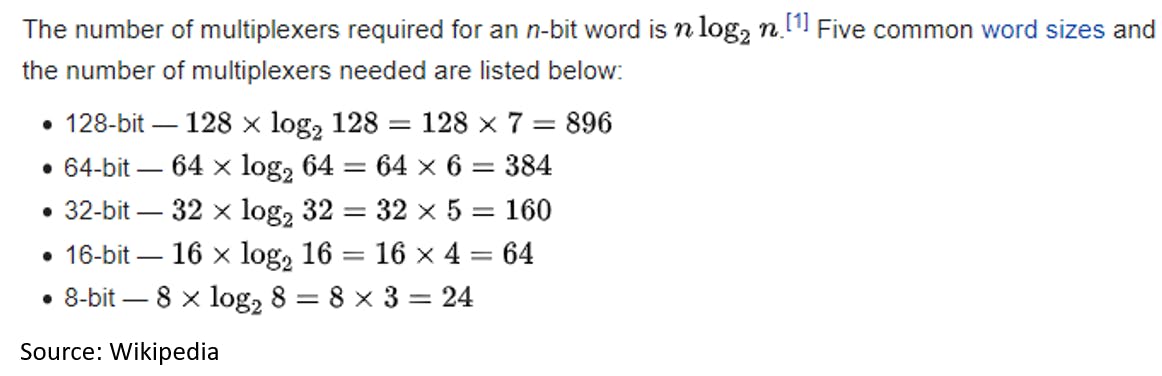

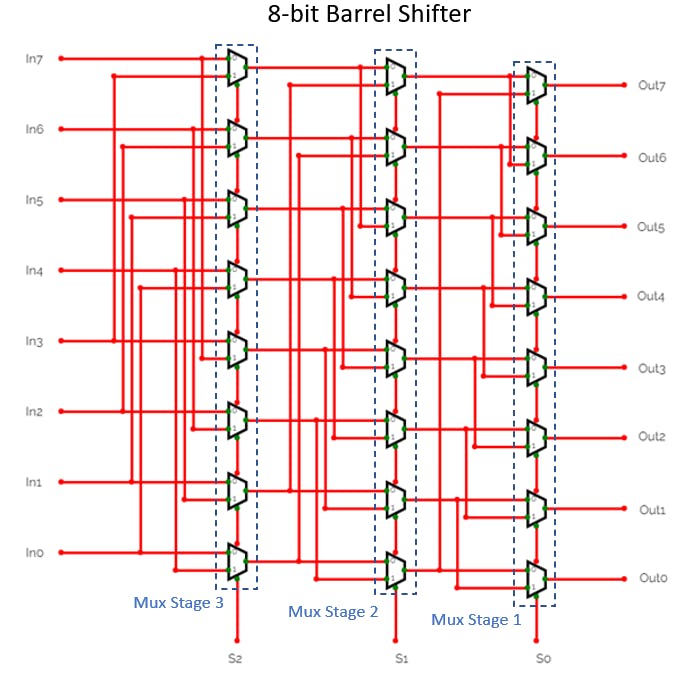

8位桶形移位器的設計:

通過使用結構設計,我們可以確保設計以我們想要的方式實現。

Verilog 實現:

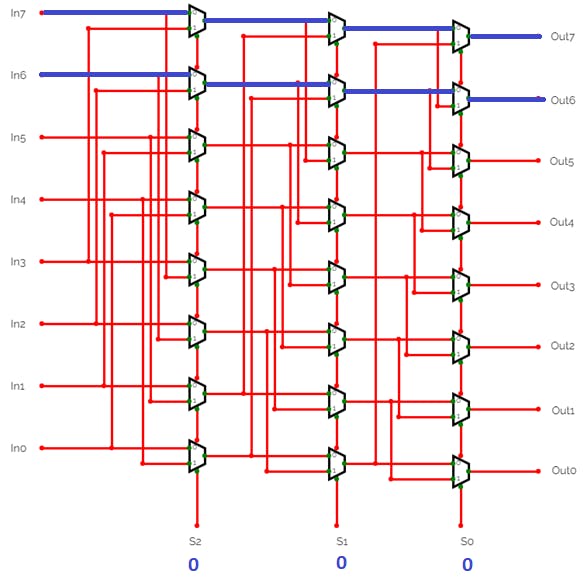

桶形移位器的工作:

這就是桶形移位器如何根據選擇線移動位。

在 Artix-7 FPGA 上的實現:

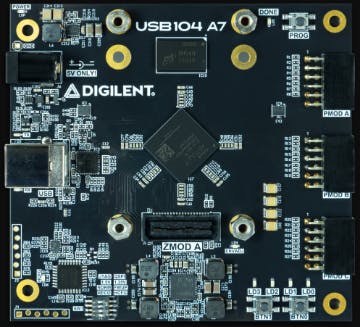

我將使用 USB104-A7 FPGA 開發板來實現。這是幾個月前的路試。在此處閱讀評論:USB104 A7:Artix-7 FPGA 開發板 - 評論

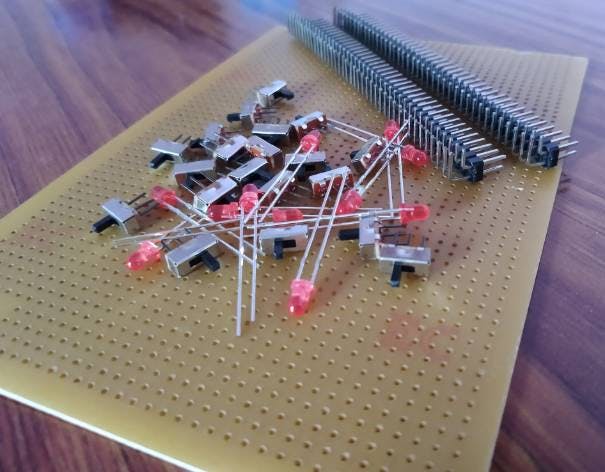

定制 Pmod 的制作:

由于按鈕和 LED 等用戶 I/O 外設非常少,因此要制造定制 Pmod(外設模塊)以實現數字設計。

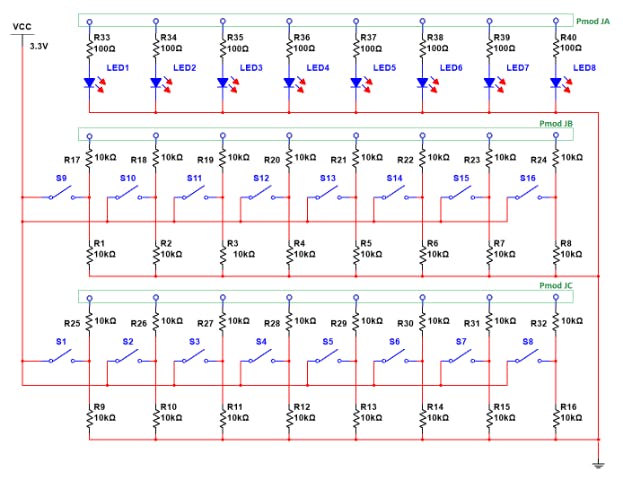

讓我們看一下制造的示意圖。

使用 NI Multisim 進行的設計:

從原理圖中可以看出,使用 10k 電阻器將用于上拉和下拉目的。

由于已經有一個 200 歐姆的電阻串聯到 Pmod GPIO 上,以防止意外將輸入驅動為輸出時損壞 FPGA,

僅 100 歐姆電阻與 LED 串聯使用。所有開關均處于高電平有效。電路圖如下:

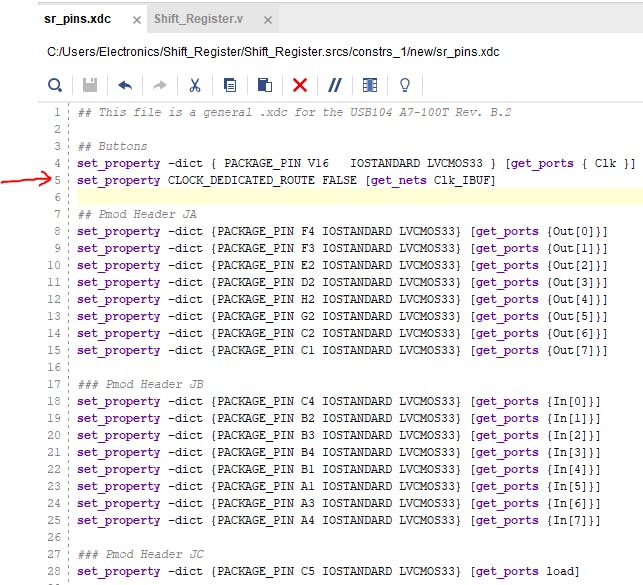

這是上面制作的 Pmod 的一般約束文件:

## Pmod Header JA

#set_property -dict { PACKAGE_PIN F4 IOSTANDARD LVCMOS33 } [get_ports { led[0] }]; #IO_L13P_T2_MRCC_35 Sch=ja[1]

#set_property -dict { PACKAGE_PIN F3 IOSTANDARD LVCMOS33 } [get_ports { led[1] }]; #IO_L13N_T2_MRCC_35 Sch=ja[2]

#set_property -dict { PACKAGE_PIN E2 IOSTANDARD LVCMOS33 } [get_ports { led[2] }]; #IO_L14P_T2_SRCC_35 Sch=ja[3]

#set_property -dict { PACKAGE_PIN D2 IOSTANDARD LVCMOS33 } [get_ports { led[3] }]; #IO_L14N_T2_SRCC_35 Sch=ja[4]

#set_property -dict { PACKAGE_PIN H2 IOSTANDARD LVCMOS33 } [get_ports { led[4] }]; #IO_L15P_T2_DQS_35 Sch=ja[7]

#set_property -dict { PACKAGE_PIN G2 IOSTANDARD LVCMOS33 } [get_ports { led[5] }]; #IO_L15N_T2_DQS_35 Sch=ja[8]

#set_property -dict { PACKAGE_PIN C2 IOSTANDARD LVCMOS33 } [get_ports { led[6] }]; #IO_L16P_T2_35 Sch=ja[9]

#set_property -dict { PACKAGE_PIN C1 IOSTANDARD LVCMOS33 } [get_ports { led[7] }]; #IO_L16N_T2_35 Sch=ja[10]

### Pmod Header JB

#set_property -dict { PACKAGE_PIN C4 IOSTANDARD LVCMOS33 } [get_ports { sw_b[0] }]; #IO_L7P_T1_AD6P_35 Sch=jb[1]

#set_property -dict { PACKAGE_PIN B2 IOSTANDARD LVCMOS33 } [get_ports { sw_b[1] }]; #IO_L10N_T1_AD15N_35 Sch=jb[2]

#set_property -dict { PACKAGE_PIN B3 IOSTANDARD LVCMOS33 } [get_ports { sw_b[2] }]; #IO_L10P_T1_AD15P_35 Sch=jb[3]

#set_property -dict { PACKAGE_PIN B4 IOSTANDARD LVCMOS33 } [get_ports { sw_b[3] }]; #IO_L7N_T1_AD6N_35 Sch=jb[4]

#set_property -dict { PACKAGE_PIN B1 IOSTANDARD LVCMOS33 } [get_ports { sw_b[4] }]; #IO_L9P_T1_DQS_AD7P_35 Sch=jb[7]

#set_property -dict { PACKAGE_PIN A1 IOSTANDARD LVCMOS33 } [get_ports { sw_b[5] }]; #IO_L9N_T1_DQS_AD7N_35 Sch=jb[8]

#set_property -dict { PACKAGE_PIN A3 IOSTANDARD LVCMOS33 } [get_ports { sw_b[6] }]; #IO_L8N_T1_AD14N_35 Sch=jb[9]

#set_property -dict { PACKAGE_PIN A4 IOSTANDARD LVCMOS33 } [get_ports { sw_b[7] }]; #IO_L8P_T1_AD14P_35 Sch=jb[10]

### Pmod Header JC

#set_property -dict { PACKAGE_PIN C5 IOSTANDARD LVCMOS33 } [get_ports { sw_a[0] }]; #IO_L1N_T0_AD4N_35 Sch=jc[1]

#set_property -dict { PACKAGE_PIN C6 IOSTANDARD LVCMOS33 } [get_ports { sw_a[1] }]; #IO_L1P_T0_AD4P_35 Sch=jc[2]

#set_property -dict { PACKAGE_PIN B6 IOSTANDARD LVCMOS33 } [get_ports { sw_a[2] }]; #IO_L2N_T0_AD12N_35 Sch=jc[3]

#set_property -dict { PACKAGE_PIN C7 IOSTANDARD LVCMOS33 } [get_ports { sw_a[3] }]; #IO_L4N_T0_35 Sch=jc[4]

#set_property -dict { PACKAGE_PIN A5 IOSTANDARD LVCMOS33 } [get_ports { sw_a[4] }]; #IO_L3N_T0_DQS_AD5N_35 Sch=jc[7]

#set_property -dict { PACKAGE_PIN A6 IOSTANDARD LVCMOS33 } [get_ports { sw_a[5] }]; #IO_L3P_T0_DQS_AD5P_35 Sch=jc[8]

#set_property -dict { PACKAGE_PIN B7 IOSTANDARD LVCMOS33 } [get_ports { sw_a[6] }]; #IO_L2P_T0_AD12P_35 Sch=jc[9]

#set_property -dict { PACKAGE_PIN D8 IOSTANDARD LVCMOS33 } [get_ports { sw_a[7] }]; #IO_L4P_T0_35 Sch=jc[10]

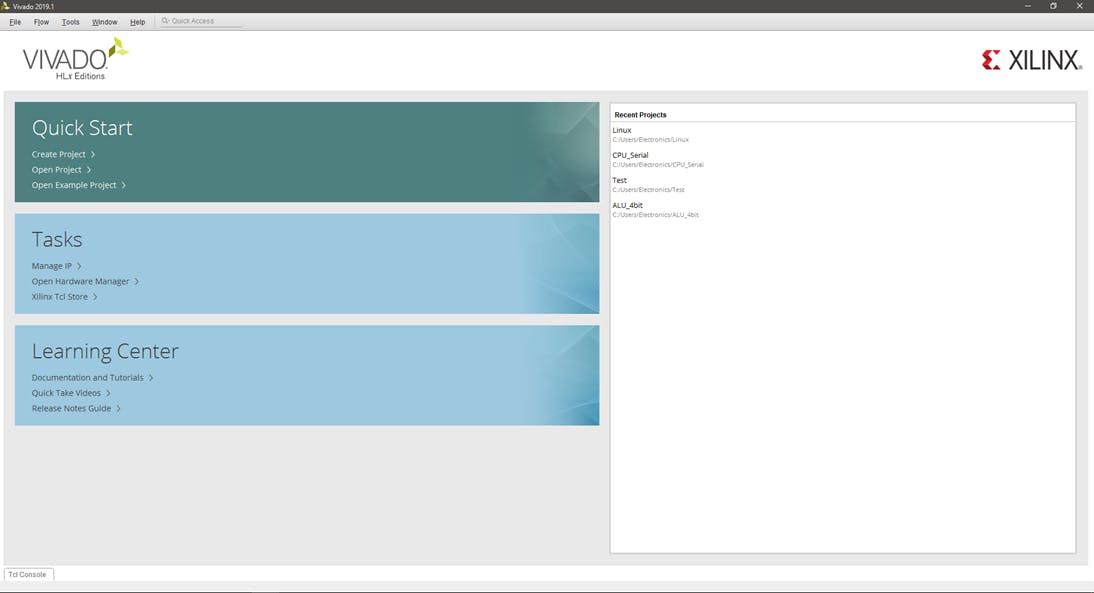

Vivado 入門:

如果您計劃使用 FPGA 板上的按鈕,請確保在移位寄存器項目的約束文件中添加命令,因為由于時鐘專用路由錯誤,實現將無法完成。

Artix-7 FPGA 上的 8 位移位寄存器:

Artix-7 FPGA 上的 8 位桶形移位器:

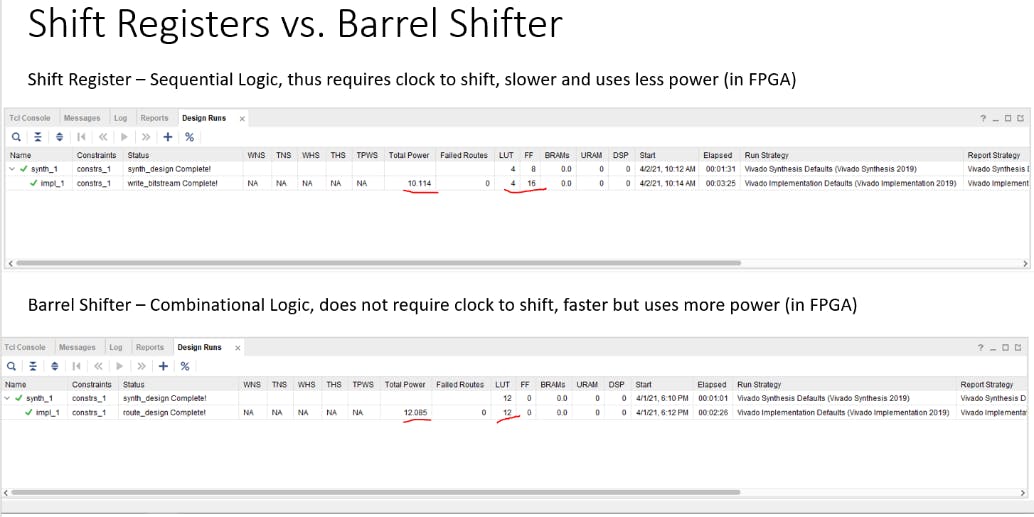

實施后的最終比較:

謝謝閱讀!

- XILINX ARTIX7系列FPGA芯片產品目錄 27次下載

- Artix-7 FPGA數據表下載 10次下載

- 使用Matlab實現組合邏輯電路的設計與仿真 23次下載

- FPGA時序邏輯和組合邏輯的入門基礎教程 12次下載

- Xilinx 7系列FPGA可配置邏輯塊的用戶指南 6次下載

- 組合邏輯電路和時序邏輯電路的學習課件免費下載 31次下載

- 組合邏輯電路的學習教程課件免費下載 15次下載

- XA ARTIX-7 FPGA的數據手冊免費下載 9次下載

- XA Artix-7 FPGA芯片的選型手冊免費下載 17次下載

- Multisim在組合邏輯電路設計中的常用元件和詳細作用分析 10次下載

- 組合邏輯設計實例_國外 24次下載

- 組合邏輯電路設計基礎 0次下載

- 組合邏輯電路電子教案 0次下載

- 組合邏輯電路設計實驗 0次下載

- 組合邏輯電路.ppt

- 組合邏輯電路之與或邏輯 1809次閱讀

- 組合邏輯電路和時序邏輯電路的區別和聯系 6856次閱讀

- 組合邏輯電路的分析和設計 4237次閱讀

- 組合邏輯生成的時鐘有哪些危害 4259次閱讀

- 什么是組合邏輯電路 如何使用verilog描述組合邏輯電路 5939次閱讀

- FPGA電路組合邏輯設計中的毛刺如何解決 3706次閱讀

- digilent Nexys 4:Artix-7 FPGA訓練板介紹 8408次閱讀

- xilinx7系列FPGA的7種邏輯代碼配置模式 3124次閱讀

- 采用Artix-7 XCA75T FPGA的高速多通道數字轉換器 2621次閱讀

- 組合邏輯電路和時序邏輯電路比較_組合邏輯電路和時序邏輯電路有什么區別 9.3w次閱讀

- 組合邏輯電路實驗原理 6.6w次閱讀

- 組合邏輯電路設計步驟詳解(教程) 12.2w次閱讀

- 組合邏輯電路的特點詳解 3.9w次閱讀

- FPGA中組合邏輯和時序邏輯的區別 8880次閱讀

- 什么是組合邏輯電路,組合邏輯電路的基本特點和種類詳解 7.5w次閱讀

下載排行

本周

- 1山景DSP芯片AP8248A2數據手冊

- 1.06 MB | 532次下載 | 免費

- 2RK3399完整板原理圖(支持平板,盒子VR)

- 3.28 MB | 339次下載 | 免費

- 3TC358743XBG評估板參考手冊

- 1.36 MB | 330次下載 | 免費

- 4DFM軟件使用教程

- 0.84 MB | 295次下載 | 免費

- 5元宇宙深度解析—未來的未來-風口還是泡沫

- 6.40 MB | 227次下載 | 免費

- 6迪文DGUS開發指南

- 31.67 MB | 194次下載 | 免費

- 7元宇宙底層硬件系列報告

- 13.42 MB | 182次下載 | 免費

- 8FP5207XR-G1中文應用手冊

- 1.09 MB | 178次下載 | 免費

本月

- 1OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 2555集成電路應用800例(新編版)

- 0.00 MB | 33566次下載 | 免費

- 3接口電路圖大全

- 未知 | 30323次下載 | 免費

- 4開關電源設計實例指南

- 未知 | 21549次下載 | 免費

- 5電氣工程師手冊免費下載(新編第二版pdf電子書)

- 0.00 MB | 15349次下載 | 免費

- 6數字電路基礎pdf(下載)

- 未知 | 13750次下載 | 免費

- 7電子制作實例集錦 下載

- 未知 | 8113次下載 | 免費

- 8《LED驅動電路設計》 溫德爾著

- 0.00 MB | 6656次下載 | 免費

總榜

- 1matlab軟件下載入口

- 未知 | 935054次下載 | 免費

- 2protel99se軟件下載(可英文版轉中文版)

- 78.1 MB | 537798次下載 | 免費

- 3MATLAB 7.1 下載 (含軟件介紹)

- 未知 | 420027次下載 | 免費

- 4OrCAD10.5下載OrCAD10.5中文版軟件

- 0.00 MB | 234315次下載 | 免費

- 5Altium DXP2002下載入口

- 未知 | 233046次下載 | 免費

- 6電路仿真軟件multisim 10.0免費下載

- 340992 | 191187次下載 | 免費

- 7十天學會AVR單片機與C語言視頻教程 下載

- 158M | 183279次下載 | 免費

- 8proe5.0野火版下載(中文版免費下載)

- 未知 | 138040次下載 | 免費

電子發燒友App

電子發燒友App

創作

創作 發文章

發文章 發帖

發帖  提問

提問  發資料

發資料 發視頻

發視頻 上傳資料賺積分

上傳資料賺積分

評論